BORA Xpress SOM/BORA Xpress Evaluation Kit/pdf

Contents

- 1 Getting started

- 2 Carrier board Design

- 2.1 Carrier board design guidelines

- 2.1.1 Basic guidelines

- 2.1.2 Power-up sequence

- 2.1.3 Interfaces Guidelines

- 2.1.3.1 Ethernet 10/100/1000

- 2.1.3.2 USB

- 2.1.3.3 HDMI

- 2.1.3.4 SATA

- 2.1.3.5 PCI Express

- 2.1.3.6 LVDS

- 2.1.3.7 LCD Interface

- 2.1.3.8 VIN Interface

- 2.1.3.9 TVOUT

- 2.1.3.10 I2C Interface

- 2.1.3.11 SD/MMC Interface

- 2.1.3.12 CAN Interface

- 2.1.4 Functional guidelines

- 2.1.5 Thermal Management

- 2.2 Integration guide

- 2.2.1 Advanced routing and carrier board design guidelines

- 2.1 Carrier board design guidelines

- 3 General Information

- 4 Interfaces and Connectors

- 4.1 Power Supply

- 4.2 Voltage selections

- 4.3 CPU connectors

- 4.4 FMC

- 4.5 JTAG

- 4.6 Ethernet

- 4.7 Console

- 4.8 SD

- 4.9 USB

- 4.10 LVDS

- 4.11 Touchscreen

- 4.12 CAN

- 4.13 RTC

- 4.14 Watchdog

- 4.15 DWM

- 4.16 PMOD

- 4.17 Pin strip

- 5 Electrical and Mechanical Documents

Getting started[edit | edit source]

Kit Identification Codes[edit | edit source]

The development kits (DESK, XELK, XUELK, BELK, etc.) are identified by a couple of codes:

- P/N Part Number identification code

- S/N Serial Number identification code

These codes are printed on a label sticked to the box containing the kit.

For example, the following picture shows such a label of an Axel Ultra XELK (XELK-H-S) with Serial Number 0CFA

These codes are required to complete the registration process of the kit.

Unboxing[edit | edit source]

Once you've received the kit, please open the box and check the kit contents with the packing list included in the box, using the table on this chapter as a reference.

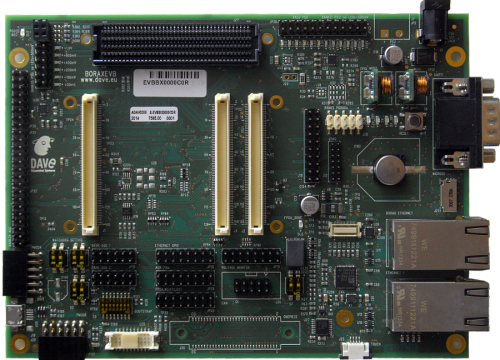

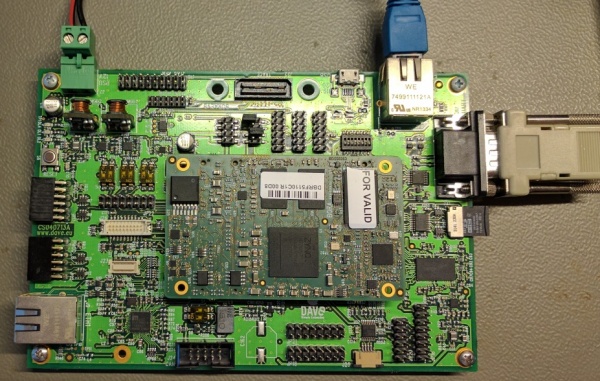

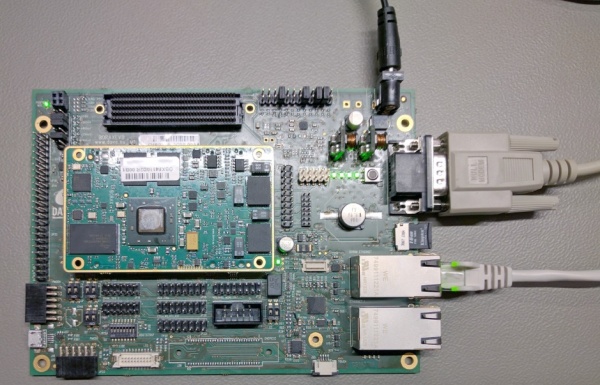

The hardware components (SOM, carrier boards and display) are pre-assembled, as shown in the picture below:

Kit Contents[edit | edit source]

The following table list the kit components:

| Component | Description | Notes |

|---|---|---|

BORA Xpress SOM (p/n DBXF4110S2R)

|

| |

| BORA Xpress Carrier board | ||

| AC/DC Single Output Wall Mount adapter Output: +12V – 2.0 A |

||

| microSDHC card | Already programmed with factory BSP version. Latest BSP SD card image can be found and programmed following this |

Order codes[edit | edit source]

| Order code | Description |

|---|---|

| BXELK-H-S | This code refers to the default configuration detailed above |

| BXELK-H-S-D | This variant is like BELK-L-S, except the SOM, which is DBXD4110S2R. |

microSD Layout[edit | edit source]

The microSD provided with the kit is used to store:

- a bootable partition (mmcblk0p1, vfat) containing:

- binary images (u-boot and kernel images)

- root file system partition (mmcblk0p2, ext4)

Kit contents[edit | edit source]

| Component | Description | Notes |

|---|---|---|

BORA Xpress SOM (p/n DBXF4110S2R)

|

| |

| BORA Xpress Carrier board | ||

| AC/DC Single Output Wall Mount adapter Output: +12V – 2.0 A |

||

|

microSDHC card with SD adapter and USB adapter |

Order codes[edit | edit source]

| Order code | Description |

|---|---|

| BXELK-H-S | This code refers to the default configuration detailed above |

| BXELK-H-S-D | This variant is like BELK-L-S, except the SOM, which is DBXD4110S2R. |

Target setup and first boot[edit | edit source]

This section describes how to quickly start Bora/BoraEVB and BoraX/BoraXEVB systems included in the BELK/BXELK:

- on target side, connect a null-modem cable on J17 DB9 connector, denoted also as UART1

- on host side, connect the other end of the null-modem cable to a COM port and start your favorite terminal software that will be used to interact with the target's serial console; communication parameters are 115200-8-N-1

- optionally connect the BoraEVB/BoraXEVB board to an Ethernet LAN by plugging cable into connector J8, also denoted as ETH0 on BoraEVB and BORAX ETHERNET on BoraXEVB

- connect 12V power supply to JP2 or J7 connector, also denoted as PSU 12V

- insert the microSD card in the slot J21, also denoted as MICROSD.

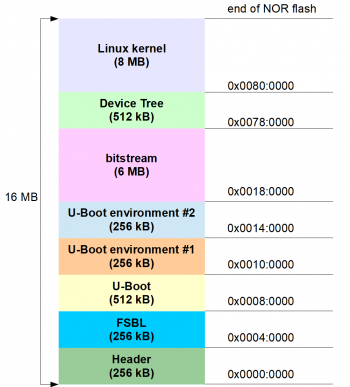

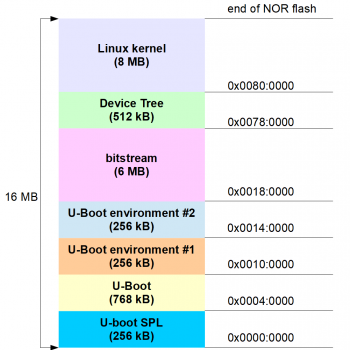

Once power has been applied to the target, FSBL or U-boot SPL and U-Boot bootloaders will be fetched from the SPI NOR flash that equips Bora/BoraX/BORA Lite SOM and executed. Boot messages will be printed out to the serial console. Redundant U-Boot environment is stored in the NOR flash as well, as depicted in the following image.

By default, U-Boot is configured to retrieve Linux kernel image stored in the microSD card [1]. In turn, Linux kernel shall mount root file system from the mmcblk0p2 partition of the microSD card itself [2], [3]. At the end of boot process, Linux shell shall be available on the serial console. Default boot process does not download any bitstream to the Programmable Logic.

The following dump shows the typical messages printed out to the console during bootstrap process. This log refers to Belk-4.0.0 running on BORA SOM. For BORAX SOM similar messages are printed out to the console.

U-Boot SPL 2017.01-belk-4.0.0 (Jul 11 2017 - 15:58:04)

qspi boot

Trying to boot from SPI

U-Boot 2017.01-belk-4.0.0 (Jul 11 2017 - 15:58:04 +0200), Build: jenkins-BELK_u-boot-10

Model: Bora

Board: Xilinx Zynq

I2C: ready

DRAM: ECC disabled 1 GiB

Relocating to 3ff2e000, new gd at 3eaedee8, sp at 3eaedec0

NAND: 1024 MiB

MMC: sdhci@e0100000: 0 (SD)

SF: Detected s25fl256s_64k with page size 256 Bytes, erase size 64 KiB, total 64 MiB

*** Warning - bad CRC, using default environment

In: serial@e0001000

Out: serial@e0001000

Err: serial@e0001000

Model: Bora

Board: Xilinx Zynq

SF: Detected s25fl256s_64k with page size 256 Bytes, erase size 64 KiB, total 64 MiB

SF: Detected s25fl256s_64k with page size 256 Bytes, erase size 64 KiB, total 64 MiB

SOM ConfigID#: 00000001

SOM UniqueID#: 01234567:89abcdef

ds2431_readmem(): error in chip reset

ds2431_readmem(): error in reading buffer

ds2431_readmem(): error in chip reset

ds2431_readmem(): error in reading buffer

CB ConfigID CRC mismatch for 0x00000000 (was 0x00000000, expected 0x2144df1c) at block 3 (offset 96): using default

CB ConfigID#: ffffffff

CB UniqueID#: 00000000:00000000

Net: ZYNQ GEM: e000b000, phyaddr 7, interface rgmii-id

eth0: ethernet@e000b000

Hit ENTER within 3 seconds to stop autoboot

starting USB...

USB0: USB EHCI 1.00

scanning bus 0 for devices... 1 USB Device(s) found

scanning usb for storage devices... 0 Storage Device(s) found

USB device 0: unknown device

** Bad device usb 0 **

switch to partitions #0, OK

mmc0 is current device

reading boot.scr

472 bytes read in 12 ms (38.1 KiB/s)

Running bootscript from mmc ...

## Executing script at 02080000

bootscript generated with command "mkimage -A ARM -T script -C none -n BELK -d bootscript.txt boot.scr"

reading uImage

3770880 bytes read in 642 ms (5.6 MiB/s)

reading bora.dtb

10647 bytes read in 19 ms (546.9 KiB/s)

Booting Bora/BoraX via mmc

## Error: "configid_fixup" not defined

## Booting kernel from Legacy Image at 02080000 ...

Image Name: Linux-4.9.0-belk-4.0.0-xilinx

Image Type: ARM Linux Kernel Image (uncompressed)

Data Size: 3770816 Bytes = 3.6 MiB

Load Address: 00008000

Entry Point: 00008000

Verifying Checksum ... OK

## Flattened Device Tree blob at 02000000

Booting using the fdt blob at 0x2000000

Loading Kernel Image ... OK

Loading Device Tree to 1effa000, end 1efff996 ... OK

Switching to NAND storage before starting Linux

Starting kernel ...

Uncompressing Linux... done, booting the kernel.

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.9.0-belk-4.0.0-xilinx (jenkins@linuxserver2) (gcc version 6.2.1 20161016 (Linaro GCC 6.2-2016.11) ) #1 SMP PREEMPT Sun Jul 9 23:10:22 CEST 2017

[ 0.000000] CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=18c5387d

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] OF: fdt:Machine model: Bora

[ 0.000000] bootconsole [earlycon0] enabled

[ 0.000000] cma: Reserved 16 MiB at 0x3f000000

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] On node 0 totalpages: 262144

[ 0.000000] free_area_init_node: node 0, pgdat c0a2d840, node_mem_map ef7f7000

[ 0.000000] Normal zone: 1536 pages used for memmap

[ 0.000000] Normal zone: 0 pages reserved

[ 0.000000] Normal zone: 196608 pages, LIFO batch:31

[ 0.000000] HighMem zone: 65536 pages, LIFO batch:15

[ 0.000000] percpu: Embedded 14 pages/cpu @ef7d1000 s26124 r8192 d23028 u57344

[ 0.000000] pcpu-alloc: s26124 r8192 d23028 u57344 alloc=14*4096

[ 0.000000] pcpu-alloc: [0] 0 [0] 1

[ 0.000000] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 260608

[ 0.000000] Kernel command line: root=/dev/mmcblk0p2 rootwait rw console=ttyPS0,115200n8 debug earlyprintk

[ 0.000000] PID hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.000000] Dentry cache hash table entries: 131072 (order: 7, 524288 bytes)

[ 0.000000] Inode-cache hash table entries: 65536 (order: 6, 262144 bytes)

[ 0.000000] Memory: 1013220K/1048576K available (6144K kernel code, 232K rwdata, 1512K rodata, 1024K init, 323K bss, 18972K reserved, 16384K cma-reserved, 245760K highmem)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 - 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

[ 0.000000] vmalloc : 0xf0800000 - 0xff800000 ( 240 MB)

[ 0.000000] lowmem : 0xc0000000 - 0xf0000000 ( 768 MB)

[ 0.000000] pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

[ 0.000000] modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

[ 0.000000] .text : 0xc0008000 - 0xc0700000 (7136 kB)

[ 0.000000] .init : 0xc0900000 - 0xc0a00000 (1024 kB)

[ 0.000000] .data : 0xc0a00000 - 0xc0a3a1a0 ( 233 kB)

[ 0.000000] .bss : 0xc0a3a1a0 - 0xc0a8afb4 ( 324 kB)

[ 0.000000] Preemptible hierarchical RCU implementation.

[ 0.000000] Build-time adjustment of leaf fanout to 32.

[ 0.000000] RCU restricting CPUs from NR_CPUS=4 to nr_cpu_ids=2.

[ 0.000000] RCU: Adjusting geometry for rcu_fanout_leaf=32, nr_cpu_ids=2

[ 0.000000] NR_IRQS:16 nr_irqs:16 16

[ 0.000000] efuse mapped to f0802000

[ 0.000000] slcr mapped to f0804000

[ 0.000000] L2C: platform modifies aux control register: 0x02060000 -> 0x02460000

[ 0.000000] L2C: DT/platform modifies aux control register: 0x02060000 -> 0x02460000

[ 0.000000] L2C-310 erratum 769419 enabled

[ 0.000000] L2C-310 enabling early BRESP for Cortex-A9

[ 0.000000] L2C-310 full line of zeros enabled for Cortex-A9

[ 0.000000] L2C-310 dynamic clock gating enabled, standby mode enabled

[ 0.000000] L2C-310 cache controller enabled, 8 ways, 512 kB

[ 0.000000] L2C-310: CACHE_ID 0x410000c8, AUX_CTRL 0x46460001

[ 0.000000] zynq_clock_init: clkc starts at f0804100

[ 0.000000] Zynq clock init

[ 0.000000] ps_clk frequency not specified, using 33 MHz.

[ 0.000012] sched_clock: 64 bits at 333MHz, resolution 3ns, wraps every 4398046511103ns

[ 0.007870] clocksource: arm_global_timer: mask: 0xffffffffffffffff max_cycles: 0x4ce07af025, max_idle_ns: 440795209040 ns

[ 0.018886] Switching to timer-based delay loop, resolution 3ns

[ 0.024887] clocksource: ttc_clocksource: mask: 0xffff max_cycles: 0xffff, max_idle_ns: 537538477 ns

[ 0.033937] timer #0 at f080c000, irq=17

[ 0.038252] Console: colour dummy device 80x30

[ 0.042581] Calibrating delay loop (skipped), value calculated using timer frequency.. 666.66 BogoMIPS (lpj=3333333)

[ 0.053061] pid_max: default: 32768 minimum: 301

[ 0.057843] Mount-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.064345] Mountpoint-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.071973] CPU: Testing write buffer coherency: ok

[ 0.076890] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.082484] Setting up static identity map for 0x100000 - 0x100058

[ 0.258340] CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

[ 0.258442] Brought up 2 CPUs

[ 0.266979] SMP: Total of 2 processors activated (1333.33 BogoMIPS).

[ 0.273360] CPU: All CPU(s) started in SVC mode.

[ 0.278941] devtmpfs: initialized

[ 0.285288] VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4

[ 0.293052] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.303669] pinctrl core: initialized pinctrl subsystem

[ 0.310015] NET: Registered protocol family 16

[ 0.316110] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.358364] cpuidle: using governor ladder

[ 0.398352] cpuidle: using governor menu

[ 0.414905] hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.

[ 0.422775] hw-breakpoint: maximum watchpoint size is 4 bytes.

[ 0.428739] zynq-ocm f800c000.ocmc: ZYNQ OCM pool: 256 KiB @ 0xf0880000

[ 0.435584] zynq-pinctrl 700.pinctrl: zynq pinctrl initialized

[ 0.455610] vgaarb: loaded

[ 0.458851] SCSI subsystem initialized

[ 0.462817] usbcore: registered new interface driver usbfs

[ 0.468276] usbcore: registered new interface driver hub

[ 0.473587] usbcore: registered new device driver usb

[ 0.479680] pps_core: LinuxPPS API ver. 1 registered

[ 0.484514] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.493700] PTP clock support registered

[ 0.499357] clocksource: Switched to clocksource arm_global_timer

[ 0.520290] NET: Registered protocol family 2

[ 0.525350] TCP established hash table entries: 8192 (order: 3, 32768 bytes)

[ 0.532409] TCP bind hash table entries: 8192 (order: 4, 65536 bytes)

[ 0.538840] TCP: Hash tables configured (established 8192 bind 8192)

[ 0.545202] UDP hash table entries: 512 (order: 2, 16384 bytes)

[ 0.551082] UDP-Lite hash table entries: 512 (order: 2, 16384 bytes)

[ 0.557542] NET: Registered protocol family 1

[ 0.562207] RPC: Registered named UNIX socket transport module.

[ 0.567985] RPC: Registered udp transport module.

[ 0.572752] RPC: Registered tcp transport module.

[ 0.577445] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.583922] PCI: CLS 0 bytes, default 64

[ 0.588414] hw perfevents: enabled with armv7_cortex_a9 PMU driver, 7 counters available

[ 0.598056] futex hash table entries: 512 (order: 3, 32768 bytes)

[ 0.604966] workingset: timestamp_bits=30 max_order=18 bucket_order=0

[ 0.612013] jffs2: version 2.2. (NAND) (SUMMARY) © 2001-2006 Red Hat, Inc.

[ 0.619910] bounce: pool size: 64 pages

[ 0.623630] io scheduler noop registered

[ 0.627583] io scheduler deadline registered

[ 0.631928] io scheduler cfq registered (default)

[ 0.639167] dma-pl330 f8003000.dmac: Loaded driver for PL330 DMAC-241330

[ 0.645763] dma-pl330 f8003000.dmac: DBUFF-128x8bytes Num_Chans-8 Num_Peri-4 Num_Events-16

[ 0.654861] e0000000.serial: ttyPS1 at MMIO 0xe0000000 (irq = 145, base_baud = 3125000) is a xuartps

[ 0.664307] e0001000.serial: ttyPS0 at MMIO 0xe0001000 (irq = 146, base_baud = 3125000) is a xuartps

à[ 0.673432] console [ttyPS0] enabled

[ 0.673432] console [ttyPS0] enabled

[ 0.680527] bootconsole [earlycon0] disabled

[ 0.680527] bootconsole [earlycon0] disabled

[ 0.689751] xdevcfg f8007000.devcfg: ioremap 0xf8007000 to f086f000

[ 0.696648] [drm] Initialized

[ 0.712609] brd: module loaded

[ 0.723100] loop: module loaded

[ 0.728406] libphy: Fixed MDIO Bus: probed

[ 0.735460] CAN device driver interface

[ 0.741807] libphy: MACB_mii_bus: probed

[ 0.840108] macb e000b000.ethernet eth0: Cadence GEM rev 0x00020118 at 0xe000b000 irq 148 (00:50:c2:1e:af:e0)

[ 0.849977] Micrel KSZ9031 Gigabit PHY e000b000.etherne:07: attached PHY driver [Micrel KSZ9031 Gigabit PHY] (mii_bus:phy_addr=e000b000.etherne:07, irq=-1)

[ 0.864140] e1000e: Intel(R) PRO/1000 Network Driver - 3.2.6-k

[ 0.869913] e1000e: Copyright(c) 1999 - 2015 Intel Corporation.

[ 0.876782] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 0.883279] ehci-pci: EHCI PCI platform driver

[ 0.887820] usbcore: registered new interface driver usb-storage

[ 0.894012] e0002000.usb supply vbus not found, using dummy regulator

[ 0.900703] ULPI transceiver vendor/product ID 0x0424/0x0006

[ 0.906275] Found SMSC USB331x ULPI transceiver.

[ 0.910910] ULPI integrity check: passed.

[ 0.916630] mousedev: PS/2 mouse device common for all mice

[ 0.922521] i2c /dev entries driver

[ 0.926190] cdns-i2c e0004000.i2c: 100 kHz mmio e0004000 irq 142

[ 0.933517] rtc-ds3232 0-0068: oscillator discontinuity flagged, time unreliable

[ 0.943182] rtc-ds3232 0-0068: rtc core: registered ds3232 as rtc0

[ 0.950800] ina2xx 0-0041: power monitor ina226 (Rshunt = 10000 uOhm)

[ 0.959126] Xilinx Zynq CpuIdle Driver started

[ 0.964011] sdhci: Secure Digital Host Controller Interface driver

[ 0.970180] sdhci: Copyright(c) Pierre Ossman

[ 0.974447] sdhci-pltfm: SDHCI platform and OF driver helper

[ 1.039420] mmc0: SDHCI controller on e0100000.sdhci [e0100000.sdhci] using DMA

[ 1.047063] usbcore: registered new interface driver usbhid

[ 1.053610] usbhid: USB HID core driver

[ 1.060557] nand: device found, Manufacturer ID: 0x01, Chip ID: 0xd3

[ 1.066828] nand: AMD/Spansion S34ML08G1

[ 1.070797] nand: 1024 MiB, SLC, erase size: 128 KiB, page size: 2048, OOB size: 64

[ 1.079104] Bad block table found at page 524224, version 0x01

[ 1.086183] Bad block table found at page 524160, version 0x01

[ 1.092800] 8 ofpart partitions found on MTD device pl35x-nand

[ 1.098568] Creating 8 MTD partitions on "pl35x-nand":

[ 1.103708] 0x000000000000-0x000000040000 : "nand-SPL"

[ 1.120695] 0x000000040000-0x000000100000 : "nand-uboot"

[ 1.137009] 0x000000100000-0x000000140000 : "nand-uboot-env1"

[ 1.153846] 0x000000140000-0x000000180000 : "nand-uboot-env2"

[ 1.160646] mmc0: new SDHC card at address 0001

[ 1.165619] mmcblk0: mmc0:0001 SD16G 14.6 GiB

[ 1.170685] 0x000000180000-0x000000780000 : "nand-bitstream"

[ 1.177693] 0x000000780000-0x000000800000 : "nand-device-tree"

[ 1.183599] mmcblk0: p1 p2

[ 1.194709] 0x000000800000-0x000001000000 : "nand-linux"

[ 1.211164] 0x000001000000-0x000020000000 : "nand-rootfs"

[ 1.232466] NET: Registered protocol family 17

[ 1.236842] can: controller area network core (rev 20120528 abi 9)

[ 1.243084] NET: Registered protocol family 29

[ 1.247450] can: raw protocol (rev 20120528)

[ 1.251720] can: broadcast manager protocol (rev 20161123 t)

[ 1.257345] can: netlink gateway (rev 20130117) max_hops=1

[ 1.263160] Registering SWP/SWPB emulation handler

[ 1.274219] rtc-ds3232 0-0068: hctosys: unable to read the hardware clock

[ 1.283162] EXT4-fs (mmcblk0p2): mounting ext3 file system using the ext4 subsystem

[ 1.592447] random: fast init done

[ 1.748727] EXT4-fs (mmcblk0p2): recovery complete

[ 1.756780] EXT4-fs (mmcblk0p2): mounted filesystem with ordered data mode. Opts: (null)

[ 1.764840] VFS: Mounted root (ext3 filesystem) on device 179:2.

[ 1.775504] devtmpfs: mounted

[ 1.781627] Freeing unused kernel memory: 1024K (c0900000 - c0a00000)

INIT: version 2.88 booting

Starting udev

[ 2.706500] udevd[702]: starting version 3.2

[ 2.771034] udevd[703]: starting eudev-3.2

[ 2.915949] EXT4-fs (mmcblk0p2): re-mounted. Opts: (null)

Mon Jul 3 00:01:52 UTC 2017

INIT: Entering runlevel: 5

Configuring network interfaces... udhcpc (v1.24.1) started

Sending discover...

Sending discover...

Sending discover...

No lease, forking to background

done.

Starting system message bus: dbus.

Starting Dropbear SSH server: dropbear.

Starting rpcbind daemon...done.

starting statd: done

exportfs: can't open /etc/exports for reading

NFS daemon support not enabled in kernel

Starting syslogd/klogd: done

Starting internet superserver: xinetd.

* Starting Avahi mDNS/DNS-SD Daemon: avahi-daemon

...done.

Starting tcf-agent: OK

Poky (Yocto Project Reference Distro) 2.2.1 bora /dev/ttyPS0

bora login:

[1] bootscript is used to do this task.

[2] This root file system has been generated by Yocto build system.

[3] The microSD card is bootable itself, as explained here.

Target configuration for the development stage (net_nfs)[edit | edit source]

|

The default BELK/BXELK Virtual Machine network configuration is using NAT: this allows to accessing external network (i.e. Internet) using the host computer's networking connection.

For software development using |

During the development stage, the target is usually connected via Ethernet LAN to the host machine and is configured to:

- retrieve binary images (i.e. Linux kernel) via TFTP protocol

- mount the development root file system via NFS protocol. This root file system is physically in the file system of the host machine as depicted here. An example of Bridge mode configuration can be found here

In DAVE Embedded Systems development kits, this configuration is generally denoted as net_nfs. U-Boot bootloader supports this configuration. Some U-Boot environment variables are needed to set it up.

For more information about how to set up and use TFTP and NFS servers, please refer to the following link Booting the system via nfs.

microSD layout[edit | edit source]

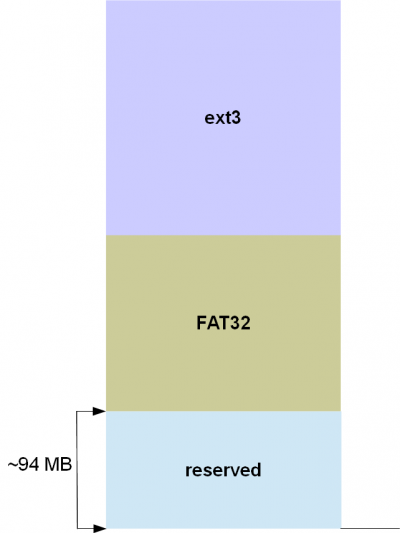

The microSD card provided with BELK/BXELK is partitioned as shown in the following image:

Most of storage space is occupied by two partitions:

- a

FAT32partition (mmcblk0p1) containing:- For BELK <= 3.0.2 and BXELK <= 1.0.1 :

boot.binboot image (containing FSBL, FPGA Bitstream an U-boot binaries)- U-Boot

boot.scrbootscript - Linux kernel and DTB binary images

- For BELK 4.0.0 or newer and BXELK 2.0.0 or newer:

boot.binu-boot SPL imagefpga.bitoptional FPGA bitstreamu-boot.imgu-boot image- U-Boot

boot.scrbootscript - Linux kernel and DTB binary images

- MVM image in OVA format

- For BELK <= 3.0.2 and BXELK <= 1.0.1 :

- an

ext3partition (mmcblk0p2) containing the root file system for the target.

bootscript and root file system are used to boot the target as described in this section.

It is worth remembering that the microSD card is bootable and U-Boot environment is retrieved from (and stored to with saveenv) into the FAT partition as bora.env

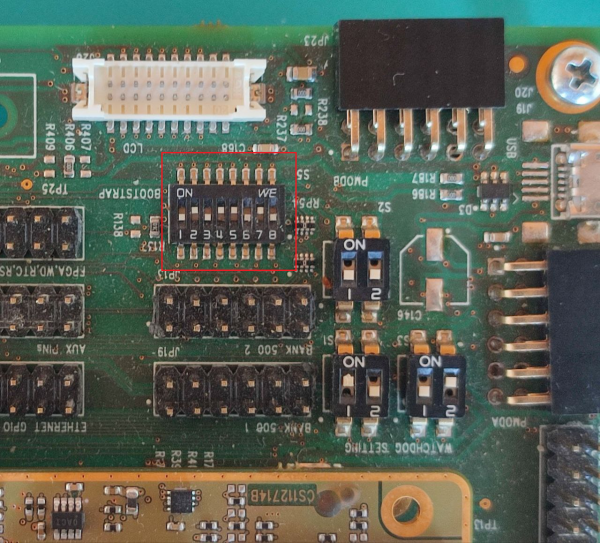

Boot mode selection - S5[edit | edit source]

S5 is a dip-switch for the boot mode selection. The following table reports the available options and the related configurations:

| S5.1 | S5.2 | S5.3 | S5.4 | S5.5 | S5.6 | S5.7 | S5.8 | |

|---|---|---|---|---|---|---|---|---|

| SPI-NOR | OFF | ON | OFF | ON | ON | ON | ON | OFF |

| SD-card | OFF | ON | OFF | ON | ON | OFF | ON | OFF |

| NAND (*) | OFF | ON | OFF | ON | ON | OFF | ON | ON |

| JTAG | OFF | ON | OFF | ON | ON | ON | ON | ON |

(*) Boot mode from NAND in supported ONLY on BORA Lite SOM module

Reset Button[edit | edit source]

Reset button - S6[edit | edit source]

S6 is the hardware reset button connected to the MRSTn signal (J2.16 SOM connector)

Carrier board Design[edit | edit source]

| History | |||

|---|---|---|---|

| Issue Date | Notes | ||

| 2021/11/22 | New documentation layout | ||

Carrier board design guidelines[edit | edit source]

This page provides useful information and resources to system designers in order to design carrier boards hosting DAVE Embedded Systems system-on-modules (SOM).

These guidelines are provided with the goal to help designers to design compliant systems with DAVE Embedded Systems modules and they cover schematics and PCB aspects. They apply to several products that are listed on the top right corner of this page (see "Applies to" boxes).

Basic guidelines[edit | edit source]

In this section basic hardware guidelines valid for all DAVE Embedded Systems SOMs are detailed.

Schematics[edit | edit source]

- Check mirroring and pinout of DAVE Embedded Systems system-on-modules (SOM) connector

- Properly decouple DAVE Embedded Systems system-on-modules (SOM) power supply with large bulk capacitor and small bypass capacitor

- Use low-ESR X7R capacitor if possible

- Check for correct connection of TX and RX lines

- Add series resistors as interface needs (see interface details)

PCB[edit | edit source]

PCB Tecnology[edit | edit source]

Use a PCB technology as advised in the following table

| Parameter | Min | Typ | Max |

| Layers(number) | 4 | 6 | - |

| Power Plane Layers | 2 | 4 | - |

| Clearence(mils) | - | 6 | - |

| Trace Width(mils) | - | 6 | - |

| Vias hole (mechanical) | 0,3 | - | |

| Minimum number of via for each power signal layer changes | 2 | 3 | - |

| Minimum number of via for each power signal SOM connector pin | 1 | 2 | - |

| Component package size | - | 0603 | - |

| PCB Height(mm) | 1,4 | 1,6 | - |

- If vias smaller than minimum advised size are used, take care to maintain an adeguate number of via when you change layer for each power signal.

- PCB heights less than minimum advised can produce PCB heating and mechanical issues

PCB Basics Guidelines[edit | edit source]

- Avoid stubs

- Isolate clock and HI-SPEED signal (see interface specifications for further details)

- Avoid voids on planes

- Use Solid Connection for on plane vias

- Place bulk and ByPass capacitor near DAVE Embedded Systems system-on-modules (SOM) power supply pins

- Place series terminator resistor near the related transmitter

SOM Connectors[edit | edit source]

This section provides information and suggestions regarding the SOM mating connectors.

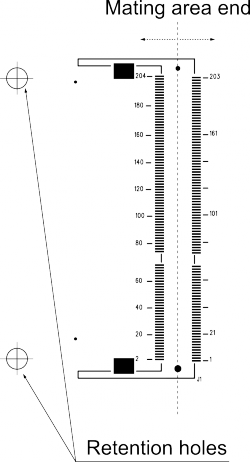

SO-DIMM[edit | edit source]

SO-DIMM mating connectors from different vendors may have slight differences in mechanical characteristics. One critical point is the position of the end of the mating area (please see the picture below), that can be slightly shifted inwards or outwards in respect to the retention holes on the carrier board. This can lead to a misalignment with the holes on the SO-DIMM modules, making difficult or impossible to insert the retentions screws or locking supports.

If you plan to use the holes as additional retention system, we recommend to pay attention to the mechanical characteristics when evaluating the SO-DIMM mating connectors to be mounted on the carrier board.

Power-up sequence[edit | edit source]

In order to prevent back powering effects, DAVE Embedded Systems' SOMs provide the signals required to handle power-up sequence properly. For instance, see the recommended sequence for the BORA SOM here.

In case the power-up sequence is not managed properly, the circuitry populating the SOM may be damaged.

Interfaces Guidelines[edit | edit source]

This section provides guidelines for the most used interfaces on DAVE Embedded Systems SOMs module.

Please refer to SOM's detailed pages for specific additional information.

Ethernet 10/100/1000[edit | edit source]

Case #1: PHY is integrated on SOM[edit | edit source]

This section refers to the case of PHY integrated on SOM such as Lizard and MAYA.

Schematics[edit | edit source]

- If LAN connector with integrated magnetic is used:

- predispose ethernet protection diodes on ethernet lines

- Connect connector shield to an adeguate GND or shield Plane

PCB[edit | edit source]

Refer to this table for 10/100 differential pairs routing

| Parameter for 10/100 differential pair | Min | Typ | Max |

| Differential Impedance(ohm) | - | 100 | - |

| Common Mode Impedance | - | 50 | - |

| Gap than TX and RX signals | 2xgap | 2xgap | - |

| Gap than other signals | 2xgap | 4xgap | - |

| Intra pair matching(mils)* | 0 | 25 | 150 |

| TX and RX via # mismatch* | 0 | 0 | 1 |

Refer to this table for Gigabit differential pairs routing

| Parameter for Gigabit Differential Pairs | Min | Typ | Max |

| Differential Impedance(ohm) | - | 100 | - |

| Common Mode Impedance | - | 50 | - |

| Gap than TX and RX signals | 2xgap | 2xgap | - |

| Gap than other signals | 2xgap | 4xgap | - |

| Intra pair matching(mils)* | 0 | 10 | 10 |

| Max PCB trace length | 3" | 5" | - |

| TX and RX via # mismatch* | 0 | 0 | 1 |

* Not mandatory but recommended.

- If LAN connector with integrated magnetic is used:

- do not route traces under the connettor, neither on opposite side

- place filter diode near connector

- place others signals far from connector

- Connect connector shield to an adeguate GND or shield Plane or Copper through numerous vias

- If on board magnetic are used

- adeguately isolate system GND from magnetic connector side

- Connect connector shield to an adeguate GND or shield Plane or Copper through numerous vias if necessary

- try to match as best as possible each differential pair (intrapair matching)

- Keep as best as possibile the same route for TX and RX traces

- If less than minimum gap is used, use a GND trace for improve trace separation

Case #2: PHY is not integrated on SOM and a RGMII PHY is used[edit | edit source]

This section refers to the case of:

- PHY not integrated on SOM

- Gigabit PHY populated on carrier board and connected to SOM through RGMII interface.

This solution is implemented on NaonEVB-Mid for example.

Schematics[edit | edit source]

- Add series resistors (RPACK resistors recommended) to RGMII lines

- Properly decouple PHY Power Supplies rails

- Properly decouple every supply pin of Ethernet PHY

- Properly separate analog Supply Rails

PCB[edit | edit source]

| Parameter for RGMII interface | Min | Typ | Max |

| Common mode impedance(ohm) | - | 50 | - |

| Gap than other ethernet diff pair | 4xwidth | - | - |

| Gap than other signals | 4xwidth | - | |

| Matching(mils) | - | - | 200 |

| Via Mismatch | 0 | 0 | 1 |

| Parameter for Gigabit Differential Pairs | Min | Typ | Max |

| Differential Impedance(ohm) | - | 100 | - |

| Common Mode Impedance | - | 50 | - |

| Gap than TX and RX signals | 2xgap | 2xgap | - |

| Gap than other signals | 2xgap | 4xgap | - |

| Intra pair matching(mils) | 0 | 10 | 10 |

| Max PCB trace length | 3" | 5" | - |

| TX and RX via # mismatch* | 0 | 0 | 1 |

* Not mandatory but recommended.

- Ground and VCC planes must be as large as possible

- Avoid plane split and voids

- Place bypass capacitor near every PHY supply pin

- Connect every capacitor's pin to the plane with at least 2 vias and the shortest trace pattern

- Place PHY device at least 1" (25mm) distance far away from connector

- Keep MDIO clock signal isolated from other signals

Case #3: PHY is not integrated on SOM and a RMII PHY is used[edit | edit source]

This section refers to the case of

- PHY not integrated on SOM

- 10/100 Ethernet PHY populate don carrier board and interfaced to SOM through RMII interface.

This solution is implemented for example in MayaEVB-Lite board.

Schematics[edit | edit source]

- If possible, place series resistor to RMII interface signals

- Properly decouple PHY Power Supplies rails

- Properly separate analog Supply Rails

- Properly decouple every supply pin of Ethernet PHY

- Use a standard RMII PHY that supports correct clock mode (see SOM specification for further details)

PCB[edit | edit source]

| Parameter for RMII interface | Min | Typ | Max |

| Reccomended Common mode impedance(ohm) | - | 50 | - |

| Gap between other signal | 2xW | - |

- Since RMII signals are not critical such as RGMII, is not necessary a strong matching between signal

- Avoid use of long traces

- Avoid stubs

- Keep as best as possibile the same routing for all RMII traces

| Parameter for Ethernet Differential Pairs | Min | Typ | Max |

| Differential Impedance(ohm) | - | 100 | - |

| Common Mode Impedance | - | 50 | - |

| Gap than other TX and RX signals | 2xgap | 2xgap | - |

| Gap than other signals | 2xgap | 4xgap | - |

| Intra pair matching(mils)* | 0 | 25 | 150 |

| TX and RX via # mismatch* | 0 | 0 | 1 |

* Not mandatory but recommended.

- Ground and VCC planes must be as large as possible

- Avoid plane split and voids

- Place bypass capacitor near every PHY supply pin

- Connect every capacitor's pin to the plane with at least 2 vias and the shortest trace pattern

- Place PHY device at least 1" (25mm) distance far away connector

- Keep MDIO clock signal isolated from other signals

USB[edit | edit source]

Schematics[edit | edit source]

- Create schematic in accordance with DAVE Embedded Systems system-on-modules (SOM) USB specification ( see SOM detailed pages )

PCB[edit | edit source]

| Parameter for USB Differential Pairs | Min | Typ | Max |

| Differential Impedance(ohm) | 80 | 90 | 100 |

| Common Mode Impedance | 40,5 | 45 | 49.5 |

| Gap than other signals | 3xgap | 5xgap | - |

| Intra pair matching(mils) | 0 | 25 | 150 |

| Max allowed stubs | - | - | 0 |

| Max traces length | - | - | note 1 |

| Max allowed plane split under traces | - | - | 0 |

note 1 see SOM detailed specifications

- If a stub is unavoidable in the design, no stub should be greater than 200 mils.

- Place a continuos reference plane underneath differential pair

HDMI[edit | edit source]

Schematics[edit | edit source]

- Add a Transmitter Port Protection to HDMI lines

- Use certified HDMI connector

- Connector shield must be properly connected

PCB[edit | edit source]

| Parameter for HDMI Differential Pairs | Min | Typ | Max |

| Differential Impedance(ohm) | 85 | 100 | 115 |

| Gap than other signals | 3xgap | 5xgap | - |

| Intra pair matching(mils) at 225MHz clock | 0 | 20 | 250 |

| Inter pair matching(mils) at 225MHz clock | 0 | 250 | 1" |

| Max allowed stubs | - | - | 0 |

| Max allowed plane split under traces | - | - | 0 |

- Place a continuos reference plane underneath differential pair

- Try to match lines as best as possible

SATA[edit | edit source]

Schematics[edit | edit source]

- Use certified SATA connector

PCB[edit | edit source]

| Parameter for SATA Differential Pairs | Min | Typ | Max |

| Differential Impedance(ohm) | 80 | 100 | 120 |

| Common Mode Impedance(ohm) | 51 | 60 | 69 |

| Gap than other signals | 2xgap | - | - |

| Intra pair matching(mils | - | - | note 1 |

| Inter pair matching(mils) | - | - | note 1 |

| Max allowed stubs | - | - | 0 |

| Max allowed plane split under traces | - | - | 0 |

| Max allowed length | - | - | note 1 |

note 1 see SOM detailed specifications

- Place a continuos reference plane underneath differential pair

- Minimized vias use

- No strong matching required between TX and RX, but keep same route for every differential pair

PCI Express[edit | edit source]

PCB[edit | edit source]

| Parameter for PCI Express Differential Pairs | Min | Typ | Max |

| Differential Impedance [Ohm] | - | 100 | - |

| Common Mode Impedance [Ohm] | - | 60 | - |

| Gap than other signals (reccomended) | - | 2xgap | - |

| Intra pair matching [mils]* | - | - | 10 |

| Max Total Length [in]* | - | - | 12 |

| Maximum allowed stub | - | - | 0 |

| Max allowed vias | - | - | 6 |

- * Including SoM trace length

- Preferred underneath plane over entire trace length GND.

LVDS[edit | edit source]

PCB[edit | edit source]

| Parameter for LVDS Differential Pairs | Min | Typ | Max |

| Differential Impedance [Ohm] | 85 | 100 | 115 |

| Common Mode Impedance [Ohm] | 46.75 | 55 | 63.25 |

| Gap than other signals (reccomended) | - | 2xgap | - |

| Intra pair skew [mils]* | - | - | 5 |

| Inter pair skew [mils]** | - | 400 | - |

| Maximum allowed stub | - | - | 0 |

- Prefer to route traces on TOP layer, referring them to a continuos GND plane.

- * Not includes SOM's length.

- ** Typical value can be relaxed depending on LVDS clock frequency

LCD Interface[edit | edit source]

Schematics[edit | edit source]

- Please refer to DAVE Embedded Systems system-on-modules (SOM) carrier board documentationfor further information

- Predispose series resistor terminator (RPACK for LCD data and single resistor for Clock and H-SYNC and V-SYNC)

- Series resistor value may vary depending by PCB and schematic

PCB[edit | edit source]

- If possible, use 50ohm common mode lines

- Match LCD parallel signals in accordance with Pixel Clock frequency (further details in SOM specifications)

- Avoid use of long traces connection (max 10" on PCB)

- Avoid stubs

VIN Interface[edit | edit source]

Schematics[edit | edit source]

- Please refer to DAVE Embedded Systems system-on-modules (SOM) carrier board documentation for further information

- Predispose series resistor terminator (RPACK for LCD data and single resistor for Clock and H-SYNC and V-SYNC)

- Series resistor value may vary depending PCB and schematic

PCB[edit | edit source]

- If possible, use 50ohm common mode lines

- Match VIN parallel signals in accordance with Pixel Clock frequency (further details in SOM specifications)

- Avoid use of long traces connection (max 10" on PCB)

- Avoid stubs

TVOUT[edit | edit source]

Schematics[edit | edit source]

- Please refer to DAVE Embedded Systems system-on-modules (SOM) carrier board documentation for further information

PCB[edit | edit source]

| Parameter for SATA Differential Pairs | Min | Typ | Max |

| Common Mode Impedance(ohm) | - | 75 | - |

| Gap than other signals | 2xwidth | - | - |

- Keep analog TVOUT signal far from noise signals

I2C Interface[edit | edit source]

Schematics[edit | edit source]

- Predispose properly pullup resistors on line in accordance with DAVE Embedded Systems system-on-modules (SOM)

- Do not overload I2C lines with too much devices

- Ensure that I2C devices are being properly initialized during power up

PCB[edit | edit source]

- Isolate I2C clock from noise sensitive signals

- Avoid stub

SD/MMC Interface[edit | edit source]

| Min | Typ | Max | |

| Common Mode impedance SOM(ohm) | - | 50 | 60 |

| Matching required* | - | - | - |

| Max allowed parallel routing(mils) | - | - | 1000 |

| Max trace Length** | - | - | - |

| Max # of vias allowed | - | - | - |

*This is not mandatory, however it is suggested in case trace length exceeds 10cm

**Overall trace length - i.e. Bora + carrier board - should not exceed 10cm. If this is not possible, try to avoid parallel routing in order to reduce crosstalk, and refer them to a ground plane.

CAN Interface[edit | edit source]

| Min | Typ | Max | |

| Differential Mode impedance(ohm) | 108 | 120 | 132 |

| Matching required | - | - | - |

| Min Interpair spacing | - | 4xgap | - |

| Max allowed parallel routing(mils) | - | - | - |

| Max trace Length | - | - | - |

| Max via allowed | - | - | - |

Functional guidelines[edit | edit source]

Sudden power off management[edit | edit source]

From the architectural standpoint, modern embedded systems often resemble traditional PCs. For example:

- they implement a rich set of I/O interfaces (large displays, Ethernet ports, USB ports, SDIO sockets etc.)

- they likely run complex operating systems that derive from desktop world (linux, Android, Windows CE etc.)

- they implement complex storage schemes (raw NAND, SSD, eMMC etc.).

One of the main difference between such systems and PCs is that the formers are - if appropriately designed - inherently resilient to sudden power fails. In any case, system designer should take into account these events and decide if and how manage them explicitly. Here are some typical techniques used to deal with this situation:

- in case the system is used by human operators, the use of clean shutdown - triggered by the user himself - should be encouraged to prevent sudden power off. Technically speaking, this can be done via GUI (soft button) or mechanical device (push buttons and alike). In the latter case, push button controllers such as Linear LTC2954 can be very useful to implement this feature

- in case no human operators interact with the system, more complex solutions might be required. This strategy is strongly dependent on hardware characteristics of SOM and must be approached on a case-by-case basis.

Thermal Management[edit | edit source]

Heat is generated by all semiconductors while operating and it is dissipated into the surrounding environment. This amount of heat is a function of the power consumed and the thermal resistance of the device package. Every silicon device on an electronic board must work within the limits of its operating temperature parameters (eg, the junction temperature) as specified by the silicon vendor.

Failure to maintain the temperature within safe ranges reduces operating lifetime, reliability, and performances and may cause irreversible damage to the system. Therefore, the product design cycle should include thermal analysis to verify that the device works within its functional limits. If the temperature is too high, component or system-level thermal enhancements are required to dissipate the heat from the system.

For detailed information, please refer to the following documents:

Integration guide[edit | edit source]

This page provides useful information and resources to system designers in order to integrate Bora SoMs in his/her application quickly. These information complement SoM-independent recommendations provided in the Carrier board design guidelines (SOM) page.

Several topics are covered, ranging from hardware issues to manufacturing aspects.

Advanced routing and carrier board design guidelines[edit | edit source]

Generally speaking, when designing a system-on-module (SoM) product it is impossible to know in advance the combination of interfaces and functionalities that will be implemented by the system integrator. This is even more true in case of Bora, due to the unprecedented flexibility and versatility of Zynq architecture. For this reason, Bora implements advanced routing schemes that, in combination with proper carrier board design, allow the implementation of high-speed complex interfaces that satisfy signal integrity requirements.

This chapter describes in detail such schemes and provides carrier board design guidelines accordingly.

In the following section the terms "Inter-pair matching" and "Intra-pair matching" are used. They indicate respectively:

- length matching among pairs belonging to the same class or group

- length matching between traces belonging to the same pair.

Suggested PCB specifications[edit | edit source]

| Min. | Typ. | |

| Layers(number) | 4 | 6 |

| GND Plane Layers | 1 | 2 |

| Power Plane Layers | 1 | 1 |

| Vias hole (mechanical)* [mm] | 0.3 | - |

*Smaller holes are deprecated because their limited current capacity and heat dissipation.

Power rails[edit | edit source]

Following power rails should be kept as short as possible and should be sized in order to minimize IR drop at maximum estimated current.

| Max estimated current | Required plane or copper areas | |

| 3.3V_SOM | application dependent | YES |

| VDDIO_BANK35 | application dependent | NO |

| VDDIO_BANK13 | application dependent | NO |

Main SD/MMC interface[edit | edit source]

Signals: PS_MIO40_501, PS_MIO41_501, PS_MIO42_501, PS_MIO43_501, PS_MIO44_501, PS_MIO45_501.

Following table details routing rules implemented on Bora SoM.

| Value | UOM | |

| Common Mode impedance | 50 | Ohm |

| Maximum Length Tolerance | 200 | mils |

Main Gigabit Ethernet interface (ETH0)[edit | edit source]

Signals: ETH_TXRX0_P/ETH_TXRX0_M, ETH_TXRX1_P/ETH_TXRX1_M, ETH_TXRX2_P/ETH_TXRX2_M, ETH_TXRX3_P/ETH_TXRX3_M.

Following table details routing rules implemented on Bora SoM.

| Value | UOM | |

| Common Mode impedance SOM | 55 | Ohm |

| Differential Mode impedance SOM | 100 | Ohm |

| Maximum Length Tolerance on SOM(intrapair) | 10 | mils |

| Maximum Length Tolerance on SOM(interpair) | 400 | mils |

CAN interface[edit | edit source]

Signals: CAN_H/CAN_L.

Following table details routing rules implemented on Bora SoM.

| Value | UOM | |

| Common Mode impedance SOM | - | Ohm |

| Differential Mode impedance SOM | 110 | Ohm |

| Maximum Length Tolerance on SOM(intrapair) | - | mils |

| Maximum Length Tolerance on SOM(interpair) | - | mils |

XADC interface[edit | edit source]

Signals XADC_VP_R/XADC_VN_R (dedicated analog inputs).

Following table details routing rules implemented on Bora SoM.

| Value | UOM | |

| Differential Mode impedance typ | 100 | Ohm |

| Maximum Length Tolerance on SOM(intrapair) | - | mils |

| Maximum Length Tolerance on SOM(interpair) | - | mils |

| Intrapair Matching required | 10 |

Connecting the PUDC_B pin[edit | edit source]

On Bora SOM, PUDC_B pin is (J2 connector, pin 15) connected to VDDIO_BANK34 (3.3V) via 10K resistor, thus internal pull-up resistors are disabled on each SelectIO pin, until FPGA configuration completes.

Default behavior can be changed by appropriate circuitry at carrier board level to set it to logical 0.

PS' I²C buses[edit | edit source]

Xilinx released an important Answer Record related to Zynq PS I2C Controller on 19th September 2014 (http://www.xilinx.com/support/answers/61861.html), a long period after Bora public lunch.

A technical and functional assessment has been performed to find out the best solution to cope with this issue on Bora based systems (1). Bora SoM is conceived to address a wide range of different application environments that are by definition unknown at design stage. Therefore it is virtually impossible to find a one-size-fits-all solution that does not limit somehow Bora functionalities and is backward compatible. The followed approach has aimed to preserve:

- system reliability

- backward compatibility

- system designer's freedom to choose the appropriate solution for his/her specific application.

Thanks to the Bora's I2C0 topology, Bora has undergone no changes to satisfy these requirements. The SoM in fact allows for:

- implementing, at carrier board level, complex glitch filtering strategies such as the one suggested by Xilinx AR# 61861

- avoiding waste of resources of PL if not strictly necessary (for instance when I2C0 functionality is not required at all).

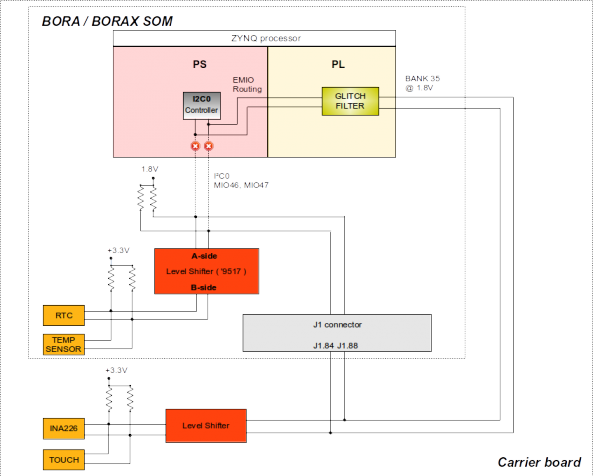

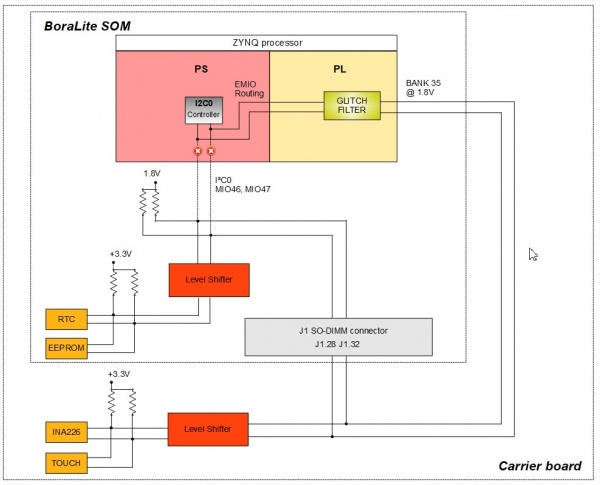

The configuration depicted by the following figure shows in principle a solution integrating the workaround suggested by Xilinx AR# 61861:

- PS I2C0 controller's signals are routed to PL via EMIO routing

- MIO46/47 are disabled

- glitch filter is digitally implemented in PL

- I2C0 SDA and SCL lines are physically connected to PL at carrier board level.

(1) What here described refers to I2C0 controller that by default is routed on pins MIO46 and MIO47.

How to implement workaround suggested by Xilinx on BoraEVB[edit | edit source]

Plase note that the reference project with I2C glitch filter implemented in FPGA is available on request. Plase contact helpdesk@dave.eu

This project, built with Vivado 2014.4, is based on the default project for BELK (BORA rev.B and BORAevb rev.A).

Here we have changed I2C0 signals routing to EMIO pins through FPGA, implementing the I2C glitch filter with VHDL example code provided in Xilinx AR# 61861. The MIO46-MIO47 is then configured as input GPIO. This is accomplished from the FSBL generated within the provided project.

I2C interface is routed through FPGA to pins on BANK35:

- I2C SCL => IO_L9P_T1_DQS_AD3P_35

- I2C SDA => IO_L9N_T1_DQS_AD3N_35

The BANK35 MUST be powered at 1.8V

Test on BoraEVB[edit | edit source]

To test the solution, please make these connections on BORAevb rev.A:

- 1.8V supply for BANK35 : (J11.2 to J11.7)

- I2C SCL : JP10.14 to JP21.5

- I2C SDA : JP10.16 to JP21.3

Test on BoraXEVB[edit | edit source]

To test the solution, please make these connections on BoraXEVB:

- 1.8V supply for BANK35 : please refer to VDDIO_BANK35 possibility on BoraXEVB schematics

- populate RPACK RP87

- I2C SCL : JP30.9 to JP29.5

- I2C SDA : JP30.11 to JP29.3

Programmable logic (PL)[edit | edit source]

For Bora SOM please refer to the following links:

For BoraX SOM please refer to the page.

For BoraLite SOM please refer to the page.

Traces length matching[edit | edit source]

A spreadsheet is available for download here, containing detailed information about signals routing. These information can be used to check nets matching of the overall system (carrier board + SOM).

For Bora/BoraEVB systems: File:Bora-routing.zip.

For BoraX/BoraXEVB systems: File:BoraX-BoraXEVB-combined-routing.zip.

For BoraLite/BoraXEVB systems: the presence of the Bora Lite adapter does not make sense to provide the routing information. Please refer to the Programmable logic page about information on internal BORA Lite routing. Please take carefully into account the design of the Carrier board considering every information related to the SO-DIMM socket and the tracenet on the Carrier

General Information[edit | edit source]

Product Highlights[edit | edit source]

The BORA Xpress SOM Evaluation platform presented here provides a compact solution for any industry and can be easily interfaced with Digital signal Processing application, Plant Automation Control thanks to IEC-61131 SW language environment and/or other GUI QT framework.

The following table summarizes the main hardware and software features available with BORA Xpress SOM EVB:

Hardware[edit | edit source]

| Subsystem | Characteristics |

|---|---|

| CPU | Zynq 7000 Dual Core Cortex-A9 and Artix-7 FPGA |

| SD | microSD boot device |

| USB | OTG |

| Serial Ports | RS232 CAN interface |

| Ethernet0 | Dual EMAC 10/100/1000Mbps |

| Ethernet1 | Dual EMAC 10/100/1000Mbps (routed through EMIO) |

| Memory | External DDR3 SDRAM bank |

| Display | LVDS interface |

| Touchscreen | Resistive |

| Espansion | GPIO connector Digilent Pmod™ Compatible connector |

| WiFi | Socket for DWM Wireless Module |

| JTAG | JTAG and TRACE ports |

| PSU | 12 to 24V DC |

Software[edit | edit source]

| Subsystem | Options |

|---|---|

| Operating System | Linux |

| Distribution | Yocto, Petalinux |

| Applications | SoftPLC |

Block Diagram[edit | edit source]

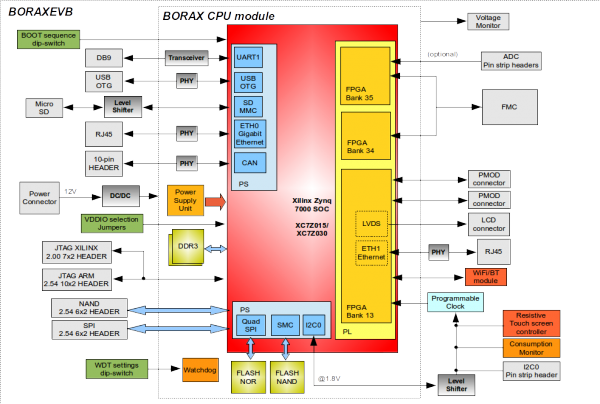

The following picture shows BORA Xpress EVB block diagram:

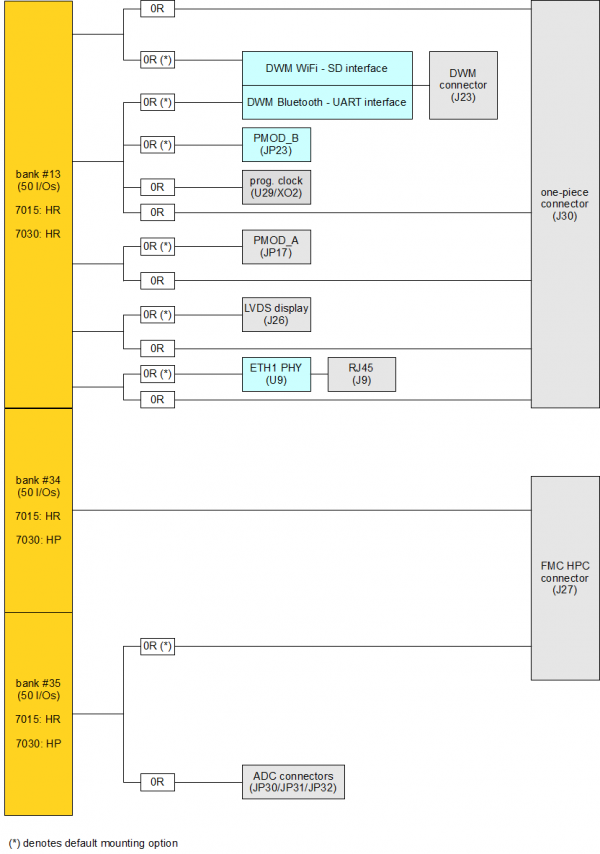

Configurable routing options[edit | edit source]

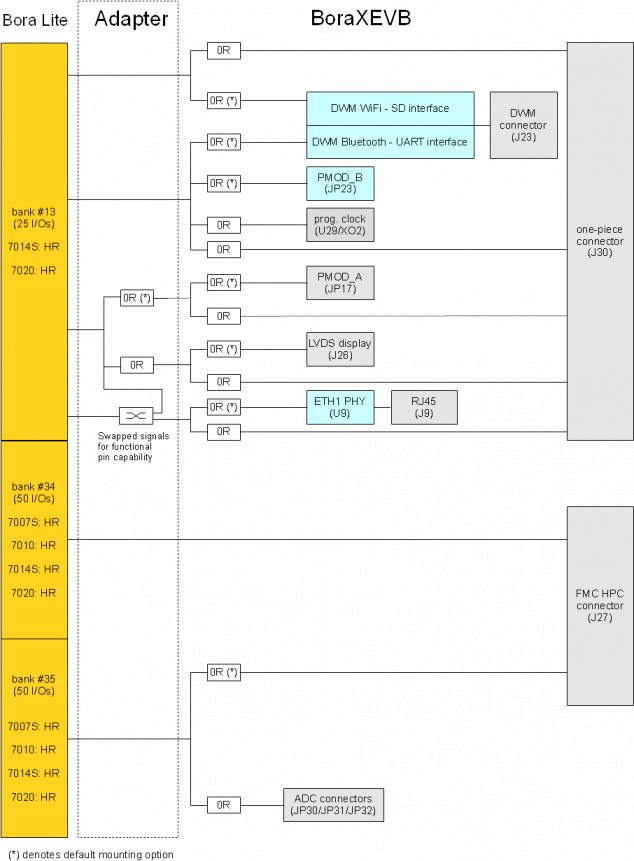

FPGA banks #12, #34 and #35 supports different routing options as shown in the following picture.

For a detailed description of FMC connector routing, please refer to this section.

BoraX[edit | edit source]

Bora Lite[edit | edit source]

Interfaces and Connectors[edit | edit source]

Power Supply[edit | edit source]

Power supply - JP2[edit | edit source]

Power is provided through the JP2 connector.

JP2 connector is a standard 2.1mm/5.5mm DC power jack with positive center pin

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | VIN | Power supply | Nominal: +12V |

| 2 , 3 | DGND | Ground | - |

Voltage selections[edit | edit source]

PL's I/O banks voltage can be selected via configuration jumpers. It is worth remembering that:

- each bank must be powered even if none of its I/Os is used

- voltage selection must be done before powering up the board.

The following table recaps the characteristics of the PL's I/O banks, in terms of allowable power supplies.

| SoM | Zynq p/n | Bank #34 | Bank #13 | Bank #35 | |||

|---|---|---|---|---|---|---|---|

| Type [1] | I/O voltage setting | Type [1] | I/O voltage setting | Type [1] | I/O voltage setting | ||

| BoraX | 7015

(CLG485 package) |

HR

(1.2 - 3.3V) |

User defined | HR

(1.2 - 3.3V) |

User defined | HR

(1.2 - 3.3V) |

User defined |

| 7030

(SBG485 package) |

HP

(1.2 - 1.8V) |

User defined | HR

(1.2 - 3.3V) |

User defined | HP

(1.2 - 1.8V) |

User defined | |

| Bora Lite | 7007S/7010

(CLG400 package) |

HR

(1.2 - 3.3V) |

User defined | HR

(1.2 - 3.3V) |

User defined | HR

(1.2 - 3.3V) |

User defined |

| 7014S/7020

(CLG400 package) |

HR

(1.2 - 3.3V) |

User defined | HR

(1.2 - 3.3V) |

User defined | HR

(1.2 - 3.3V) |

User defined | |

[1]

- HR = High Range

- HP = High Performance

BoraXEVB voltage selection jumpers[edit | edit source]

BoraXEVB provides several configuration jumpers that allow to easily select the voltages used for PL's I/O banks. The following tables lists some of the allowed combinations used to select the most common voltage values. There are other combination available. However, some of them are not allowed and may cause permanent hardware damages to the Zynq part.

Since characteristics of PL's I/O banks differ between Zynq 7015 and 7030 parts, the valid combinations are not the same for all of the BoraX models. Please refer to the following sections for more details.

Even if PL's banks are independent, default configuration of BoraXEVB is such that

- bank 34 and bank 35 have the same supply voltage

- this voltage is selected via JP28.

This configuration is in accordance with default routing of signals used for FMC connector.

Examples of valid combinations for Zynq 7030-based SOMs (default option for BXELK)[edit | edit source]

| Nominal voltage [V] | JP25.1-2 | JP25.3-4 | JP25.5-6 | JP25.7-8 | JP25.9-10 | JP25.11-12 |

|---|---|---|---|---|---|---|

| 1.2 | open | open | closed | closed | closed | open |

| 1.5 | open | closed | open | closed | open | open |

| 1.8 | open | closed | closed | open | closed | open |

| 2.5 | closed | open | closed | open | open | open |

| 3.3 | closed | closed | closed | open | open | open |

| Nominal voltage [V] | JP27.1-2 | JP27.3-4 | JP27.5-6 | JP27.7-8 | JP27.9-10 | JP27.11-12 |

|---|---|---|---|---|---|---|

| 1.2 | open | open | closed | closed | closed | open |

| 1.5 | open | closed | open | closed | open | open |

| 1.8 | open | closed | closed | open | closed | open |

| Nominal voltage [V] | JP28.1-2 | JP28.3-4 | JP28.5-6 | JP28.7-8 | JP28.9-10 | JP28.11-12 |

|---|---|---|---|---|---|---|

| 1.2 | open | open | open | open | closed | open |

| 1.5 | open | open | open | closed | open | open |

| 1.8 | open | open | closed | open | open | open |

Examples of valid combinations for Zynq 7015-based SOMs[edit | edit source]

| Nominal voltage [V] | JP25.1-2 | JP25.3-4 | JP25.5-6 | JP25.7-8 | JP25.9-10 | JP25.11-12 |

|---|---|---|---|---|---|---|

| 1.2 | open | open | closed | closed | closed | open |

| 1.5 | open | closed | open | closed | open | open |

| 1.8 | open | closed | closed | open | closed | open |

| 2.5 | closed | open | closed | open | open | open |

| 3.3 | closed | closed | closed | open | open | open |

| Nominal voltage [V] | JP27.1-2 | JP27.3-4 | JP27.5-6 | JP27.7-8 | JP27.9-10 | JP27.11-12 |

|---|---|---|---|---|---|---|

| 1.2 | open | open | closed | closed | closed | open |

| 1.5 | open | closed | open | closed | open | open |

| 1.8 | open | closed | closed | open | closed | open |

| 2.5 | closed | open | closed | open | open | open |

| 3.3 | closed | closed | closed | open | open | open |

| Nominal voltage [V] | JP28.1-2 | JP28.3-4 | JP28.5-6 | JP28.7-8 | JP28.9-10 | JP28.11-12 |

|---|---|---|---|---|---|---|

| 1.2 | open | open | open | open | closed | open |

| 1.5 | open | open | open | closed | open | open |

| 1.8 | open | open | closed | open | open | open |

| 2.5 | open | closed | open | open | open | open |

| 3.3 | closed | open | open | open | open | open |

Advanced information about voltage selection connectors[edit | edit source]

Bank 13 VDDIO selection connector (JP25)[edit | edit source]

JP25 is a 12-pin 6x2x2.54 pitch vertical header used for the selection - through jumpers - of the bank supply voltages. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 2 | LDO_B13_1V6 | adds +1.6V to VDDIO_BANK13 | - |

| 4 | LDO_B13_800mV | adds +800mV to VDDIO_BANK13 | - |

| 6 | LDO_B13_400mV | adds +400mV to VDDIO_BANK13 | - |

| 8 | LDO_B13_200mV | adds +200mV to VDDIO_BANK13 | - |

| 10 | LDO_B13_100mV | adds +100mV to VDDIO_BANK13 | - |

| 12 | LDO_B13_50mV | adds +50mV to VDDIO_BANK13 | - |

| 1, 3, 5, 7, 9, 11 | DGND | - | - |

The jumper configurations are:

- No jumpers installed -> DC output for VDDIO_BANK13 is 500mV

- Jumper on 1-2 -> adds 1.6V to VDDIO_BANK13 above the default 500mV

- Jumper on 3-4 -> adds 800mV to VDDIO_BANK13 above the default 500mV

- Jumper on 5-6 -> adds 400mV to VDDIO_BANK13 above the default 500mV

- Jumper on 7-8 -> adds 200mV to VDDIO_BANK13 above the default 500mV

- Jumper on 9-10 -> adds 100mV to VDDIO_BANK13 above the default 500mV

- Jumper on 11-12 -> adds 50mV to VDDIO_BANK13 above the default 500mV

The default configuration is VDDIO_BANK13 @ 1.8V (500mV + 800mV + 400mV + 100mV):

- Jumper on 3-4 -> adds 800mV to VDDIO_BANK13 above the default 500mV

- Jumper on 5-6 -> adds 400mV to VDDIO_BANK13

- Jumper on 9-10 -> adds 100mV to VDDIO_BANK13

Bank 35 VDDIO selection connector (JP27)[edit | edit source]

JP27 is a 12-pin 6x2x2.54 pitch vertical header used for the selection - through jumpers - of the bank supply voltages. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 2 | LDO_B35_1V6 | adds +1.6V to VDDIO_BANK35 | - |

| 4 | LDO_B35_800mV | adds +800mV to VDDIO_BANK35 | - |

| 6 | LDO_B35_400mV | adds +400mV to VDDIO_BANK35 | - |

| 8 | LDO_B35_200mV | adds +200mV to VDDIO_BANK35 | - |

| 10 | LDO_B35_100mV | adds +100mV to VDDIO_BANK35 | - |

| 12 | LDO_B35_50mV | adds +50mV to VDDIO_BANK35 | - |

| 1, 3, 5, 7, 9, 11 | DGND | - | - |

The jumper configurations are:

- No jumpers installed -> DC output for VDDIO_BANK35 is 500mV

- Jumper on 1-2 -> adds 1.6V to VDDIO_BANK35 above the default 500mV

- Jumper on 3-4 -> adds 800mV to VDDIO_BANK35 above the default 500mV

- Jumper on 5-6 -> adds 400mV to VDDIO_BANK35 above the default 500mV

- Jumper on 7-8 -> adds 200mV to VDDIO_BANK35 above the default 500mV

- Jumper on 9-10 -> adds 100mV to VDDIO_BANK35 above the default 500mV

- Jumper on 11-12 -> adds 50mV to VDDIO_BANK35 above the default 500mV

The DEFAULT configuration is VDDIO_BANK35 @ 1.8V (500mV + 800mV + 400mV + 100mV):

- Jumper on 3-4 -> adds 800mV to VDDIO_BANK35 above the default 500mV

- Jumper on 5-6 -> adds 400mV to VDDIO_BANK35

- Jumper on 9-10 -> adds 100mV to VDDIO_BANK35

|

Please note that by default VDDIO_BANK35 is supplied by VADJ Regulator. For using a dedicated VDDIO_BANK35, it is required to remove R343 and mount R344: check BORA Xpress Evaluation Kit schematics page 10. |

Bank 34 and VADJ VDDIO selection connector (JP28)[edit | edit source]

JP28 is a 12-pin 6x2x2.54 pitch vertical header used for the selection - through jumpers - of the bank supply voltages. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 2 | VADJ_FB (22K) | selects 3.3V VADJ | - |

| 4 | VADJ_FB (30K9) | selects 2.5V VADJ | - |

| 6 | VADJ_FB (51K1) | selects 1.8V VADJ | - |

| 8 | VADJ_FB (68K) | selects 1.5V VADJ | - |

| 10 | VADJ_FB (100K) | selects 1.2V VADJ | - |

| 12 | RFU | Reserved | - |

| 1, 3, 5, 7, 9, 11 | DGND | - | - |

The jumper configurations are:

- Jumper on 1-2 -> supply VADJ with 3.3V

- Jumper on 3-4 -> supply VADJ with 2.5V

- Jumper on 5-6 -> supply VADJ with 1.8V

- Jumper on 7-8 -> supply VADJ with 1.5V

- Jumper on 9-10 -> supply VADJ with 1.2V

The default configuration is:

- Jumper on 5-6 -> supply VADJ with 1.8V

CPU connectors[edit | edit source]

J1,J2 and J3[edit | edit source]

The pinout of the J1, J2 and J3 connectors of the Bora Xpress EVB is the same of the counterpart connectors on BORA Xpress module.

FMC[edit | edit source]

FPGA Mezzanine Card (FMC) Connector - J27[edit | edit source]

J27 is a 400 pins ANSI/VITA 57.1-2008 FPGA Mezzanine Card Connector that allows to connect to standard I/O mezzanine cards.

Please note that BoraXpress EVB FMC Connector is:

- fully compliant to FMC LPC

- partially compliant to FMC HPC because HPC side is not fully populated.

The following tables detail how BORA Xpress signals have been routed to FMC connector. At this link a spreadsheet providing the same information is available for download.

For more information about I/O voltage of single-ended signals available on FMC connector, please refer to this section.

HPC Row A[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| A1 | DGND | GND | |

| A2 | MGTxRXP1 | DP1_M2C_P | |

| A3 | MGTxRXN1 | DP1_M2C_N | |

| A4 | DGND | GND | |

| A5 | DGND | GND | |

| A6 | MGTxRXP2 | DP2_M2C_P | |

| A7 | MGTxRXN2 | DP2_M2C_N | |

| A8 | DGND | GND | |

| A9 | DGND | GND | |

| A10 | MGTxRXP3 | DP3_M2C_P | |

| A11 | MGTxRXN3 | DP3_M2C_N | |

| A12 | DGND | GND | |

| A13 | DGND | GND | |

| A14 | not connected | DP4_M2C_P | |

| A15 | not connected | DP4_M2C_N | |

| A16 | DGND | GND | |

| A17 | DGND | GND | |

| A18 | not connected | DP5_M2C_P | |

| A19 | not connected | DP5_M2C_N | |

| A20 | DGND | GND | |

| A21 | DGND | GND | |

| A22 | MGTxTXP1 | DP1_C2M_P | |

| A23 | MGTxTXN1 | DP1_C2M_N | |

| A24 | DGND | GND | |

| A25 | DGND | GND | |

| A26 | MGTxTXP2 | DP2_C2M_P | |

| A27 | MGTxTXN2 | DP2_C2M_N | |

| A28 | DGND | GND | |

| A29 | DGND | GND | |

| A30 | MGTxTXP3 | DP3_C2M_P | |

| A31 | MGTxTXN3 | DP3_C2M_N | |

| A32 | DGND | GND | |

| A33 | DGND | GND | |

| A34 | not connected | DP4_C2M_P | |

| A35 | not connected | DP4_C2M_N | |

| A36 | DGND | GND | |

| A37 | DGND | GND | |

| A38 | not connected | DP5_C2M_P | |

| A39 | not connected | DP5_C2M_N | |

| A40 | DGND | GND |

HPC Row B[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| B1 | RSVD | RES1 | |

| B2 | DGND | GND | |

| B3 | DGND | GND | |

| B4 | not connected | DP9_M2C_P | |

| B5 | not connected | DP9_M2C_N | |

| B6 | DGND | GND | |

| B7 | DGND | GND | |

| B8 | not connected | DP8_M2C_P | |

| B9 | not connected | DP8_M2C_N | |

| B10 | DGND | GND | |

| B11 | DGND | GND | |

| B12 | not connected | DP7_M2C_P | |

| B13 | not connected | DP7_M2C_N | |

| B14 | DGND | GND | |

| B15 | DGND | GND | |

| B16 | not connected | DP6_M2C_P | |

| B17 | not connected | DP6_M2C_N | |

| B18 | DGND | GND | |

| B19 | DGND | GND | |

| B20 | MGTREFCLK1P | GBTCLK1_M2C_P | |

| B21 | MGTREFCLK1N | GBTCLK1_M2C_N | |

| B22 | DGND | GND | |

| B23 | DGND | GND | |

| B24 | not connected | DP9_C2M_P | |

| B25 | not connected | DP9_C2M_N | |

| B26 | DGND | GND | |

| B27 | DGND | GND | |

| B28 | not connected | DP8_C2M_P | |

| B29 | not connected | DP8_C2M_N | |

| B30 | DGND | GND | |

| B31 | DGND | GND | |

| B32 | not connected | DP7_C2M_P | |

| B33 | not connected | DP7_C2M_N | |

| B34 | DGND | GND | |

| B35 | DGND | GND | |

| B36 | not connected | DP6_C2M_P | |

| B37 | not connected | DP6_C2M_N | |

| B38 | DGND | GND | |

| B39 | DGND | GND | |

| B40 | RSVD | RES0 |

LPC Row C[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| C1 | DGND | GND | |

| C2 | MGTxTXP0 | DP0_C2M_P | |

| C3 | MGTxTXN0 | DP0_C2M_N | |

| C4 | DGND | GND | |

| C5 | DGND | GND | |

| C6 | MGTxRXP0 | DP0_M2C_P | |

| C7 | MGTxRXN0 | DP0_M2C_N | |

| C8 | DGND | GND | |

| C9 | DGND | GND | |

| C10 | IO_L23P_T3_34 | LA06_P | |

| C11 | IO_L23N_T3_34 | LA06_N | |

| C12 | DGND | GND | |

| C13 | DGND | GND | |

| C14 | IO_L2P_T0_34 | LA10_P | |

| C15 | IO_L2N_T0_34 | LA10_N | |

| C16 | DGND | GND | |

| C17 | DGND | GND | |

| C18 | IO_L1P_T0_34 | LA14_P | |

| C19 | IO_L1N_T0_34 | LA14_N | |

| C20 | DGND | GND | |

| C21 | DGND | GND | |

| C22 | IO_L16P_T2_34 | LA18_P_CC | |

| C23 | IO_L16N_T2_34 | LA18_N_CC | |

| C24 | DGND | GND | |

| C25 | DGND | GND | |

| C26 | IO_L6P_T0_35 | LA27_P | |

| C27 | IO_L6N_T0_VREF_35 | LA27_N | |

| C28 | DGND | GND | |

| C29 | DGND | GND | |

| C30 | I2C0_SCL | SCL | |

| C31 | I2C0_SDA | SDA | |

| C32 | DGND | GND | |

| C33 | DGND | GND | |

| C34 | GA0 | GA0 | |

| C35 | FMC_12P0V | 12P0V | |

| C36 | DGND | GND | |

| C37 | FMC_12P0V | 12P0V | |

| C38 | DGND | GND | |

| C39 | FMC_3P3V | 3P3V | |

| C40 | DGND | GND |

LPC Row D[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| D1 | IO_25_VRP_34 | PG_C2M | |

| D2 | DGND | GND | |

| D3 | DGND | GND | |

| D4 | MGTREFCLK0P | GBTCLK0_M2C_P | |

| D5 | MGTREFCLK0N | GBTCLK0_M2C_N | |

| D6 | DGND | GND | |

| D7 | DGND | GND | |

| D8 | IO_L14P_T2_SRCC_34 | LA01_P_CC | |

| D9 | IO_L14N_T2_SRCC_34 | LA01_N_CC | |

| D10 | DGND | GND | |

| D11 | IO_L9P_T1_DQS_34 | LA05_P | |

| D12 | IO_L9N_T1_DQS_34 | LA05_N | |

| D13 | DGND | GND | |

| D14 | IO_L6P_T0_34 | LA09_P | |

| D15 | IO_L6N_T0_VREF_34 | LA09_N | |

| D16 | DGND | GND | |

| D17 | IO_L20P_T3_34 | LA13_P | |

| D18 | IO_L20N_T3_34 | LA13_N | |

| D19 | DGND | GND | |

| D20 | IO_L15P_T2_DQS_34 | LA17_P_CC | |

| D21 | IO_L15N_T2_DQS_34 | LA17_N_CC | |

| D22 | DGND | GND | |

| D23 | IO_L2P_T0_AD8P_35 | LA23_P | |

| D24 | IO_L2N_T0_AD8N_35 | LA23_N | |

| D25 | DGND | GND | |

| D26 | IO_L5P_T0_AD9P_35 | LA26_P | |

| D27 | IO_L5N_T0_AD9N_35 | LA26_N | |

| D28 | DGND | GND | |

| D29 | JTAG_TCK | TCK | |

| D30 | JTAG_TDI | TDI | |

| D31 | FMC_TDO_ZYNQ_TDI | TDO | |

| D32 | FMC_3P3VAUX | 3P3VAUX | |

| D33 | JTAG_TMS | TMS | |

| D34 | JTAG_TRSTn | TRST_L | |

| D35 | GA0 | GA1 | |

| D36 | FMC_3P3V | 3P3V | |

| D37 | DGND | GND | |

| D38 | FMC_3P3V | 3P3V | |

| D39 | DGND | GND | |

| D40 | FMC_3P3V | 3P3V |

HPC Row E[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| E1 | DGND | GND | |

| E2 | IO_L14P_T2_AD4P_SRCC_35 | HA01_P_CC | |

| E3 | IO_L14N_T2_AD4N_SRCC_35 | HA01_N_CC | |

| E4 | DGND | GND | |

| E5 | DGND | GND | |

| E6 | IO_L20P_T3_AD6P_35 | HA05_P | |

| E7 | IO_L20N_T3_AD6N_35 | HA05_N | |

| E8 | DGND | GND | |

| E9 | IO_L24P_T3_AD15P_35 | HA09_P | |

| E10 | IO_L24N_T3_AD15N_35 | HA09_N | |

| E11 | DGND | GND | |

| E12 | not connected | HA13_P | |

| E13 | not connected | HA13_N | |

| E14 | DGND | GND | |

| E15 | not connected | HA16_P | |

| E16 | not connected | HA16_N | |

| E17 | DGND | GND | |

| E18 | not connected | HA20_P | |

| E19 | not connected | HA20_N | |

| E20 | DGND | GND | |

| E21 | not connected | HB03_P | |

| E22 | not connected | HB03_N | |

| E23 | DGND | GND | |

| E24 | not connected | HB05_P | |

| E25 | not connected | HB05_N | |

| E26 | DGND | GND | |

| E27 | not connected | HB09_P | |

| E28 | not connected | HB09_N | |

| E29 | DGND | GND | |

| E30 | not connected | HB13_P | |

| E31 | not connected | HB13_N | |

| E32 | DGND | GND | |

| E33 | not connected | HB19_P | |

| E34 | not connected | HB19_N | |

| E35 | DGND | GND | |

| E36 | not connected | HB21_P | |

| E37 | not connected | HB21_N | |

| E38 | DGND | GND | |

| E39 | FMC_VADJ | VADJ | |

| E40 | DGND | GND |

HPC Row F[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| F1 | IO_0_VRN_35 | PG_M2C | |

| F2 | DGND | GND | |

| F3 | DGND | GND | |

| F4 | IO_L13P_T2_MRCC_35 | HA00_P_CC | |

| F5 | IO_L13N_T2_MRCC_35 | HA00_N_CC | |

| F6 | DGND | GND | |

| F7 | IO_L19P_T3_35 | HA04_P | |

| F8 | IO_L19N_T3_VREF_35 | HA04_N | |

| F9 | DGND | GND | |

| F10 | IO_L23P_T3_35 | HA08_P | |

| F11 | IO_L23N_T3_35 | HA08_N | |

| F12 | DGND | GND | |

| F13 | not connected | HA12_P | |

| F14 | not connected | HA12_N | |

| F15 | DGND | GND | |

| F16 | not connected | HA15_P | |

| F17 | not connected | HA15_N | |

| F18 | DGND | GND | |

| F19 | not connected | HA19_P | |

| F20 | not connected | HA19_N | |

| F21 | DGND | GND | |

| F22 | not connected | HB02_P | |

| F23 | not connected | HB02_N | |

| F24 | DGND | GND | |

| F25 | not connected | HB04_P | |

| F26 | not connected | HB04_N | |

| F27 | DGND | GND | |

| F28 | not connected | HB08_P | |

| F29 | not connected | HB08_N | |

| F30 | DGND | GND | |

| F31 | not connected | HB12_P | |

| F32 | not connected | HB12_N | |

| F33 | DGND | GND | |

| F34 | not connected | HB16_P | |

| F35 | not connected | HB16_N | |

| F36 | DGND | GND | |

| F37 | not connected | HB20_P | |

| F38 | not connected | HB20_N | |

| F39 | DGND | GND | |

| F40 | FMC_VADJ | VADJ |

LPC Row G[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| G1 | DGND | GND | |

| G2 | IO_L11P_T1_SRCC_34 | CLK0_C2M_P | |

| G3 | IO_L11N_T1_SRCC_34 | CLK0_C2M_N | |

| G4 | DGND | GND | |

| G5 | DGND | GND | |

| G6 | IO_L13P_T1_MRCC_34 | LA00_P_CC | |

| G7 | IO_L13N_T1_MRCC_34 | LA00_N_CC | |

| G8 | DGND | GND | |

| G9 | IO_L4P_T0_34 | LA03_P | |

| G10 | IO_L4N_T0_34 | LA03_N | |

| G11 | DGND | GND | |

| G12 | IO_L3P_T0_DQS_PUDC_B_34 | LA08_P | |

| G13 | IO_L3N_T0_DQS_34 | LA08_N | |

| G14 | DGND | GND | |

| G15 | IO_L22P_T3_34 | LA12_P | |

| G16 | IO_L22N_T3_34 | LA12_N | |

| G17 | DGND | GND | |

| G18 | IO_L19P_T3_34 | LA16_P | |

| G19 | IO_L19N_T3_VREF_34 | LA16_N | |

| G20 | DGND | GND | |

| G21 | IO_L17P_T2_34 | LA20_P | |

| G22 | IO_L17N_T2_34 | LA20_N | |

| G23 | DGND | GND | |

| G24 | IO_L1P_T0_AD0P_35 | LA22_P | |

| G25 | IO_L1N_T0_AD0N_35 | LA22_N | |

| G26 | DGND | GND | |

| G27 | IO_L4P_T0_35 | LA25_P | |

| G28 | IO_L4N_T0_35 | LA25_N | |

| G29 | DGND | GND | |

| G30 | IO_L8P_T1_AD10P_35 | LA29_P | |

| G31 | IO_L8N_T1_AD10N_35 | LA29_N | |

| G32 | DGND | GND | |

| G33 | IO_L10P_T1_AD11P_35 | LA31_P | |

| G34 | IO_L10N_T1_AD11N_35 | LA31_N | |

| G35 | DGND | GND | |

| G36 | IO_L16P_T2_35 | LA33_P | |

| G37 | IO_L16N_T2_35 | LA33_N | |

| G38 | DGND | GND | |

| G39 | FMC_VADJ | VADJ | |

| G40 | DGND | GND |

LPC Row H[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| H1 | FMC_VREF_A_M2C | VREF_A_M2C | |

| H2 | FMC_PRSNT_M2C_L | PRSNT_M2C_L | |

| H3 | DGND | GND | |

| H4 | IO_L12P_T1_MRCC_34 | CLK0_M2C_P | |

| H5 | IO_L12N_T1_MRCC_34 | CLK0_M2C_N | |

| H6 | DGND | GND | |

| H7 | IO_L7P_T1_34 | LA02_P | |

| H8 | IO_L7N_T1_34 | LA02_N | |

| H9 | DGND | GND | |

| H10 | IO_L5P_T0_34 | LA04_P | |

| H11 | IO_L5N_T0_34 | LA04_N | |

| H12 | DGND | GND | |

| H13 | IO_L8P_T1_34 | LA07_P | |

| H14 | IO_L8N_T1_34 | LA07_N | |

| H15 | DGND | GND | |

| H16 | IO_L21P_T3_DQS_34 | LA11_P | |

| H17 | IO_L21N_T3_DQS_34 | LA11_N | |

| H18 | DGND | GND | |

| H19 | IO_L18P_T2_34 | LA15_P | |

| H20 | IO_L18N_T2_34 | LA15_N | |

| H21 | DGND | GND | |

| H22 | IO_L24P_T3_34 | LA19_P | |

| H23 | IO_L24N_T3_34 | LA19_N | |

| H24 | DGND | GND | |

| H25 | IO_L10P_T1_34 | LA21_P | |

| H26 | IO_L10N_T1_34 | LA21_N | |

| H27 | DGND | GND | |

| H28 | IO_L3P_T0_DQS_AD1P_35 | LA24_P | |

| H29 | IO_L3N_T0_DQS_AD1N_35 | LA24_N | |

| H30 | DGND | GND | |

| H31 | IO_L7P_T1_AD2P_35 | LA28_P | |

| H32 | IO_L7N_T1_AD2N_35 | LA28_N | |

| H33 | DGND | GND | |

| H34 | IO_L9P_T1_DQS_AD3P_35 | LA30_P | |

| H35 | IO_L9N_T1_DQS_AD3N_35 | LA30_N | |

| H36 | DGND | GND | |

| H37 | IO_L15P_T2_DQS_AD12P_35 | LA32_P | |

| H38 | IO_L15N_T2_DQS_AD12N_35 | LA32_N | |

| H39 | DGND | GND | |

| H40 | FMC_VADJ | VADJ |

HPC Row J[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| J1 | DGND | GND | |

| J2 | IO_L11P_T1_SRCC_35 | CLK1_C2M_P | |

| J3 | IO_L11N_T1_SRCC_35 | CLK1_C2M_N | |

| J4 | DGND | GND | |

| J5 | DGND | GND | |

| J6 | IO_L18P_T2_AD13P_35 | HA03_P | |

| J7 | IO_L18N_T2_AD13N_35 | HA03_N | |

| J8 | DGND | GND | |

| J9 | IO_L22P_T3_AD7P_35 | HA07_P | |

| J10 | IO_L22N_T3_AD7N_35 | HA07_N | |

| J11 | DGND | GND | |

| J12 | not connected | HA11_P | |

| J13 | not connected | HA11_N | |

| J14 | DGND | GND | |

| J15 | not connected | HA14_P | |

| J16 | not connected | HA14_N | |

| J17 | DGND | GND | |

| J18 | not connected | HA18_P | |

| J19 | not connected | HA18_N | |

| J20 | DGND | GND | |

| J21 | not connected | HA22_P | |

| J22 | not connected | HA22_N | |

| J23 | DGND | GND | |

| J24 | not connected | HB01_P | |

| J25 | not connected | HB01_N | |

| J26 | DGND | GND | |

| J27 | not connected | HB07_P | |

| J28 | not connected | HB07_N | |

| J29 | DGND | GND | |

| J30 | not connected | HB11_P | |

| J31 | not connected | HB11_N | |

| J32 | DGND | GND | |

| J33 | not connected | HB15_P | |

| J34 | not connected | HB15_N | |

| J35 | DGND | GND | |

| J36 | not connected | HB18_P | |

| J37 | not connected | HB18_N | |

| J38 | DGND | GND | |

| J39 | not connected | VIO_B_M2C | |

| J40 | DGND | GND |

HPC Row K[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| K1 | not connected | VREF_B_M2C | |

| K2 | DGND | GND | |

| K3 | DGND | GND | |

| K4 | IO_L12P_T1_MRCC_35 | CLK1_M2C_P | |

| K5 | IO_L12N_T1_MRCC_35 | CLK1_M2C_N | |

| K6 | DGND | GND | |

| K7 | IO_L17P_T2_AD5P_35 | HA02_P | |

| K8 | IO_L17N_T2_AD5N_35 | HA02_N | |

| K9 | DGND | GND | |

| K10 | IO_L21P_T3_DQS_AD14P_35 | HA06_P | |

| K11 | IO_L21N_T3_DQS_AD14N_35 | HA06_N | |

| K12 | DGND | GND | |

| K13 | IO_25_VRP_35 | HA10_P | |

| K14 | not connected | HA10_N | |

| K15 | DGND | GND | |

| K16 | not connected | HA17_P_CC | |

| K17 | not connected | HA17_N_CC | |

| K18 | DGND | GND | |

| K19 | not connected | HA21_P | |

| K20 | not connected | HA21_N | |

| K21 | DGND | GND | |