ONDA SOM/ONDA Hardware/pdf

General Information[edit | edit source]

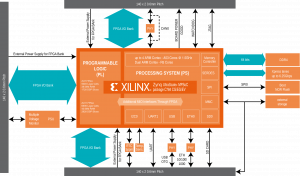

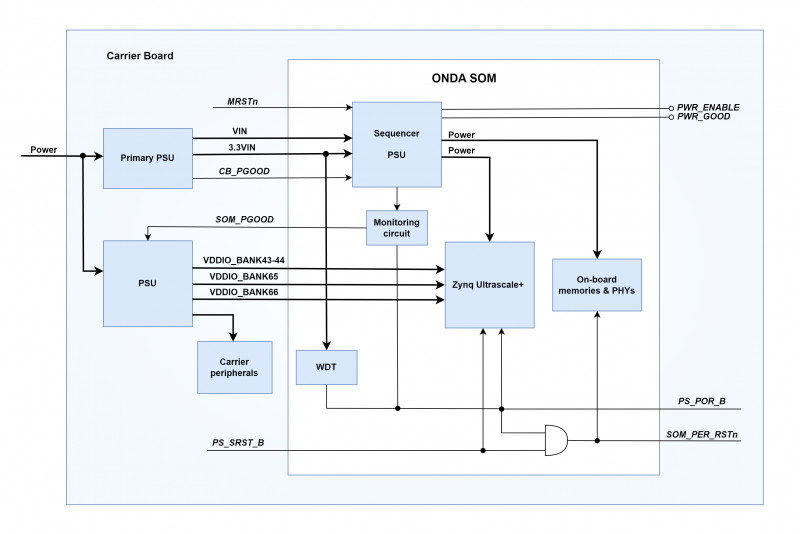

BORA Block Diagram[edit | edit source]

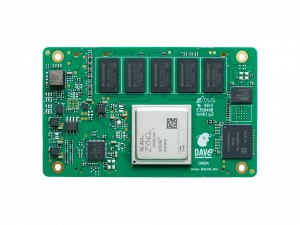

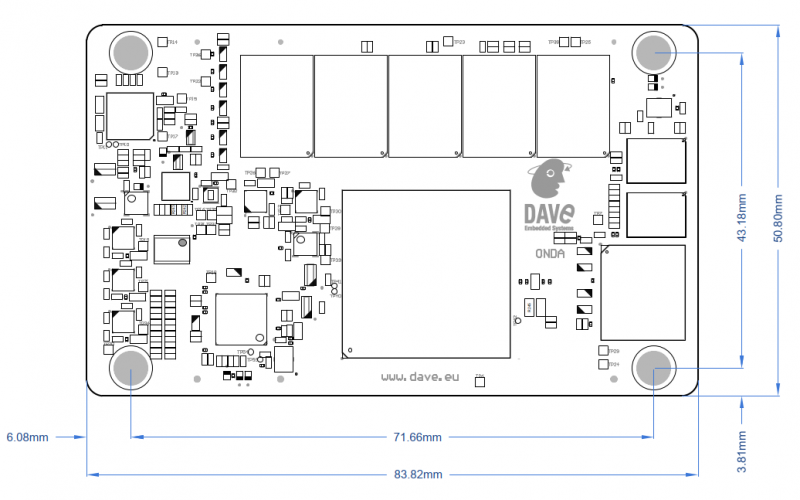

BORA TOP View[edit | edit source]

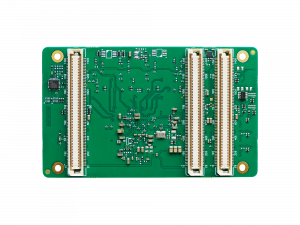

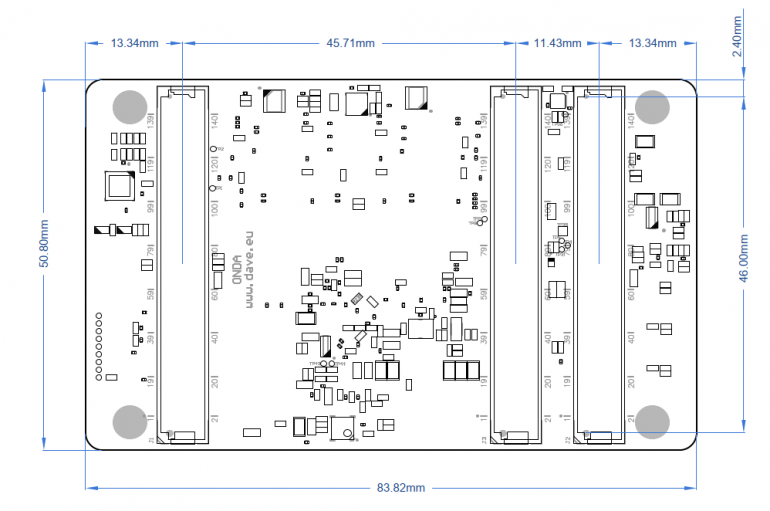

BORA BOTTOM View[edit | edit source]

Processor and memory subsystem[edit | edit source]

The heart of ONDA module is composed by the following components:

- Xilinx Zynq Ultrascale+ XCZU5EG / XCZU5EV SoC

- Power supply unit

- DDR memory banks

- NOR and eMMC flash storage

- 3x 140 pin connectors with interfaces signals

This chapter shortly describes the main ONDA components.

Processor Info[edit | edit source]

| Processor | XCZU5EG | XCZU5EV |

| # Cores | 4x Arm® Cortex®-A53 2x Arm® Cortex®-MRF | |

| Clocks | Cortex®-A53 up to 1.5 GHz Cortex®-MRF up to 600 MHz | |

| L2 Cache | 1 MB | |

| OchChip RAM | 256 KB | |

| DDR4 | 64 bit @ 2400 MHz | |

| GPU | ARM Mali-400 OpenGL ES 1.1 and Open VG 1.1 | |

| VCU | - | H.265, H.264 simultaneous encoder /decoder |

| Ethernet | 1 Gbit/s MAC (with 3 additional RGMII) | |

| PCIe | 2x base specification 2.1 | |

| USB | USB 2.0 | |

| Serial Interfaces | UART, CAN, I2C, SPI | |

PL info[edit | edit source]

The Zynq™Ultrascale+ MPSoCs h software, hardware, interconnect, power, security, and I/O programmability. The range of devices in the Zynq UltraScale+ MPSoC family allows designers to target cost-sensitive as well as high-performance applications from a single platform using industry-standard tools. EG and EV Zynq UltraScale+ devices contains the same PS, the PL, while only the EV device has a VCU hardware cell. The Zynq UltraScale+ MPSoCs are able to serve a wide range of applications including:

- Automotive: Driver assistance, driver information, and infotainment

- Wireless Communications: Support for multiple spectral bands and smart antennas

- Wired Communications: Multiple wired communications standards and context-aware network services

- Data Centers: Software Defined Networks (SDN), data pre-processing, and analytics

- Smarter Vision: Evolving video-processing algorithms, object detection, and analytics

- Connected Control/M2M: Flexible/adaptable manufacturing, factory throughput, quality, and safet

ONDA can mount two versions of the Zynq processor. The following table shows the main PL features:

| Processor | Programmable logic cells | LUTs | Flip flops | Distributed RAM | Total Block RAM | DSP slices | Serial Tranceivers | Peak Serial Transceiver performance |

| XCZU5EG / XCZU5EV | 256K Logic Cells | 117120 | 234240 | 3.5 Mb | 5.1 Mb | 1248 | 4 | 6 Gb/s |

RAM memory bank[edit | edit source]

DDR4 RAM memory bank is composed by 64-bit width chips. The following table reports the RAM specifications:

| CPU connection | Dynamic Memory Controller (DDRC) |

| Size max | 8 GB |

| Width | 64 bit with ECC |

| Speed | 3200 MHz |

NOR flash bank[edit | edit source]

NOR flash is a Serial Peripheral Interface (SPI) device. By default two devices are connected to both QSPI channel 0 and channel 1 for a dual parallel interface. They acts as boot memory. The following table reports the NOR flash specifications:

| CPU connection | PS MIO QSPI Channel 0 / 1 |

| Size min | 16 MB |

| Size max | 32 MB |

| Chip select | SS5 and SS7 |

| Bootable | Yes |

eMMC flash bank[edit | edit source]

On board main storage memory eMMC is connected to the PS MIO interface and it can act as boot peripheral. The following table reports the eMMC flash specifications:

| CPU connection | PS MIO SDIO0 |

| Size min | 8 GB |

| Size max | 128 GB |

| Bootable | Yes |

Power supply unit[edit | edit source]

ONDA embeds all the elements required for powering the unit, therefore power sequencing is self-contained and simplified. Nevertheless, power must be provided from carrier board, and therefore users should be aware of the ranges power supply can assume as well as all other parameters.

Hardware versioning and tracking[edit | edit source]

ONDA SOM implements well established versioning and tracking mechanisms:

- PCB version is copper printed on PCB itself, as shown in Fig. 1

- serial number: it is printed on a white label, as shown in Fig. 2: see also Product serial number page for more details

- ConfigID: it is used by software running on the board for the identification of the product model/hardware configuration. For more details, please refer to this link

- on ONDA SOM ConfigID is stored in an internal I2C EEPROM

Part number composition[edit | edit source]

ONDA SOM module part number is identified by the following digit-code table:

| Part number structure | Options | Description |

|---|---|---|

| Family | DND | Family prefix code |

| SOC |

|

Other versions can be available, please contact technical support |

| RAM |

|

|

| Storage |

|

|

| Boot mode |

|

|

| Mounting options |

|

|

| RFU |

|

|

| Temperature range |

|

|

| PCB revision |

|

PCB release may change for manufacturing purposes (i.e. text fixture adaptation) |

| Manufacturing option |

|

typically connected to production process and quality |

| Software Configuration | -00: standard factory u-boot pre-programmed

-XX: custom version |

If customers require custom SW deployed this section should be defined and agreed. Please contact technical support |

Example[edit | edit source]

ONDA SOM code DNDA20000I1R

- A: XCZU5EG Quad core A53 1.5GHz / Dual core R5F

- 2: 4GB DDR4

- 0: 8GB eMMC + 32MB NOR

- 0: boot from eMMC

- 0: EG devices

- 0: RFU

- I: Industrial grade: -40 to +85°C

- 1: rev. A PCB version

- R: RoHS compliant

- -00: standard factory u-boot pre-programmed

Pinout Table[edit | edit source]

Connectors and Pinout Table[edit | edit source]

This chapter contains the pinout description of the ONDA module, grouped in six tables (two – odd and even pins – for each connector) that report the pin mapping of the three 140-pin ONDA connectors.

Connectors description[edit | edit source]

In the following table are described the interface connectors on ONDA SOM:

| Connector name | Connector Type | Notes | Carrier board counterpart |

|---|---|---|---|

| J1, J2, J3 | Hirose FX8C-140S-SV 3x140 pins 0.6mm pitch connectors |

Hirose FX8C-140P-SV<x>

where <x> stays for:

|

The dedicated carrier board must mount the mating connector and connect the desired peripheral interfaces according to ONDA pinout specifications. See the images below for reference:

Pinout table naming conventions[edit | edit source]

Each row in the pinout tables contains the following information:

- CPU.<x> : pin connected to CPU (processing system) pad named <x>

- FPGA.<x>: pin connected to FPGA (programmable logic) pad named <x>

- CAN.<x> : pin connected to the CAN transceiver

TCAN3413DR - LAN.<x> : pin connected to the LAN PHY

LAN8830 - USB.<x> : pin connected to the USB transceiver

USB3317C - EEPROM.<x>: pin connected to the EEPROM

24LC32AT - RTC.<x>: pin connected to the Real Time Clock

DS3232MZ+ - WD.<x>: pin connected to the Watchdog

MAX6373KA+ - PSU.<x>: pin connected to the Step Down power module

TPSM828303

| Pin | reference to the connector pin |

| Pin Name | Pin (signal) name on the ONDA connectors |

| Internal connections |

Connections to the ONDA components |

| Ball/pin # | Component ball/pin number connected to signal |

| Voltage | I/O voltage levels

|

| Type | Pin type

|

SOM J1 ODD pins (1 to 139) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J1.1 | DGND | DGND | - | - | G | - | Digital ground |

| J1.3 | IO_T0U_N12_VRP_65 | FPGA.IO_T0U_N12_VRP_65 | W9 | Bank 65 | I/O | User defined | |

| J1.5 | IO_L23P_T3U_N8_I2C_SCLK_65 | FPGA.IO_L23P_T3U_N8_I2C_SCLK_65 | K9 | Bank 65 | I/O | User defined | |

| J1.7 | IO_L23N_T3U_N9_65 | FPGA.IO_L23N_T3U_N9_65 | J9 | Bank 65 | I/O | User defined | |

| J1.9 | IO_L21P_T3L_N4_AD8P_65 | FPGA.IO_L21P_T3L_N4_AD8P_65 | J7 | Bank 65 | I/O | User defined | |

| J1.11 | IO_L21N_T3L_N5_AD8N_65 | FPGA.IO_L21N_T3L_N5_AD8N_65 | H7 | Bank 65 | I/O | User defined | |

| J1.13 | DGND | DGND | - | - | - | - | Digital ground |

| J1.15 | IO_L19P_T3L_N0_DBC_AD9P_65 | FPGA.IO_L19P_T3L_N0_DBC_AD9P_65 | J5 | Bank 65 | I/O | User defined | |

| J1.17 | IO_L19N_T3L_N1_DBC_AD9N_65 | FPGA.IO_L19N_T3L_N1_DBC_AD9N_65 | J4 | Bank 65 | I/O | User defined | |

| J1.19 | DGND | DGND | - | - | G | - | Digital ground |

| J1.21 | IO_L17P_T2U_N8_AD10P_65 | FPGA.IO_L17P_T2U_N8_AD10P_65 | N9 | Bank 65 | I/O | User defined | |

| J1.23 | IO_L17N_T2U_N9_AD10N_65 | FPGA.IO_L17N_T2U_N9_AD10N_65 | N8 | Bank 65 | I/O | User defined | |

| J1.25 | IO_L15P_T2L_N4_AD11P_65 | FPGA.IO_L15P_T2L_N4_AD11P_65 | N7 | Bank 65 | I/O | User defined | |

| J1.27 | IO_L15N_T2L_N5_AD11N_65 | FPGA.IO_L15N_T2L_N5_AD11N_65 | N6 | Bank 65 | I/O | User defined | |

| J1.29 | DGND | DGND | - | - | G | - | Digital ground |

| J1.31 | IO_L13P_T2L_N0_GC_QBC_65 | FPGA.IO_L13P_T2L_N0_GC_QBC_65 | L7 | Bank 65 | I/O | User defined | |

| J1.33 | IO_L13N_T2L_N1_GC_QBC_65 | FPGA.IO_L13N_T2L_N1_GC_QBC_65 | L6 | Bank 35 | I/O | User defined | |

| J1.35 | DGND | DGND | - | - | G | - | Digital ground |

| J1.37 | IO_L11P_T1U_N8_GC_65 | FPGA.IO_L11P_T1U_N8_GC_65 | K4 | Bank 65 | I/O | User defined | |

| J1.39 | IO_L11N_T1U_N9_GC_65 | FPGA.IO_L11N_T1U_N9_GC_65 | K3 | Bank 65 | I/O | User defined | |

| J1.41 | IO_L9P_T1L_N4_AD12P_65 | FPGA.IO_L9P_T1L_N4_AD12P_65 | K2 | Bank 65 | I/O | User defined | |

| J1.43 | IO_L9N_T1L_N5_AD12N_65 | FPGA.IO_L9N_T1L_N5_AD12N_65 | J2 | Bank 65 | I/O | User defined | |

| J1.45 | IO_L7P_T1L_N0_QBC_AD13P_65 | FPGA.IO_L7P_T1L_N0_QBC_AD13P_65 | L1 | Bank 65 | I/O | User defined | |

| J1.47 | IO_L7N_T1L_N1_QBC_AD13N_65 | FPGA.IO_L7N_T1L_N1_QBC_AD13N_65 | K1 | Bank 65 | I/O | User defined | |

| J1.49 | DGND | DGND | - | - | G | - | Digital ground |

| J1.51 | IO_L5P_T0U_N8_AD14P_65 | FPGA.IO_L5P_T0U_N8_AD14P_65 | R7 | Bank 65 | I/O | User defined | |

| J1.53 | IO_L5N_T0U_N9_AD14N_65 | FPGA.IO_L5N_T0U_N9_AD14N_65 | T7 | Bank 65 | I/O | User defined | |

| J1.55 | IO_L3P_T0L_N4_AD15P_65 | FPGA.IO_L3P_T0L_N4_AD15P_65 | U8 | Bank 65 | I/O | User defined | |

| J1.57 | IO_L3N_T0L_N5_AD15N_65 | FPGA.IO_L3N_T0L_N5_AD15N_65 | V8 | Bank 65 | I/O | User defined | |

| J1.59 | DGND | DGND | - | - | G | - | Digital ground |

| J1.61 | IO_L1P_T0L_N0_DBC_65 | FPGA.IO_L1P_T0L_N0_DBC_65 | W8 | Bank 65 | I/O | User defined | |

| J1.63 | IO_L1N_T0L_N1_DBC_65 | FPGA.IO_L1N_T0L_N1_DBC_65 | Y8 | Bank 65 | I/O | User defined | |

| J1.65 | DGND | DGND | - | - | G | - | Digital ground |

| J1.67 | VDDIO_BANK65 | S | |||||

| J1.69 | PS_MIO43_501 | CPU.PS_MIO43_501 | K19 | Bank 501 | I/O | 1.8V / 3.3V | (optional) MIO43 pin |

| J1.71 | PS_MIO45_501 | CPU.PS_MIO45_501 | K20 | Bank 501 | I/O | 1.8V / 3.3V | (optional) MIO45 pin |

| J1.73 | PS_MIO49_501 | CPU.PS_MIO45_501 | M18 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.75 | PS_MIO48_501 | CPU.PS_MIO44_501 | J21 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.77 | PS_MIO47_501 | CPU.PS_MIO43_501 | H21 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.79 | PS_MIO46_501 | CPU.PS_MIO42_501 | L20 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.81 | PS_MIO50_501 | CPU.PS_MIO41_501 | M19 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.83 | DGND | DGND | - | - | G | - | Digital ground |

| J1.85 | PS_MIO51_501 | CPU.PS_MIO51_501 | L21 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.87 | ETH_MDIO | CPU.PS_MIO77_502 | F20 | Bank 502 | I/O | 1.8V | 1kOhm pull-up |

| J1.89 | ETH_MDC | CPU.PS_MIO76_502 | B20 | Bank 502 | I/O | 1.8V | |

| J1.91 | ETH_LED1 | LAN.LED1 | 18 | - | 1.8V | ||

| J1.93 | ETH_LED2 | LAN.LED2 | 16 | - | 1.8V | ||

| J1.95 | DGND | DGND | - | - | G | - | Digital ground |

| J1.97 | ETH_TXRX1_N | LAN.TXRXM_B | 6 | D | |||

| J1.99 | ETH_TXRX1_N | LAN.TXRXP_B | 5 | D | |||

| J1.101 | DGND | DGND | - | - | G | - | Digital ground |

| J1.103 | ETH_TXRX0_N | LAN.ETH_TXRX0M_A | 3 | D | |||

| J1.105 | ETH_TXRX0_P | LAN.ETH_TXRX0P_A | 2 | D | |||

| J1.107 | PS_MIO28_501 | CPU.PS_MIO28_501 | K15 | Bank 501 | I/O | 1.8V / 3.3V | (optional) MIO28 pin |

| J1.109 | PS_MIO29_501 | CPU.PS_MIO28_501 | G16 | Bank 501 | I/O | 1.8V / 3.3V | (optional) MIO29 pin |

| J1.111 | USB_CPEN | USB.CPEN | 7 | 3.3V | |||

| J1.113 | USB_VBUS | USB.VBUS | 2 | ||||

| J1.115 | USB_ID | USB.ID | 1 | ||||

| J1.117 | DGND | DGND | - | - | G | - | Digital ground |

| J1.119 | PS_MODE0 | CPU.PS_MODE0 | CPU.P19 | Bank 503 | I/O | 1.8V or 3.3V | This signal is pulled up or down with 1kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (BOOT_MODE[0]=0) |

| J1.119 | PS_MODE1 | CPU.PS_MODE1 | CPU.P20 | Bank 503 | I/O | 1.8V or 3.3V | This signal is pulled up or down with 1kOhm resistor to select proper bootstrap configuration. Default configuration: pull-up (BOOT_MODE[1]=1) |

| J1.119 | PS_MODE2 | CPU.PS_MODE2 | CPU.R20 | Bank 503 | I/O | 1.8V or 3.3V | This signal is pulled up or down with 1kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (BOOT_MODE[2]=0) |

| J1.119 | PS_MODE3 | CPU.PS_MODE3 | CPU.T20 | Bank 503 | I/O | 1.8V or 3.3V | This signal is pulled up or down with 1kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (BOOT_MODE[3]=0) |

| J1.127 | DGND | DGND | - | - | G | - | Digital ground |

| J1.129 | PS_MIO31_501 | CPU.PS_MIO31_501 | CPU.H16 | Bank 501 | I/O | 1.8V or 3.3V | |

| J1.131 | PS_MIO32_501 | CPU.PS_MIO32_501 | CPU.J16 | Bank 501 | I/O | 1.8V or 3.3V | |

| J1.133 | PS_MIO33_501 | CPU.PS_MIO33_501 | CPU.L16 | Bank 501 | I/O | 1.8V or 3.3V | |

| J1.135 | PS_MIO34_501 | CPU.PS_MIO34_501 | CPU.L17 | Bank 501 | I/O | 1.8V or 3.3V | |

| J1.137 | MEM_WPn | EEPROM.WP | 7 | 3.3V | |||

| J1.139 | DGND | DGND | - | - | G | - | Digital ground |

SOM J1 EVEN pins (2 to 140) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J1.2 | VDDIO_BANK65 | S | |||||

| J1.4 | DGND | DGND | - | - | - | G | Digital ground |

| J1.6 | IO_L24P_T3U_N10_PERSTN1_I2C_SDA_65 | FPGA.IO_L24P_T3U_N10_PERSTN1_I2C_SDA_65 | H9 | Bank 65 | I/O | User defined | |

| J1.8 | IO_L24N_T3U_N11_PERSTN0_65 | FPGA.IO_L24N_T3U_N11_PERSTN0_65 | H8 | Bank 65 | I/O | User defined | |

| J1.10 | IO_L22P_T3U_N6_DBC_AD0P_65 | FPGA.IO_L22P_T3U_N6_DBC_AD0P_65 | K8 | Bank 65 | I/O | User defined | |

| J1.12 | IO_L22N_T3U_N7_DBC_AD0N_65 | FPGA.IO_L22N_T3U_N7_DBC_AD0N_65 | K7 | Bank 65 | I/O | User defined | |

| J1.14 | DGND | DGND | - | - | - | G | Digital ground |

| J1.16 | IO_L20P_T3L_N2_AD1P_65 | FPGA.IO_L20P_T3L_N2_AD1P_65 | J6 | Bank 65 | I/O | User defined | |

| J1.18 | IO_L20N_T3L_N3_AD1N_65 | FPGA.IO_L20N_T3L_N3_AD1N_65 | H6 | Bank 65 | I/O | User defined | |

| J1.20 | IO_L18P_T2U_N10_AD2P_65 | FPGA.IO_L18P_T2U_N10_AD2P_65 | M8 | Bank 65 | I/O | User defined | |

| J1.22 | IO_L18N_T2U_N11_AD2N_65 | FPGA.IO_L18N_T2U_N11_AD2N_65 | L8 | Bank 65 | I/O | User defined | |

| J1.24 | DGND | DGND | - | - | - | G | Digital ground |

| J1.26 | IO_L16P_T2U_N6_QBC_AD3P_65 | FPGA.IO_L16P_T2U_N6_QBC_AD3P_65 | P7 | Bank 65 | I/O | User defined | |

| J1.28 | IO_L16N_T2U_N7_QBC_AD3N_65 | FPGA.IO_L16N_T2U_N7_QBC_AD3N_65 | P6 | Bank 65 | I/O | User defined | |

| J1.30 | DGND | DGND | - | - | - | G | Digital ground |

| J1.32 | IO_L14P_T2L_N2_GC_65 | FPGA.IO_L14P_T2L_N2_GC_65 | M6 | Bank 65 | I/O | User defined | |

| J1.34 | IO_L14N_T2L_N3_GC_65 | FPGA.IO_L14N_T2L_N3_GC_65 | L5 | Bank 65 | I/O | User defined | |

| J1.36 | IO_L12P_T1U_N10_GC_65 | FPGA.IO_L12P_T1U_N10_GC_65 | L3 | Bank 65 | I/O | User defined | |

| J1.38 | DGND | DGND | - | - | - | G | Digital ground |

| J1.40 | IO_L12N_T1U_N11_GC_65 | FPGA.IO_L12N_T1U_N11_GC_65 | L2 | Bank 65 | I/O | User defined | |

| J1.42 | IO_L10P_T1U_N6_QBC_AD4P_65 | FPGA.IO_L10P_T1U_N6_QBC_AD4P_65 | H4 | Bank 65 | I/O | User defined | |

| J1.44 | IO_L10N_T1U_N7_QBC_AD4N_65 | FPGA.IO_L10N_T1U_N7_QBC_AD4N_65 | H3 | Bank 65 | I/O | User defined | |

| J1.46 | IO_L8P_T1L_N2_AD5P_65 | FPGA.IO_L8P_T1L_N2_AD5P_65 | J1 | Bank 65 | I/O | User defined | |

| J1.48 | DGND | DGND | - | - | - | G | Digital ground |

| J1.50 | IO_L8N_T1L_N3_AD5N_65 | FPGA.IO_L8N_T1L_N3_AD5N_65 | H1 | Bank 65 | I/O | User defined | |

| J1.52 | IO_L6P_T0U_N10_AD6P_65 | FPGA.IO_L6P_T0U_N10_AD6P_65 | R6 | Bank 65 | I/O | User defined | |

| J1.54 | IO_L6N_T0U_N11_AD6N_65 | FPGA.IO_L6N_T0U_N11_AD6N_65 | T6 | Bank 65 | I/O | User defined | |

| J1.56 | IO_L4P_T0U_N6_DBC_AD7P_SMBALERT_65 | FPGA.IO_L4P_T0U_N6_DBC_AD7P_SMBALERT_65 | R8 | Bank 65 | I/O | User defined | |

| J1.58 | IO_L4N_T0U_N7_DBC_AD7N_65 | FPGA.IO_L4N_T0U_N7_DBC_AD7N_65 | T8 | Bank 65 | I/O | User defined | |

| J1.60 | DGND | DGND | - | - | - | G | Digital ground |

| J1.62 | IO_L2P_T0L_N2_65 | FPGA.IO_L2P_T0L_N2_65 | U9 | Bank 65 | I/O | User defined | |

| J1.64 | IO_L2N_T0L_N3_65 | FPGA.IO_L2N_T0L_N3_65 | V9 | Bank 65 | I/O | User defined | |

| J1.66 | VDDIO_BANK65 | S | |||||

| J1.68 | VDDIO_BANK65 | S | |||||

| J1.70 | IO_T1U_N12_65 | FPGA.IO_T1U_N12_65 | H2 | Bank 65 | I/O | User defined | (optional) PL pin |

| J1.72 | IO_T2U_N12_65 | FPGA.IO_T2U_N12_65 | P9 | Bank 65 | I/O | User defined | (optional) PL pin |

| J1.74 | VREF_65 | FPGA.VREF_65 | R9 | Bank 65 | S | on-board 1kohm pull-down | |

| J1.76 | IO_T1U_N12_65 | FPGA.IO_T1U_N12_65 | K5 | Bank 65 | I/O | User defined | (optional) PL pin |

| J1.78 | PS_MIO23_500 | CPU.PS_MIO23_500 | AB18 | Bank 500 | I/O | 1.8V / 3.3V | |

| J1.80 | PS_MIO24_500 | CPU.PS_MIO23_500 | AB19 | Bank 500 | I/O | 1.8V / 3.3V | |

| J1.82 | PS_MIO25_500 | CPU.PS_MIO23_500 | AB21 | Bank 500 | I/O | 1.8V / 3.3V | |

| J1.84 | PS_MIO39_501 | CPU.PS_MIO39_501 | H19 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.86 | DGND | DGND | - | - | - | G | Digital ground |

| J1.88 | PS_MIO38_501 | CPU.PS_MIO38_501 | H18 | Bank 501 | I/O | 1.8V / 3.3V | |

| J1.90 | ETH_INTn | LAN.ETH_INTn | 9 | D | |||

| J1.92 | DGND | DGND | - | - | - | G | Digital ground |

| J1.94 | ETH_TXRX3_N | LAN.TXRXM_D | 11 | D | |||

| J1.96 | ETH_TXRX3_P | LAN.TXRXP_D | 10 | D | |||

| J1.98 | DGND | DGND | - | - | - | G | Digital ground |

| J1.100 | ETH_TXRX2_N | LAN.TXRXM_C | 8 | D | |||

| J1.102 | ETH_TXRX2_P | LAN.TXRXP_C | 7 | D | |||

| J1.104 | DGND | DGND | - | - | - | G | Digital ground |

| J1.106 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J1.108 | PS_MGTRTXP1_505 | CPU.PS_MGTRTXP1_505 | D23 | Bank 505 | I/O | ||

| J1.110 | PS_MGTRTXN1_505 | CPU.PS_MGTRTXN1_505 | D24 | Bank 505 | I/O | ||

| J1.112 | DGND | DGND | - | - | - | G | Digital ground |

| J1.114 | USB_D_P | USB.DP | 6 | D | |||

| J1.116 | USB_D_N | USB.DM | 5 | D | |||

| J1.118 | DGND | DGND | - | - | - | G | Digital ground |

| J1.120 | PS_MGTRRXP1_505 | CPU.PS_MGTRRXP1_505 | D27 | Bank 505 | I/O | ||

| J1.122 | PS_MGTRRXN1_505 | CPU.PS_MGTRRXN1_505 | D28 | Bank 505 | I/O | ||

| J1.124 | PS_MIO30_501 | CPU.PS_MIO30_501 | F16 | Bank 501 | I/O | 1.8V / 3.3V | (optional) MIO30 pin |

| J1.126 | PS_MGTREFCLK0P_505 | CPU.PS_MGTREFCLK0P_505 | F23 | Bank 505 | I/O | ||

| J1.128 | PS_MGTREFCLK0N_505 | CPU.PS_MGTREFCLK0N_505 | F24 | Bank 505 | I/O | ||

| J1.130 | DGND | DGND | - | - | - | G | Digital ground |

| J1.132 | PS_MGTRTXP0_505 | CPU.PS_MGTRTXP0_505 | E25 | Bank 505 | I/O | ||

| J1.134 | PS_MGTRTXN0_505 | CPU.PS_MGTRTXN0_505 | E26 | Bank 505 | I/O | ||

| J1.136 | PS_MGTRRXP0_505 | CPU.PS_MGTRRXP0_505 | F27 | Bank 505 | I/O | ||

| J1.138 | PS_MGTRRXN0_505 | CPU.PS_MGTRRXN0_505 | F28 | Bank 505 | I/O | ||

| J1.140 | DGND | DGND | - | - | - | G | Digital ground |

SOM J2 ODD pins (1 to 139) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J2.1 | DGND | DGND | - | - | G | - | Digital ground |

| J2.3 | DGND | DGND | - | - | G | - | Digital ground |

| J2.5 | IO_L8P_T1L_N2_AD5P_66 | FPGA.IO_L8P_T1L_N2_AD5P_66 | A2 | Bank 66 | I/O | User defined | |

| J2.7 | IO_L8N_T1L_N3_AD5N_66 | FPGA.IO_L8N_T1L_N3_AD5N_66 | A1 | Bank 66 | I/O | User defined | |

| J2.9 | IO_L6P_T0U_N10_AD6P_66 | FPGA.IO_L6P_T0U_N10_AD6P_66 | G5 | Bank 66 | I/O | User defined | |

| J2.11 | IO_L6N_T0U_N11_AD6N_66 | FPGA.IO_L6N_T0U_N11_AD6N_66 | F5 | Bank 66 | I/O | User defined | |

| J2.13 | DGND | DGND | - | - | G | - | Digital ground |

| J2.15 | IO_L3P_T0L_N4_AD15P_66 | FPGA.IO_L3P_T0L_N4_AD15P_66 | F2 | Bank 66 | I/O | User defined | |

| J2.17 | IO_L3N_T0L_N5_AD15N_66 | FPGA.IO_L3N_T0L_N5_AD15N_66 | E2 | Bank 66 | I/O | User defined | |

| J2.19 | IO_L2P_T0L_N2_66 | FPGA.IO_L2P_T0L_N2_66 | E1 | Bank 66 | I/O | User defined | |

| J2.21 | IO_L2N_T0L_N3_66 | FPGA.IO_L2N_T0L_N3_66 | D1 | Bank 66 | I/O | User defined | |

| J2.23 | DGND | DGND | - | - | G | - | Digital ground |

| J2.25 | IO_L22P_T3U_N6_DBC_AD0P_66 | FPGA.IO_L22P_T3U_N6_DBC_AD0P_66 | C8 | Bank 66 | I/O | User defined | |

| J2.27 | IO_L22N_T3U_N7_DBC_AD0N_66 | FPGA.IO_L22N_T3U_N7_DBC_AD0N_66 | B8 | Bank 66 | I/O | User defined | |

| J2.29 | IO_L21P_T3L_N4_AD8P_66 | FPGA.IO_L21P_T3L_N4_AD8P_66 | A7 | Bank 66 | I/O | User defined | |

| J2.31 | IO_L21N_T3L_N5_AD8N_66 | FPGA.IO_L21N_T3L_N5_AD8N_66 | A6 | Bank 66 | I/O | User defined | |

| J2.33 | DGND | DGND | - | - | G | - | Digital ground |

| J2.35 | IO_L19P_T3L_N0_DBC_AD9P_66 | FPGA.IO_L19P_T3L_N0_DBC_AD9P_66 | B5 | Bank 66 | I/O | User defined | |

| J2.37 | IO_L19N_T3L_N1_DBC_AD9N_66 | FPGA.IO_L19N_T3L_N1_DBC_AD9N_66 | A5 | Bank 66 | I/O | User defined | |

| J2.39 | IO_L18P_T2U_N10_AD2P_66 | FPGA.IO_L18P_T2U_N10_AD2P_66 | E9 | Bank 66 | I/O | User defined | |

| J2.41 | IO_L18N_T2U_N11_AD2N_66 | FPGA.IO_L18N_T2U_N11_AD2N_66 | D9 | Bank 66 | I/O | User defined | |

| J2.43 | DGND | DGND | - | - | G | - | Digital ground |

| J2.45 | IO_L15P_T2L_N4_AD11P_66 | FPGA.IO_L15P_T2L_N4_AD11P_66 | G6 | Bank 66 | I/O | User defined | |

| J2.47 | IO_L15N_T2L_N5_AD11N_66 | FPGA.IO_L15N_T2L_N5_AD11N_66 | F6 | Bank 66 | I/O | User defined | |

| J2.49 | DGND | DGND | - | - | G | - | Digital ground |

| J2.51 | IO_L13P_T2L_N0_GC_QBC_66 | FPGA.IO_L13P_T2L_N0_GC_QBC_66 | D7 | Bank 66 | I/O | User defined | |

| J2.53 | IO_L13N_T2L_N1_GC_QBC_66 | FPGA.IO_L13N_T2L_N1_GC_QBC_66 | D6 | Bank 66 | I/O | User defined | |

| J2.55 | DGND | DGND | - | - | G | - | Digital ground |

| J2.57 | IO_L11P_T1U_N8_GC_66 | FPGA.IO_L11P_T1U_N8_GC_66 | D4 | Bank 66 | I/O | User defined | |

| J2.59 | IO_L11N_T1U_N9_GC_66 | FPGA.IO_L11N_T1U_N9_GC_66 | C4 | Bank 66 | I/O | User defined | |

| J2.61 | DGND | DGND | - | - | G | - | Digital ground |

| J2.63 | IO_L10P_T1U_N6_QBC_AD4P_66 | FPGA.IO_L10P_T1U_N6_QBC_AD4P_66 | B4 | Bank 66 | I/O | User defined | |

| J2.65 | IO_L10N_T1U_N7_QBC_AD4N_66 | FPGA.IO_L10N_T1U_N7_QBC_AD4N_66 | A4 | Bank 66 | I/O | User defined | |

| J2.67 | IO_T1U_N12_66 | FPGA.IO_T1U_N12_66 | D2 | Bank 66 | I/O | User defined | |

| J2.69 | IO_T0U_N12_VRP_66 | FPGA.IO_T0U_N12_VRP_66 | G4 | Bank 66 | I/O | User defined | |

| J2.71 | DGND | DGND | - | - | G | - | Digital ground |

| J2.73 | IO_T3U_N12_66 | FPGA.IO_T3U_N12_66 | C7 | Bank 66 | I/O | User defined | |

| J2.75 | IO_T2U_N12_66 | FPGA.IO_T2U_N12_66 | E7 | Bank 66 | I/O | User defined | |

| J2.77 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.79 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.81 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.83 | ETH_RSTn | LAN.RESET_N | 43 | I | 1.8V | Internally connected to ETH_VDDIO via 10K resistor and to SOM_PER_RSTn | |

| J2.85 | USB_RSTn | USB.RESETB | 22 | I | 1.8V | Internally connected to USB_VDDIO via 10K resistor | |

| J2.87 | CAN_STBYn | CAN.STB | 8 | I | Internally connected to VDDIO_BANK501 via 10K resistor | ||

| J2.89 | PS_MIO27_501 | CPU.PS_MIO27_501 | F16 | Bank 501 | I/O | 1.8V / 3.3V | (optional) MIO27 pin |

| J2.91 | PS_MIO35_501 | CPU.PS_MIO35_501 | F16 | Bank 501 | I/O | 1.8V / 3.3V | (optional) MIO35 pin |

| J2.93 | RTC_32KHZ | RTC.32KHZ | 1 | 3.3V | O | 3.3V | |

| J2.95 | RTC_RSTn | RTC.RSTn | 4 | 3.3V | I/O | 3.3V | |

| J2.97 | ADC_N | FPGA.VN | T12 | Bank 503 | A | ||

| J2.99 | ADC_P | FPGA.VP | R13 | Bank 503 | A | ||

| J2.101 | AGND | AGND | - | - | G | - | Analog ground |

| J2.103 | SOM_PER_RSTn | - | - | - | - | - | Peripheral reset buffer (NOR, eMMC, LAN PHY, USB PHY) |

| J2.105 | CAN_L | CAN.CANL | 6 | - | D | - | |

| J2.107 | CAN_H | CAN.CANH | 7 | - | D | - | |

| J2.109 | DGND | DGND | - | - | G | - | Digital ground |

| J2.111 | RTC_INTn/SQW | RTC.INT/SQW | 3 | 3.3V | I/O | 3.3V | It can be left open if not used. When used, a proper pull-up resistor is required on the carrier board.

For further details, please refer to the Maxim Integrated DS3232 datasheet. |

| J2.113 | RTC_VBAT | RTC.VBAT | 6 | - | S | - | |

| J2.115 | VBAT | CPU.VCC_PSBATT | Y18 | - | S | - | |

| J2.117 | DGND | DGND | - | - | G | - | Digital ground |

| J2.119 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | Auxiliary 3.3V Power Supply | |

| J2.121 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | Auxiliary 3.3V Power Supply | |

| J2.123 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | Auxiliary 3.3V Power Supply | |

| J2.125 | DGND | DGND | - | - | G | - | Digital ground |

| J2.127 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.129 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.131 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.133 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.135 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.137 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.139 | DGND | DGND | - | - | G | - | Digital ground |

SOM J2 EVEN pins (2 to 140) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J2.2 | DGND | DGND | - | - | G | - | Digital ground |

| J2.4 | IO_L9P_T1L_N4_AD12P_66 | FPGA.IO_L9P_T1L_N4_AD12P_66 | B3 | Bank 66 | I/O | User defined | |

| J2.6 | IO_L9N_T1L_N5_AD12N_66 | FPGA.IO_L9N_T1L_N5_AD12N_66 | A3 | Bank 66 | I/O | User defined | |

| J2.8 | IO_L7P_T1L_N0_QBC_AD13P_66 | FPGA.IO_L7P_T1L_N0_QBC_AD13P_66 | C1 | Bank 66 | I/O | User defined | |

| J2.10 | IO_L7N_T1L_N1_QBC_AD13N_66 | FPGA.IO_L7N_T1L_N1_QBC_AD13N_66 | B1 | Bank 66 | I/O | User defined | |

| J2.12 | DGND | DGND | - | - | G | - | Digital ground |

| J2.14 | IO_L5P_T0U_N8_AD14P_66 | FPGA.IO_L5P_T0U_N8_AD14P_66 | E4 | Bank 66 | I/O | User defined | |

| J2.16 | IO_L5N_T0U_N9_AD14N_66 | FPGA.IO_L5N_T0U_N9_AD14N_66 | E3 | Bank 66 | I/O | User defined | |

| J2.18 | IO_L4P_T0U_N6_DBC_AD7P_66 | FPGA.IO_L4P_T0U_N6_DBC_AD7P_66 | G3 | Bank 66 | I/O | User defined | |

| J2.20 | IO_L4N_T0U_N7_DBC_AD7N_66 | FPGA.IO_L4N_T0U_N7_DBC_AD7N_66 | F3 | Bank 66 | I/O | User defined | |

| J2.22 | DGND | DGND | - | - | G | - | Digital ground |

| J2.24 | IO_L24P_T3U_N10_66 | FPGA.IO_L24P_T3U_N10_66 | C9 | Bank 66 | I/O | User defined | |

| J2.26 | IO_L24N_T3U_N11_66 | FPGA.IO_L24N_T3U_N11_66 | B9 | Bank 66 | I/O | User defined | |

| J2.28 | IO_L23P_T3U_N8_66 | FPGA.IO_L23P_T3U_N8_66 | A9 | Bank 66 | I/O | User defined | |

| J2.30 | IO_L23N_T3U_N9_66 | FPGA.IO_L23N_T3U_N9_66 | A8 | Bank 66 | I/O | User defined | |

| J2.32 | DGND | DGND | - | - | G | - | Digital ground |

| J2.34 | IO_L20P_T3L_N2_AD1P_66 | FPGA.IO_L20P_T3L_N2_AD1P_66 | C6 | Bank 66 | I/O | User defined | |

| J2.36 | IO_L20N_T3L_N3_AD1N_66 | FPGA.IO_L20N_T3L_N3_AD1N_66 | B6 | Bank 66 | I/O | User defined | |

| J2.38 | IO_L1P_T0L_N0_DBC_66 | FPGA.IO_L1P_T0L_N0_DBC_66 | G1 | Bank 66 | I/O | User defined | |

| J2.40 | IO_L1N_T0L_N1_DBC_66 | FPGA.IO_L1N_T0L_N1_DBC_66 | F1 | Bank 66 | I/O | User defined | |

| J2.42 | DGND | DGND | - | - | G | - | Digital ground |

| J2.44 | IO_L17P_T2U_N8_AD10P_66 | FPGA.IO_L17P_T2U_N8_AD10P_66 | F8 | Bank 66 | I/O | User defined | |

| J2.46 | IO_L17N_T2U_N9_AD10N_66 | FPGA.IO_L17N_T2U_N9_AD10N_66 | E8 | Bank 66 | I/O | User defined | |

| J2.48 | IO_L16P_T2U_N6_QBC_AD3P_66 | FPGA.IO_L16P_T2U_N6_QBC_AD3P_66 | G8 | Bank 66 | I/O | User defined | |

| J2.50 | IO_L16N_T2U_N7_QBC_AD3N_66 | FPGA.IO_L16N_T2U_N7_QBC_AD3N_66 | F7 | Bank 66 | I/O | User defined | |

| J2.52 | DGND | DGND | - | - | G | - | Digital ground |

| J2.54 | IO_L14P_T2L_N2_GC_66 | FPGA.IO_L14P_T2L_N2_GC_66 | E5 | Bank 66 | I/O | User defined | |

| J2.56 | IO_L14N_T2L_N3_GC_66 | FPGA.IO_L14N_T2L_N3_GC_66 | D5 | Bank 66 | I/O | User defined | |

| J2.58 | DGND | DGND | - | - | G | - | Digital ground |

| J2.60 | IO_L12P_T1U_N10_GC_66 | FPGA.IO_L12P_T1U_N10_GC_66 | C3 | Bank 66 | I/O | User defined | |

| J2.62 | IO_L12N_T1U_N11_GC_66 | FPGA.IO_L12N_T1U_N11_GC_66 | C2 | Bank 66 | I/O | User defined | |

| J2.64 | DGND | DGND | - | - | G | - | Digital ground |

| J2.66 | VDDIO_BANK66 | FPGA.VCCO_66 | B7 D3 E6 |

Bank 66 | S | User defined | Bank66 I/O Power Supply |

| J2.68 | VDDIO_BANK66 | FPGA.VCCO_66 | B7 D3 E6 |

Bank 66 | S | User defined | Bank66 I/O Power Supply |

| J2.70 | VDDIO_BANK66 | FPGA.VCCO_66 | B7 D3 E6 |

Bank 66 | S | User defined | Bank66 I/O Power Supply |

| J2.72 | VDDIO_BANK66 | FPGA.VCCO_66 | B7 D3 E6 |

Bank 66 | S | User defined | Bank66 I/O Power Supply |

| J2.74 | VREF_66 | FPGA.VREF_66 | G9 | Bank 66 | S | on-board 1kohm pull-down | |

| J2.76 | PS_ERROR_OUT | CPU.PS_ERROR_OUT | CPU.P17 | Bank 503 | I/O | 1.8V or 3.3V | This signal has an optional internal pull-up (10k) |

| J2.78 | PS_ERROR_STATUS | CPU.PS_ERROR_STATUS | CPU.M20 | Bank 503 | I/O | 1.8V or 3.3V | This signal has an internal pull-up (10k) |

| J2.80 | JTAG_TDO | CPU.PS_JTAG_TDO | T21 | Bank 503 | O | 1.8V or 3.3V | |

| J2.82 | JTAG_TDI | CPU.PS_JTAG_TDI | R18 | Bank 503 | I | 1.8V or 3.3V | |

| J2.84 | JTAG_TMS | CPU.PS_JTAG_TMS | N21 | Bank 503 | I | 1.8V or 3.3V | |

| J2.86 | JTAG_TCK | CPU.PS_JTAG_TCK | R19 | Bank 503 | I | 1.8V or 3.3V | |

| J2.88 | DGND | DGND | - | - | G | - | Digital ground |

| J2.90 | PS_INIT_B | FPGA.PS_INIT_B | P21 | Bank 503 | I/O | 1.8V or 3.3V | For further details, please refer to PL initialization signals |

| J2.92 | PS_PROG_B | FPGA.PS_PROG_B | V10 | Bank 503 | I | 1.8V or 3.3V | For further details, please refer to PL initialization signals

(10 kohm pull-up resistor is already mounted on ONDA SOM) |

| J2.94 | PS_DONE | FPGA.PS_DONE | M21 | Bank 503 | I/O | 1.8V or 3.3V | For further details, please refer to PL initialization signals

(10 kohm pull-up resistor is already mounted on ONDA SOM) |

| J2.96 | WD_SET2 | WDT.SET2 | 6 | 3.3V | I | 3.3V | |

| J2.98 | WD_SET1 | WDT.SET1 | 5 | 3.3V | I | 3.3V | |

| J2.100 | WD_SET0 | WDT.SET0 | 4 | 3.3V | I | 3.3V | |

| J2.102 | DGND | DGND | - | - | G | - | Digital ground |

| J2.104 | PS_MIO36_501 | CPU.PS_MIO36_501 | K17 | Bank 501 | I/O | 1.8V or 3.3V | |

| J2.106 | PS_MIO37_501 | CPU.PS_MIO37_501 | J17 | Bank 501 | I/O | 1.8V or 3.3V | |

| J2.108 | SOM_PGOOD | n.a. | 3.3V | O | 3.3V | Internally connected to +VIN_3V3 via 10K resistor

For further details, please refer to Power_Supply_Unit | |

| J2.110 | CB_PGOOD | n.a. | 3.3VIN | I | 3.3V | Internally connected to +VIN_3V3 via 10K resistor

For further details, please refer to Power_Supply_Unit | |

| J2.112 | PS_SRST_B | CPU.PS_SRST_B | N19 | Bank 503 | I | 1.8V or 3.3V | Internally connected to Bank 503 power supply via 10K resistor

For further details, please refer to Reset scheme |

| J2.114 | PS_POR_B | CPU.PS_POR_B WD.WDOn |

P16 7 |

Bank 503 | I/O | 1.8V or 3.3V | Internally connected to Bank 503 power supply via 10K resistor

For further details, please refer to Reset scheme |

| J2.116 | MRSTn | Voltage monitor | 3.3VIN | I | 3.3V | For further details, please refer to Reset scheme | |

| J2.118 | DGND | DGND | - | - | G | - | Digital ground |

| J2.120 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.122 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.124 | DGND | DGND | - | - | G | - | Digital ground |

| J2.126 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.128 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.130 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.132 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.134 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.136 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.138 | VIN | VIN | - | VIN | S | SOM Power Supply | |

| J2.140 | DGND | DGND | - | - | G | - | Digital ground |

SOM J3 ODD pins (1 to 139)declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J3.1 | DGND | DGND | - | - | G | - | Digital ground |

| J3.3 | MGTREFCLK0N | FPGA.MGTREFCLK0N_224 | Y5 | MGTAVCC | D | ||

| J3.5 | MGTREFCLK0P | FPGA.MGTREFCLK0P_224 | Y6 | MGTAVCC | D | ||

| J3.7 | DGND | DGND | - | - | G | - | Digital ground |

| J3.9 | MGTHTXP0 | FPGA.MGTHTXP0_224 | W4 | MGTAVCC | D | ||

| J3.11 | MGTHTXN0 | FPGA.MGTHTXN0_224 | W3 | MGTAVCC | D | ||

| J3.13 | DGND | DGND | - | - | G | - | Digital ground |

| J3.15 | MGTHTXP1 | FPGA.MGTHTXP1_224 | U4 | MGTAVCC | D | ||

| J3.17 | MGTHTXN1 | FPGA.MGTHTXN1_224 | U3 | MGTAVCC | D | ||

| J3.19 | DGND | DGND | - | - | G | - | Digital ground |

| J3.21 | MGTHTXP2 | FPGA.MGTHTXP2_224 | R4 | MGTAVCC | D | ||

| J3.23 | MGTHTXN2 | FPGA.MGTHTXN2_224 | R3 | MGTAVCC | D | ||

| J3.25 | DGND | DGND | - | - | G | - | Digital ground |

| J3.27 | MGTHTXP3 | FPGA.MGTHTXP3_224 | N4 | MGTAVCC | D | ||

| J3.29 | MGTHTXN3 | FPGA.MGTHTXN3_224 | N3 | MGTAVCC | D | ||

| J3.31 | DGND | DGND | - | - | G | - | Digital ground |

| J3.33 | PG_0V9_GTH | - | - | 3.3VIN | O | - | Power Good for 0V9 GTH power supply LDO regulator |

| J3.35 | EN_0V9_GTH | - | - | 3.3VIN | I | - | Power Enable for 0V9 GTH power supply LDO regulator |

| J3.37 | DGND | DGND | - | - | G | - | Digital ground |

| J3.39 | IO_L8P_HDGC_AD4P_43 | FPGA.IO_L8P_HDGC_AD4P_43 | AB11 | Bank 43 | I/O | User defined | |

| J3.41 | IO_L8N_HDGC_AD4N_43 | FPGA.IO_L8N_HDGC_AD4N_43 | AC11 | Bank 43 | I/O | User defined | |

| J3.43 | DGND | DGND | - | - | G | - | Digital ground |

| J3.45 | IO_L7P_HDGC_AD5P_43 | FPGA.IO_L7P_HDGC_AD5P_43 | AD11 | Bank 43 | I/O | User defined | |

| J3.47 | IO_L7N_HDGC_AD5N_43 | FPGA.IO_L7N_HDGC_AD5N_43 | AD10 | Bank 43 | I/O | User defined | |

| J3.49 | DGND | DGND | - | - | G | - | Digital ground |

| J3.51 | IO_L6P_HDGC_AD6P_43 | FPGA.IO_L6P_HDGC_AD6P_43 | AC12 | Bank 43 | I/O | User defined | |

| J3.53 | IO_L6N_HDGC_AD6N_43 | FPGA.IO_L6N_HDGC_AD6N_43 | AD12 | Bank 43 | I/O | User defined | |

| J3.55 | DGND | DGND | - | - | G | - | Digital ground |

| J3.57 | IO_L5P_HDGC_AD7P_43 | FPGA.IO_L5P_HDGC_AD7P_43 | AE12 | Bank 43 | I/O | User defined | |

| J3.59 | IO_L5N_HDGC_AD7N_43 | FPGA.IO_L5N_HDGC_AD7N_43 | AF12 | Bank 43 | I/O | User defined | |

| J3.61 | DGND | DGND | - | - | G | - | Digital ground |

| J3.63 | IO_L4P_AD8P_43 | FPGA.IO_L4P_AD8P_43 | AE10 | Bank 43 | I/O | User defined | |

| J3.65 | IO_L4N_AD8N_43 | FPGA.IO_L4N_AD8N_43 | AF10 | Bank 43 | I/O | User defined | |

| J3.67 | DGND | DGND | - | - | G | - | Digital ground |

| J3.69 | DGND | DGND | - | - | G | - | Digital ground |

| J3.71 | IO_L3P_AD9P_43 | FPGA.IO_L3P_AD9P_43 | AH12 | Bank 43 | I/O | User defined | |

| J3.73 | IO_L3N_AD9N_43 | FPGA.IO_L3N_AD9N_43 | AH11 | Bank 43 | I/O | User defined | |

| J3.75 | DGND | DGND | - | - | G | - | Digital ground |

| J3.77 | IO_L2P_AD10P_43 | FPGA.IO_L2P_AD10P_43 | AF11 | Bank 43 | I/O | User defined | |

| J3.79 | IO_L2N_AD10N_43 | FPGA.IO_L2N_AD10N_43 | AG11 | Bank 43 | I/O | User defined | |

| J3.81 | DGND | DGND | - | - | G | - | Digital ground |

| J3.83 | IO_L1P_AD11P_43 | FPGA.IO_L1P_AD11P_43 | AG10 | Bank 43 | I/O | User defined | |

| J3.85 | IO_L1N_AD11N_43 | FPGA.IO_L1N_AD11N_43 | AH10 | Bank 43 | I/O | User defined | |

| J3.87 | DGND | DGND | - | - | G | - | Digital ground |

| J3.89 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J3.91 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J3.93 | DGND | DGND | - | - | G | - | Digital ground |

| J3.95 | VDDIO_BANK43-44 | FPGA.VCCO_13 | AC10 AG12 AA14 AD13 |

Bank 43-44 | S | User defined | Bank43-44 I/O Power Supply |

| J3.97 | VDDIO_BANK43-44 | FPGA.VCCO_13 | AC10 AG12 AA14 AD13 |

Bank 43-44 | S | User defined | Bank43-44 I/O Power Supply |

| J3.99 | VDDIO_BANK43-44 | FPGA.VCCO_13 | AC10 AG12 AA14 AD13 |

Bank 43-44 | S | User defined | Bank43-44 I/O Power Supply |

| J3.101 | DGND | DGND | - | - | G | - | Digital ground |

| J3.103 | DGND | DGND | - | - | G | - | Digital ground |

| J3.105 | IO_L11P_AD9P_44 | FPGA.IO_L11P_AD9P_44 | W12 | Bank 44 | I/O | User defined | |

| J3.107 | IO_L11N_AD9N_44 | FPGA.IO_L11N_AD9N_44 | W11 | Bank 44 | I/O | User defined | |

| J3.109 | DGND | DGND | - | - | G | - | Digital ground |

| J3.111 | IO_L9P_AD11P_44 | FPGA.IO_L9P_AD11P_44 | W14 | Bank 44 | I/O | User defined | |

| J3.113 | IO_L9N_AD11N_44 | FPGA.IO_L9N_AD11N_44 | W13 | Bank 44 | I/O | User defined | |

| J3.115 | DGND | DGND | - | - | G | - | Digital ground |

| J3.117 | IO_L7P_HDGC_44 | FPGA.IO_L7P_HDGC_44 | AA13 | Bank 44 | I/O | User defined | |

| J3.119 | IO_L7N_HDGC_44 | FPGA.IO_L7N_HDGC_44 | AB13 | Bank 44 | I/O | User defined | |

| J3.121 | DGND | DGND | - | - | G | - | Digital ground |

| J3.123 | IO_L5P_HDGC_44 | FPGA.IO_L5P_HDGC_44 | AD15 | Bank 44 | I/O | User defined | |

| J3.125 | IO_L5N_HDGC_44 | FPGA.IO_L5N_HDGC_44 | AD14 | Bank 44 | I/O | User defined | |

| J3.127 | DGND | DGND | - | - | G | - | Digital ground |

| J3.129 | IO_L3P_AD13P_44 | FPGA.IO_L3P_AD13P_44 | AG13 | Bank 44 | I/O | User defined | |

| J3.131 | IO_L3N_AD13N_44 | FPGA.IO_L3N_AD13N_44 | AH13 | Bank 44 | I/O | User defined | |

| J3.133 | DGND | DGND | - | - | G | - | Digital ground |

| J3.135 | IO_L1P_AD15P_44 | FPGA.IO_L1P_AD15P_44 | AE15 | Bank 44 | I/O | User defined | |

| J3.137 | IO_L1N_AD15N_44 | FPGA.IO_L1N_AD15N_44 | AE14 | Bank 44 | I/O | User defined | |

| J3.139 | DGND | DGND | - | - | G | - | Digital ground |

SOM J3 EVEN pins (2 to 140) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J3.2 | DGND | DGND | - | - | G | - | Digital ground |

| J3.4 | DGND | DGND | - | - | G | - | Digital ground |

| J3.6 | MGTREFCLK1N | FPGA.MGTREFCLK1N_224 | V5 | MGTAVCC | D | ||

| J3.8 | MGTREFCLK1P | FPGA.MGTREFCLK1P_224 | V6 | MGTAVCC | D | ||

| J3.10 | DGND | DGND | - | - | G | - | Digital ground |

| J3.12 | MGTHRXP0 | FPGA.MGTHRXP0_224 | Y2 | MGTAVCC | D | ||

| J3.14 | MGTHRXN0 | FPGA.MGTHRXN0_224 | Y1 | MGTAVCC | D | ||

| J3.16 | DGND | DGND | - | - | G | - | Digital ground |

| J3.18 | MGTHRXP1 | FPGA.MGTHRXP1_224 | V2 | MGTAVCC | D | ||

| J3.20 | MGTHRXN1 | FPGA.MGTHRXN1_224 | V1 | MGTAVCC | D | ||

| J3.22 | DGND | DGND | - | - | G | - | Digital ground |

| J3.24 | MGTHRXP2 | FPGA.MGTHRXP2_224 | T2 | MGTAVCC | D | ||

| J3.26 | MGTHRXN2 | FPGA.MGTHRXN2_224 | T1 | MGTAVCC | D | ||

| J3.28 | DGND | DGND | - | - | G | - | Digital ground |

| J3.30 | MGTHRXP3 | FPGA.MGTHRXP3_224 | P2 | MGTAVCC | D | ||

| J3.32 | MGTHRXN3 | FPGA.MGTHRXN3_224 | P1 | MGTAVCC | D | ||

| J3.34 | DGND | DGND | - | - | G | - | Digital ground |

| J3.36 | DGND | DGND | - | - | G | - | Digital ground |

| J3.38 | IO_L12P_AD0P_43 | FPGA.IO_L12P_AD0P_43 | AB10 | Bank 43 | I/O | User defined | |

| J3.40 | IO_L12N_AD0N_43 | FPGA.IO_L12N_AD0N_43 | AB9 | Bank 43 | I/O | User defined | |

| J3.42 | DGND | DGND | - | - | G | - | Digital ground |

| J3.44 | IO_L11P_AD1P_43 | FPGA.IO_L11P_AD1P_43 | Y9 | Bank 43 | I/O | User defined | |

| J3.46 | IO_L11N_AD1N_43 | FPGA.IO_L11N_AD1N_43 | AA8 | Bank 43 | I/O | User defined | |

| J3.48 | DGND | DGND | - | - | G | - | Digital ground |

| J3.50 | IO_L10P_AD2P_43 | FPGA.IO_L10P_AD2P_43 | W10 | Bank 43 | I/O | User defined | |

| J3.52 | IO_L10N_AD2N_43 | FPGA.IO_L10N_AD2N_43 | Y10 | Bank 43 | I/O | User defined | |

| J3.54 | DGND | DGND | - | - | G | - | Digital ground |

| J3.56 | IO_L9P_AD3P_43 | FPGA.IO_L9P_AD3P_43 | AA11 | Bank 43 | I/O | User defined | |

| J3.58 | IO_L9N_AD3N_43 | FPGA.IO_L9N_AD3N_43 | AA10 | Bank 43 | I/O | User defined | |

| J3.60 | DGND | DGND | - | - | G | - | Digital ground |

| J3.62 | PG_0V9_VCU | PSU.7 | - | 3.3VIN | O | - | Power Good for 0V9 VCU power supply LDO regulator |

| J3.64 | EN_0V9_VCU | PSU.5 | - | 3.3VIN | I | - | Power Enable for 0V9 VCU power supply LDO regulator |

| J3.62 | PG_1V8_IO | PSU.7 | - | 3.3VIN | O | - | Power Good for 1V8 I/O power supply regulator |

| J3.68 | DGND | DGND | - | - | G | - | Digital ground |

| J3.64 | EN_1V8_IO | PSU.5 | - | 3.3VIN | I | - | Power Enable for 1V8 I/O power supply regulator |

| J3.72 | PG_0V85_MGT | PSU.7 | - | 3.3VIN | O | - | Power Good for 0V85 GTR power supply LDO regulator |

| J3.74 | EN_0V85_MGT | PSU.5 | - | 3.3VIN | I | - | Power Enable for 0V85 GTR power supply LDO regulator |

| J3.76 | PG_1V2_DDR | PSU.7 | - | 3.3VIN | O | - | Power Good for 1V2 DDR power supply regulator |

| J3.78 | EN_1V2_DDR | PSU.5 | - | 3.3VIN | I | - | Power Enable for 1V2 DDR power supply regulator |

| J3.80 | PG_2V5_PP | PSU.7 | - | 3.3VIN | O | - | Power Good for 2V5 power supply regulator |

| J3.82 | EN_2V5_PP | PSU.5 | - | 3.3VIN | I | - | Power Enable for 2V5 power supply regulator |

| J3.84 | PG_1V2_GTH | PSU.7 | - | 3.3VIN | O | - | Power Good for 1V2 GTH power supply regulator |

| J3.86 | EN_1V2_GTH | PSU.5 | - | VIN | I | - | Power Enable for 1V2 GTH power supply regulator |

| J3.88 | PG_1V8_AUX | PSU.7 | - | 3.3VIN | O | - | Power Good for 1V8 AUX power supply regulator |

| J3.90 | EN_1V8_AUX | PSU.5 | - | 3.3VIN | I | - | Power Enable for 1V8 AUX power supply regulator |

| J3.92 | PG_0V85_INT | - | - | 3.3VIN | O | - | Power Good for 0V85 power supply regulator |

| J3.94 | DGND | DGND | - | - | G | - | Digital ground |

| J3.96 | VDDIO_BANK43-44 | FPGA.VCCO_13 | AC10 AG12 AA14 AD13 |

Bank 43-44 | S | User defined | Bank43-44 I/O Power Supply |

| J3.98 | VDDIO_BANK43-44 | FPGA.VCCO_13 | AC10 AG12 AA14 AD13 |

Bank 43-44 | S | User defined | Bank43-44 I/O Power Supply |

| J3.100 | WDT_REARM | WD.WDI | 1 | 3.3VIN | I | - | Watchdog rearm pin |

| J3.102 | DGND | DGND | - | - | G | - | Digital ground |

| J3.104 | IO_L12P_AD8P_44 | FPGA.IO_L12P_AD8P_44 | Y12 | Bank 44 | I/O | User defined | |

| J3.106 | IO_L12N_AD8N_44 | FPGA.IO_L12N_AD8N_44 | AA12 | Bank 44 | I/O | User defined | |

| J3.108 | DGND | DGND | - | - | G | - | Digital ground |

| J3.110 | IO_L10P_AD10P_44 | FPGA.IO_L10P_AD10P_44 | Y14 | Bank 44 | I/O | User defined | |

| J3.112 | IO_L10N_AD10N_44 | FPGA.IO_L10N_AD10N_44 | Y13 | Bank 44 | I/O | User defined | |

| J3.114 | DGND | DGND | - | - | G | - | Digital ground |

| J3.116 | IO_L8P_HDGC_44 | FPGA.IO_L8P_HDGC_44 | AB15 | Bank 44 | I/O | User defined | |

| J3.118 | IO_L8N_HDGC_44 | FPGA.IO_L8N_HDGC_44 | AB14 | Bank 44 | I/O | User defined | |

| J3.120 | DGND | DGND | - | - | G | - | Digital ground |

| J3.122 | IO_L6P_HDGC_44 | FPGA.IO_L6P_HDGC_44 | AC14 | Bank 44 | I/O | User defined | |

| J3.124 | IO_L6N_HDGC_44 | FPGA.IO_L6N_HDGC_44 | AC13 | Bank 44 | I/O | User defined | |

| J3.126 | DGND | DGND | - | - | G | - | Digital ground |

| J3.128 | IO_L4P_AD12P_44 | FPGA.IO_L4P_AD12P_44 | AE13 | Bank 44 | I/O | User defined | |

| J3.130 | IO_L4N_AD12N_44 | FPGA.IO_L4N_AD12N_44 | AF13 | Bank 44 | I/O | User defined | |

| J3.132 | DGND | DGND | - | - | G | - | Digital ground |

| J3.134 | IO_L2P_AD14P_44 | FPGA.IO_L2P_AD14P_44 | AG14 | Bank 44 | I/O | User defined | |

| J3.136 | IO_L2N_AD14N_44 | FPGA.IO_L2N_AD14N_44 | AH14 | Bank 44 | I/O | User defined | |

| J3.138 | DGND | DGND | - | - | G | - | Digital ground |

| J3.140 | DGND | DGND | - | - | G | - | Digital ground |

Power and reset[edit | edit source]

Power Supply Unit (PSU) and recommended power-up sequence[edit | edit source]

Implementing a correct power-up sequence for Zynq Ultrascale+ processors is not a trivial task because several power rails are involved.

ONDA SOM simplifies this task by embedding all the needed circuitry. The following picture shows a simplified block diagram of PSU circuitry:

The PSU:

- consists of several regulators for each SOC power rail

- generates the proper power-up sequence required by the SOC processor and surrounding memories and peripherals

- synchronizes the powering up of the carrier board to prevent back power

- continuously checks the correct voltages of the various power rails

The picture also shows the control signals involved: for a detailed description see the chapter Reset scheme and control signals).

Power-up sequence[edit | edit source]

The recommended power-up sequence is:

- Carrier board generate main and auxiliary SOM power supply rails (VIN and 3.3VIN)

- Carrier board circuitry raises CB_PGOOD signal when VIN and 3.3VIN rails are stable (see note)

- ONDA's PSU enables and sequences DC/DC regulators to turn on the rails

- ONDA raises SOM_PGOOD signal; this active-high signal indicates that SoM's I/O is powered. This signal can be used to manage carrier board power up sequence in order to prevent back powering (from SoM to carrier board or vice versa)

- Finally, ONDA release PS_POR_B signal (see Reset scheme and control signals)

Please note that FPGA Bank 43, 43, 65 and 66 of the PL must be powered by carrier board, even if they are not used to implement any function. Three dedicated power rails are available for this purpose (VDDIO_BANK43-34, VDDIO_BANK65 and VDDIO_BANK66), offering the system designer the freedom to select the I/O voltage of these three banks. The power rails of these banks are enabled by the SOM_PGOOD signal and are connected to the I/O power supply rail provided by the carrier board.

N.B.: Regarding power off, it is recommended that I/O supply is turned off before core supply.

Cold reset[edit | edit source]

To force a cold reset, which shuts down all regulators on the SOM and restarts the power-up sequence, force the MRSTn signal to low for a few hundred of milliseconds.

Note on CB_PGOOD[edit | edit source]

The step 2 of power sequence is not mandatory and CB_PGOOD can be left floating.

CB_PGOOD is provided to prevent, if necessary, ONDA's PSU to turn on during ramp or glitch of VIN and 3.3VIN rails.

This signal is referenced to 3.3VIN auxiliary input PS; when the signal rises, the SoM power-up sequence begins.

Note on SOM_PGOOD[edit | edit source]

SOM_PGOOD signal rises about 4 ms after the last SoC rail is activated. Then, after about 2 ms, the PS_POR_B signal is release.

This signal is referenced to 3.3VIN auxiliary input PS.

Note on embedding power sequence circuitry[edit | edit source]

The sequential switching on of the different voltage regulators is controlled and monitored, for each rail, by a pair of signals called 'Power enable' and 'Power good': these pairs of signals can be monitored at connector J3.

Reset scheme and control signals[edit | edit source]

The following picture shows the simplified block diagram of PSU, reset and control signals:

Signals description[edit | edit source]

The electrical and functional characteristics of reset and control signals are listed in the following table:

| Signal | Type | Connector | Driven | Affect | Purpouse | Note | |

|---|---|---|---|---|---|---|---|

| MRSTn | Open drain,

User input |

10kΩ pull-up on ONDA

Refered to 3.3VIN rail |

J2.116 | Carrier | SOM PSU | ONDA performs COLD reset when MRSTn is asserted low. | |

| CB_PGOOD | Open drain,

User input |

10kΩ pull-up on ONDA

Refered to 3.3VIN rail |

J2.110 | Carrier | SOM PSU | ONDA initiates the power-up sequence when CB_PGOOD is released. | |

| SOM_PGOOD | Open drain,

User output |

10kΩ pull-up on ONDA

Refered to 3.3VIN rail |

J2.108 | SOM | Carrier PSU | ONDA indicates that the power sequence has been completed successfully.

The carrier can now turn on the power supply voltages for the PL banks and its peripherals connected to the SOM. |

|

| PWR_ENABLE_xx | User monitor | Refered to 3.3VIN rail | J3.35, J3.70, J3.74, J3.78,

J3.82, J3.86, J3.90 |

SOM PSU | - | Control signal that active the regulator on SOM. | See Pinout Table. |

| PWR_GOOD_xx | User monitor | Refered to 3.3VIN rail | J3.33, J3.72, J3.76, J3.80,

J3.84, J3.88, J3.92 |

SOM PSU | - | Indicates that the regulator's output voltage has reached the rated value. | See Pinout Table. |

| PS_POR_B | Open drain,

User output |

4k7Ω pull-up on ONDA

Refered to Bank503 rail (3.3V) |

J2.114 | SOM PSU | SoC & carrier | Zynq POR reset. This reset source does not cause a power cycle of SOM. | |

| WDT | SoC & carrier | ||||||

| PS_SRST_B | Open drain,

User input |

4k7Ω pull-up on ONDA

Refered to Bank503 rail (3.3V) |

J2.112 | Carrier | SoC | Zynq external system reset. This reset source does not cause a power cycle of SOM. | |

| SOM_PER_RSTn | Open drain,

User output |

10kΩ pull-up on ONDA

Refered to 1.8V |

J2.103 | SOM | SOM memories & PHYs

Carrier devices |

ONDA resets their memories and PHYs when PS_POR_B or PS_SRST_B is asserted low. | Can be use as an input. |

WDT[edit | edit source]

ONDA pairs the Zynq with a watchdog timer (WDT), Maxim MAX6373. The WDT output signal is connected to the PS_POR_B signal to trigger a warm reset if the timeout period is exceeded.

Whit a BOM variant, WDT can be trigger a cold reset by driving MRSTn signal: please contact sales dept. for more information.

For a detailed WDT description see the chapter Watchdog.

Clock scheme[edit | edit source]

ONDA is equipped with three independent active oscillators:

- processor (33.3 MHz)

- ethernet PHY (25 MHz)

- USB PHY (26 MHz)

Generally speaking, no clocks have to be provided by the carrier board.

PL initialization signals[edit | edit source]

This page provides information about the Programmable Logic (PL) initialization signals: PS_PROGRAM_B, PS_INIT_B, and PS_DONE.

Please refer to UltraScale Architecture PCB Design User Guide for more information about the usage and configuration of the initialization circuit and signals. As described in the link, the user can initialize the PL using these PS signals.

ONDA SOM signals are configured in the following way:

- PS_PROG_B has an internal 4k7 Ω pull-up

- PS_INIT_B has an internal 4k7 Ω pull-up

- PS_DONE has an internal 4k7 Ω pull-up. It does not require any external pull-up or pull-down but can be used for connecting a user led for a configuration completed indication (see for example ONDA EVK schematics).

These signals are referenced to the Bank 503 power rail, which operates at 3.3 V (see Processing System (PS) Bank Voltage).

System boot[edit | edit source]

In order to fully understand how boot works on the ONDA SOM, please refer to Chapter 11 ("Boot and configuration") of the Zynq UltraScale+ Device Technical Reference Manual (UG1085).

The BootROM can boot the system from Quad-SPI, SD, eMMC, USB 2.0 controller 0, or NAND external boot devices. All modes can be non-secure or be secure and signed except PS JTAG and PJTAG.

The system boot-up process is managed and carried out by the platform management unit (PMU) and configuration security unit (CSU). The boot-up process consists of three functional stages.

- Pre-configuration stage

- Configuration stage

- Post-configuration stage

The PMU performs a number of mandatory and optional security operation, the CSU is the central configuration processor that manages secure and non-secure system-level configuration.

After a system reset, the system automatically sequences to initialize the system and process the first stage boot loader from the selected external boot device.

Boot options[edit | edit source]

The boot ROM supports configuration from different slave interfaces, but not all of them are available in the ONDA SOM. Here below the list of available boot interface:

- PS JTAG

- onboard QSPI 32 bit NOR flash(es)

- SD1

- onboard eMMC

- USB

Boot mode is selectable via mode pins (PS_MODE[3:0]); here below the allowed boot modes

| Boot interface | BOOT_MODE[3..0] | Pin location |

|---|---|---|

| PS JTAG | 0000 | JTAG |

| QSPI NORE 32 bit | 0010 | MIO[12:00] |

| SD1 | 0101 | MIO[51:43] |

| eMMC | 0110 | MIO[22:13] |

| USB | 0111 | MIO[63:52] |

Default boot configuration for ONDA SOM is PS_MODE[3:0] = 0010 (QSPI 32-bit)

Boot sequence customization[edit | edit source]

PS_MODE[3:0] are routed to the J1 connector, enabling for the customization of the boot sequence through a simple resistor network that can be implemented on the carrier board hosting the ONDA SOM.

| Mode signal | J1 pin | Notes |

|---|---|---|

| PS_MODE[3] | J1.125 | PS_MODE pins, from Bank503, are powered @ 3V3

(BOM variant @ 1V8) |

| PS_MODE[2] | J1.121 | |

| PS_MODE[1] | J1.123 | |

| PS_MODE[0] | J1.119 |

JTAG[edit | edit source]

The Zynq UltraScale+ MPSoC JTAG interface provides 4-wire IEEE 1149.1 standard access (TCK, TMS, TDI, TDO) for debugging, programming, and boundary-scan, usually operating at 3.3V. It allows direct control over the Processing System (PS) and Programmable Logic (PL), supporting boot mode configuration (e.g., QSPI boot) and flash programming via tools like Vivado or Vitis.

JTAG signals are connected to the pinout connector (J2) on ONDA.

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| J2.80 | JTAG_TDO | - | - |

| J2.82 | JTAG_TDI | - | Internal 4k7 Ω pull-up |

| J2.84 | JTAG_TMS | - | Internal 4k7 Ω pull-up |

| J2.86 | JTAG_TCK | - | Internal 4k7 Ω pull-up |

| J2.90 | PS_INIT_B | - | For further details, please refer to PL initialization signals |

| J2.92 | PS_PROG_B | - | For further details, please refer to PL initialization signals |

| J2.94 | PS_DONE | - | For further details, please refer to PL initialization signals |

Peripherals[edit | edit source]

Processing System[edit | edit source]

PS_MIO pins are multiplexed I/O that can be configured to support multiple I/O interfaces. These interfaces include QSPI, USB, Ethernet, SDIO, CAN, UART, SPI, and GPIO interfaces.

The MIO module, on ONDA SOM, are assigned as reported in the following table:

| MIO Pins | Bank | VCC | Function/Peripheral | Notes |

|---|---|---|---|---|

| [0:5] | B500 | 1V8 | QSPI0 | Internal connection to QSPI NOR flash |

| [7:12] | B500 | QSPI1 | Internal connection to QSPI NOR flash | |

| [13:22] | B500 | SD0 interface (eMMC) | Internal connection to eMMC | |

| [24:25] | B500 | UART1 | UART console | |

| [38:39] | B501 | 1V8

(or 3V3 with a BOM variant) |

I²C1 | Internal connection to RTC, EEPROM, Temperature Monitor |

| [40:41] | B501 | CAN1 | Internal connection to CAN PHY (optional bypass) | |

| [43:51] | B501 | SD1 (MMC) | External SD interface (boot) | |

| [52:63] | B502 | 1V8 | USB0 | Internal connection to USB PHY |

| [64:75] | B502 | Gigabit Ethernet 3 (GEM3) | Internal connection to ethernet PHY | |

| [76] | B502 | MDC (ethernet Management Data Clock input) | ||

| [77] | B502 | MDIO (ethernet Management Data Input/Output) | ||

| 23 | B500 | 1V8 | available on J1 | |

| [27:29], [31:37] | B501 | 1V8

(or 3V3 with a BOM variant) |

|

|

| 6 | B500 | 1V8 | unused MIO | Not connected |

| 26,30,42,44 | B501 | 1V8

(or 3V3 with a BOM variant) |

unused MIO | Not connected |

GT transceiver[edit | edit source]

These page reports the GT transceiver characteristics.

Programmable logic[edit | edit source]

The following paragraphs describe in detail the available PL I/O signals and how they are routed to the ONDA connectors. The Zynq Ultrascale+ AP SoC is split into I/O banks to allow for flexibility in the choice of I/O standards, thus each table reports one bank configuration.

Moreover, ONDA design allows carrier board to power all three PL banks in order to achieve complete flexibility in terms of I/O voltage levels too.

For more details about PCB design considerations, please refer to the Advanced routing and carrier board design guidelines article.

The following table reports the I/O banks characteristics:

| ONDA bank | FPGA Bank | Bank power supply pins | I/O | Differentials Pairs | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Name | Type | External power rail | XCZU4 /

XCZU5 |

XCZU3T | XCZU2 | XCZU1 | XCZU4 /

XCZU5 |

XCZU3T | XCZU2 | XCZU1 | XCZU4 /

XCZU5 |

XCZU3T | XCZU2 | XCZU1 | |

| Bank 43 | HD | VDDIO_BANK43-44 | Bank 43 | - | Bank 44 | Bank 44 | J3.95 J3.96 J3.97 J3.98 J3.99 |

24 | - | 24 | 24 | 12 | - | 12 | 12 |

| Bank 44 | Bank 44 | Bank 44 | Bank 24 | - | 24 | 24 | 24 | - | 12 | 12 | 12 | - | |||

| Not connected | - | Bank 45 | Bank 45 | Bank 25 | - | - | - | - | - | - | - | - | - | - | |

| Not connected | - | Bank 46 | Bank 46 | Bank 26 | - | - | - | - | - | - | - | - | - | - | |

| Not connected | HP | - | Bank 64 | - | Bank 64 | Bank 64 | - | - | - | - | - | - | - | - | - |

| Bank 65 | VDDIO_BANK65 | Bank 65 | - | Bank 65 | Bank 65 | J1.2 J1.66 J1.67 J1.68 |

48 | - | 48 | 48 | 24 | - | 24 | 24 | |

| Bank 66 | VDDIO_BANK66 | Bank 66 | Bank 66 | Bank 66 | Bank 66 | 48 | 48 | 48 | 48 | 24 | 24 | 24 | 24 | ||

FPGA I/O Bank definitions:

- HD = High-density I/O with support for I/O voltage from 1.2V to 3.3V

- HP = High-performance I/O with support for I/O voltage from 1.0V to 1.8V

Max I/O[edit | edit source]

- Max HD I/O available on ONDA SOM is 48 (Bank 43 and Bank 44)

- Max HP I/O available on ONDA SOM is 96 (Bank 65 and Bank 66)

I/O naming[edit | edit source]

Each user I/O is labeled IO_Lxxy_Tmp_Nb_[opt]_##, where:

IOindicates a user I/O pin.Lindicates a differential pair, withxxa unique pair in the bank andy= [P|N] for the positive/negative sides of the differential pairTindicates the memory, withmthe byte group [0-3] andp= [U|L] Upper/Low portionNthe number within itsbbyte group [0 to 12]##indicates the bank number[opt]field can be:ADnnyindicates a withnna unique pair in the bank andy= [P|N] for the positive/negative sides of the differential pairGC/HDGCindicates a Global Clock (GC) having access to global clock buffers adjacent to the same I/O bank, and HDGC pins have direct access to the global clock buffersDBC/QBCindicates byte lane clock (DBC and QBC) input pin pairs (clock inputs directly driving source synchronous clocks)VRPindicates a DCI voltage reference resistor of P transistor

GT transceiver[edit | edit source]

The following table reports the GT transceiver characteristics:

| FPGA Bank | Domain | Type | Differentials Pairs | Clock pairs | |||

|---|---|---|---|---|---|---|---|

| XCZU4 /

XCZU5 |

XCZU3T | XCZU2 | XCZU1 | ||||

| Bank 505 | PS | GTR | 4 | 4 | 4 | 4 | 1 |

| Bank 224 | PL | GTH | 8 | 8 | - | - | 2 |

- GTR = PS-GTR receivers and transmitters supports up to 6.0Gb/s data rates (supports SGMII tri-speed Ethernet, PCI Express® Gen2, Serial-ATA (SATA), USB3.0, and DisplayPort™)

- GTH = PL-GTH transceiver, on ONDA the maximum data rates is up to 6.0Gb/s

Peripheral Ethernet[edit | edit source]

On-board gigabit Ethernet PHY (Microchip LAN8830) provides interface signals required to implement the 10/100/1000 Mbps Ethernet port. The transceiver is connected to the GEM3 Gigabit Ethernet Controller through the RGMII interface on MIO bank 502, pins PS_MIO[64:77]. For further details (eg: connection and selection of the magnetics), please refer to the Microchip LAN8830 datasheet.

The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| ETH_TXRX0_P | J1.105 | Media Dependent Interface[0], positive pin | - |

| ETH_TXRX0_N | J1.103 | Media Dependent Interface[0], negative pin | - |

| ETH_TXRX1_P | J1.99 | Media Dependent Interface[1], positive pin | - |

| ETH_TXRX1_N | J1.97 | Media Dependent Interface[1], negative pin | - |

| ETH_TXRX2_P | J1.102 | Media Dependent Interface[2], positive pin | - |

| ETH_TXRX2_N | J1.100 | Media Dependent Interface[2], negative pin | - |

| ETH_TXRX3_P | J1.96 | Media Dependent Interface[3], positive pin | - |

| ETH_TXRX3_N | J1.94 | Media Dependent Interface[3], negative pin | - |

| PS_MIO76_502 | J1.87 | ETH_MDIO Management Data Input/Output | - |

| PS_MIO77_502 | J1.89 | ETH_MDC Management Data Clock input | - |

| ETH_INTn | J1.90 | Ethernet PHY interrupt | - |

| ETH_LED1 | J1.91 | Activity LED | - |

| ETH_LED2 | J1.93 | Link LED | - |

| ETH_RSTn | J2.83 | Ethernet reset interrupt | PHY reset is also driven by RSTn SOM_PER_RSTn signal.

See Reset scheme and control signals page for more information |

Peripheral SDIO[edit | edit source]

The two SD/SDIO controller controllers are compatible with the standard SD Host Controller Specification Version 3.0. The controllers communicate with SDIO devices and SD memory cards with data transfers in 1-bit and 4-bit modes.

The SDIO Card Interface supports the maximum data rate in Standard mode (19 MHz), High-speed mode (50 MHz), SDR12 (25 MHz), SDR25 (50 MHz), SDR50 (100 MHz), SDR104 (200 MHz), DDR50 mode (50 MHz).

The following table describes the external ONDA interface signals for the SD card interface (MIO bank 501, pins PS_MIO[46:51] and optional PS_MIO[43], PS_MIO[45]):

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_MIO43_501 | J1.69 | SD/SDIO/MMC VBUS | VBUS (optional) pin |

| PS_MIO45_501 | J1.71 | SD/SDIO/MMC CD | Card detect (optional) pin |

| PS_MIO46_501 | J1.79 | SD/SDIO/MMC data 0 | - |

| PS_MIO47_501 | J1.77 | SD/SDIO/MMC data 1 | - |

| PS_MIO48_501 | J1.75 | SD/SDIO/MMC data 2 | - |

| PS_MIO49_501 | J1.73 | SD/SDIO/MMC data 3 | - |

| PS_MIO50_501 | J1.81 | SD/SDIO/MMC command | - |

| PS_MIO51_501 | J1.85 | SD/SDIO/MMC clock | - |

These signals are referenced to VCC_B501 (see dedicated section in the hardware manual).

Peripheral eMMC[edit | edit source]

The second SD/SDIO controller is used for interfacing the on-board eMMC and can operate at the maximum clock rate in Standard mode (25 MHz), High-speed SDR mode (50 MHz), High-Speed DDR mode (50 MHz), HS200 mode (200 MHz). The SD/SDIO controller supports MMC4.51.

The following table describes the external ONDA interface signals for the eMMC interface (MIO bank 500, pins PS_MIO[13:21]):

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_MIO13_500 | - | eMMC D0 | - |

| PS_MIO14_500 | - | eMMC D1 | - |

| PS_MIO15_500 | - | eMMC D2 | - |

| PS_MIO16_500 | - | eMMC D3 | - |

| PS_MIO17_500 | - | eMMC D4 | - |

| PS_MIO18_500 | - | eMMC D5 | - |

| PS_MIO19_500 | - | eMMC D6 | - |

| PS_MIO20_500 | - | eMMC D7 | - |

| PS_MIO21_500 | - | eMMC CMD | - |

| PS_MIO22_500 | - | eMMC CLK | - |

Peripheral QSPI[edit | edit source]

The two Quad-SPI controllers are configured to operate in a dual SS parallel configuration with two NOR SPI memory devices (bootable storage).

The controller supports up to two SPI flash memories operating in parallel: in this configuration, the maximum addressable SPI flash memory is 32 MB (25-bit address).

The following table describes the interface signals (MIO bank 500, pins PS_MIO[00:12]):

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_MIO00_500 | - | QSPI0 serial clock | NOR0 SCK |

| PS_MIO01_500 | - | QSPI0 IO1 | NOR0 IO pin 1 |

| PS_MIO02_500 | - | QSPI0 IO2 | NOR0 IO pin 2 |

| PS_MIO03_500 | - | QSPI0 IO3 | NOR0 IO pin 3 |

| PS_MIO04_500 | - | QSPI0 IO0 | NOR0 IO pin 0 |

| PS_MIO05_500 | - | QSPI0 chip select | NOR0 CS# |

| PS_MIO07_500 | - | QSPI1 chip select | NOR1 CS# |

| PS_MIO08_500 | - | QSPI1 IO0 | NOR1 IO pin 0 |

| PS_MIO09_500 | - | QSPI1 IO1 | NOR1 IO pin 1 |

| PS_MIO010_500 | - | QSPI1 IO2 | NOR1 IO pin 2 |

| PS_MIO011_500 | - | QSPI1 IO3 | NOR1 IO pin 3 |

| PS_MIO012_500 | - | QSPI1 serial clock | NOR1 SCK |

Peripheral CAN[edit | edit source]

ONDA provides full CAN 2.0B-compliant CAN bus interfaces 2.0-A, 2.0-B and ISO 118981-1.

The CAN port is connected to the on-board transceiver (TI SN65HVD232) which converts the controller's single-ended CAN signals into the differential signals of the physical layer. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| CAN_STBYn | J2.87 | CAN stand-by | PHY pin 8 STB signal - active low |

| CAN_H | J2.107 | High bus output | - |

| CAN_L | J2.105 | Low bus output | - |

Optionally, the on-board TCAN3413 CAN PHY transceiver can be excluded (for example, to use an external PHY on the carrier board) and the single-ended CAN signals are routed to the connectors. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_MIO41_501 | J2.105 | Receive data pin | - |

| PS_MIO40_501 | J2.107 | Transmit data pin | - |

These signals are referenced to VCC_B501 (see dedicated section in the hardware manual).

Contact our Sales Department for more information about this hardware option.

Peripheral I2C[edit | edit source]

This I²C module is a bus controller that can function as a master or a slave in a multi-master design. It supports an extremely wide clock frequency range up to 400 Kb/s.

An internal voltage level translator allows the use of MIO Bank 501 signals with a different voltage level than the internal 3V3-powered devices: the I²C0 is internally connected to the following devices:

- Temperature_Monitor: Texas Instruments TMP421 (Address: 0x4F)

- Real Time Clock: Maxim Integrated DS3232M (Address: 0x68)

The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_MIO39_501 | J1.84 | I2C SDA | - |

| PS_MIO38_501 | J1.88 | I2C SCL | - |

These signals are referenced to VCC_B501 (see dedicated section in the hardware manual).

Peripheral UART[edit | edit source]

The UART controller is a full-duplex asynchronous receiver and transmitter that supports a wide range of programmable baud rates and I/O signal formats. UART1 port is routed to the SOM connectors as a 2-wire interface. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_MIO25_500 | J1.80 | UART RX | - |

| PS_MIO24_500 | J1.82 | UART TX | - |

These signals are referenced to VCC_B500 (see dedicated section in the hardware manual).

Peripheral USB[edit | edit source]

ONDA provides one USB 2.0 (Full Speed, up to 480 Mbps) port with on-board USB3317 PHY Hi-Speed and support to the On-The-Go (OTG) specifications. The transceiver is connected to the USB1 controller (MIO bank 502, pins PS_MIO[52:63]). The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| USB_D_P | J1.114 | D+ pin of the USB cable | - |

| USB_D_N | J1.116 | D- pin of the USB cable | - |

| USB_CPEN | J1.111 | External 5 volt supply enable | This pin is used to enable the external VBUS power supply |

| USB_VBUS | J1.113 | VBUS pin of the USB cable | - |

| USB_ID | J1.115 | ID pin of the USB cable | For non-OTG applications this pin can be floated. For an A-device ID is grounded. For a B-device ID is floated. |

These signals are referenced to VCC_B501 (see dedicated section in the hardware manual).

Peripheral RTC[edit | edit source]

An on-board Maxim Integrated DS3232M device provides a very accurate, temperature-compensated real-time clock (RTC) resource with:

- Temperature-compensated crystal oscillator

- Date, time and calendar

- Alarm capability

- Backup power from external battery

- ±3.5ppm accuracy from -40°C to +85°C

- 236 Bytes of Battery-Backed SRAM

- I²C Interface

For a detailed description of RTC characteristics, please refer to the DS3232M datasheet.

Signals[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| J2.93 | RTC_32KHZ | 32.768kHz output | - |

| J2.95 | RTC_RSTn | active-low reset | open-drain input/output |

| J2.111 | RTC_INTn/SQW | active-Low Interrupt or 1Hz Square-Wave Output | It can be left open if not used. |

| J2.113 | RTC_VBAT | Backup power | If not used, RTC_VBAT must be externally connected to GND |

These signals are referenced to 3.3VIN auxiliary input PS.

Default configuration[edit | edit source]

MAX6373 timeout is pin-selectable. It can be configured through the WDT_SET0, WDT_SET1 and WDT_SET2 signals. By default, they are configured as follows:

- WD_SET2 = 0

- WD_SET1 = 1

- WD_SET0 = 1

This set selects the option disabled(the exhaustive list of configurations options is descripted on MAX6373 page 4 datasheet):

Watchdog signals[edit | edit source]

Watchdog signals are connected to the pinout connector (J2 and J3) on ONDA.

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| J2.96 | WDT_SET2 | SET2 | Internal 10K Ω pull-down |

| J2.98 | WDT_SET1 | SET1 | Internal 10K Ω pull-up |

| J2.100 | WDT_SET0 | SET0 | Internal 10K Ω pull-up |

| J3.100 | WDT_REARM | WDI | Internal 10K Ω pull-down |

| J2.114 | PS_POR_B | WDO | For further details, please refer to Reset_scheme_and_control_signals

WDO can be optionally connected to the MRSTn signal (J2.116 pin): contact sales dept. for more information. |

When the watchdog is started, the software (bootloader/operating system) must take care of toggling the watchdog trigger pin (WDI) before the timeout expiration.

Selecting different configurations[edit | edit source]

Since WD_SETx signals are routed externally, WDT configuration can be changed by optional circuitry implemented on the carrier board. Different solutions can be implemented on the carrier board, depending on system requirements. The easiest circuit consists of additional stronger pull-up/down resistors connected to WDT_SETx pins in order to overrule default configuration. As MAX6373 allows to change the configuration during operation, more complex solutions can be implemented as well.

Peripheral Temperature Monitor[edit | edit source]

An on-board thermal IC (Texas Instruments TMP421) connected to the I²C interface can work as a local temperature sensor, providing the measurement of its internal temperature, but also as a remote temperature sensor, since it is connected to the XADC_DXP/XADC_DXN of the Zynq processor, providing the measurement of the Zynq internal temperature.

For a detailed description of the thermal IC characteristics, please refer to the TMP421 datasheet.

Electrical, Thermal and Mechanical Features[edit | edit source]

Operational characteristics[edit | edit source]

Absolute Maximum ratings[edit | edit source]

| Parameter | Min | Typ | Max | Unit |

|---|---|---|---|---|

| Main power supply voltage | -0.3 | 3.3 or 5 | 6 | V |

| Auxiliary power supply voltage | -0.3 | 3.3 | 3.6 | V |

Recommended ratings[edit | edit source]

| Parameter | Min | Typ | Max | Unit |

|---|---|---|---|---|

| Main power supply voltage | 3.1 | 3.3 or 5 | 5.5 | V |

| Auxiliary power supply voltage | 3.135 | 3.3 | 3.465 | V |

Programmable Logic (PL) Bank Voltage support[edit | edit source]

The power supplies of PL banks are provided by the carrier board.

Please refer to the dedicated section in the hardware manual for PL Voltage levels.

Processing System (PS) Bank Voltage support[edit | edit source]

The PS bank are powered by the SOM.

Please refer to the dedicated section in the hardware manual for PS Voltage levels.

Power consumption[edit | edit source]

Providing a theoretical maximum power consumption value would be useless for the majority of system designers building their application upon ONDA SOM because, in most cases, this would lead to an oversized power supply unit.

Please note that ONDA platform is so flexible that it is virtually impossible to test for all possible configurations and applications on the market.

Generally speaking, application-specific requirements must be taken into account to properly design the power supply unit and to implement the thermal management.

Mechanical specifications[edit | edit source]

This chapter describes the mechanical characteristics of the ONDA module.

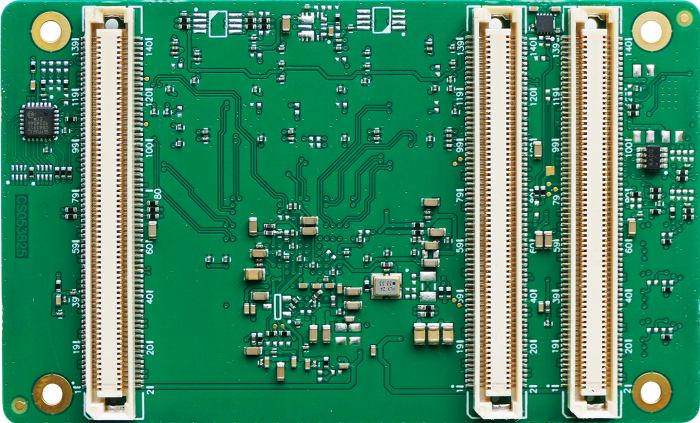

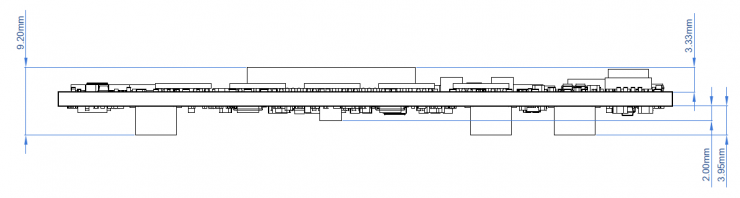

Board Layout[edit | edit source]

The following figure shows the physical dimensions of the ONDA module:

The following figure highlights the maximum components' heights (expressed in mm) in the ONDA SOM:

CAD drawings[edit | edit source]

3D drawings[edit | edit source]