ORCA SOM/ORCA Hardware/pdf

Contents

- 1 General Information

- 2 Pinout Table

- 3 Power and reset

- 4 Peripherals

- 4.1 Peripheral Audio

- 4.2 Peripheral CAN

- 4.3 Peripheral HDMI

- 4.4 Peripheral LVDS

- 4.5 Peripheral MIPI

- 4.6 Peripheral ISP

- 4.7 Peripheral SDIOs

- 4.8 Peripheral SPI

- 4.9 Peripheral I2C

- 4.10 Peripheral UART

- 4.11 Peripheral USB

- 4.12 Peripheral PCI Express

- 4.13 Peripheral GPIOs

- 4.14 Real Time Clock

- 4.15 Peripheral Watchdog

- 4.16 Peripheral Secure Element

- 5 Electrical, Thermal and Mechanical Features

General Information[edit | edit source]

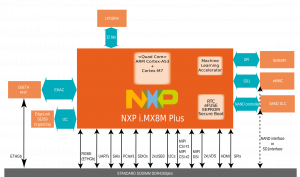

ORCA Block Diagram[edit | edit source]

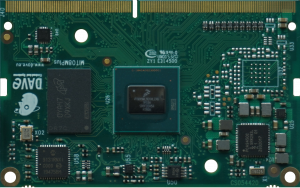

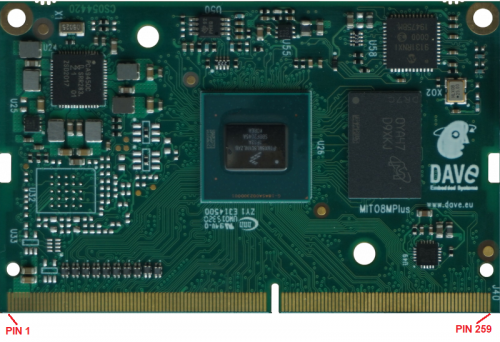

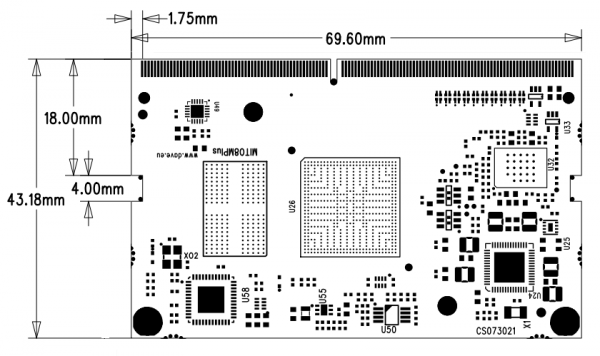

ORCA TOP View[edit | edit source]

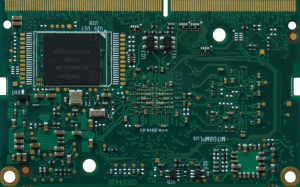

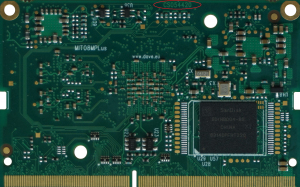

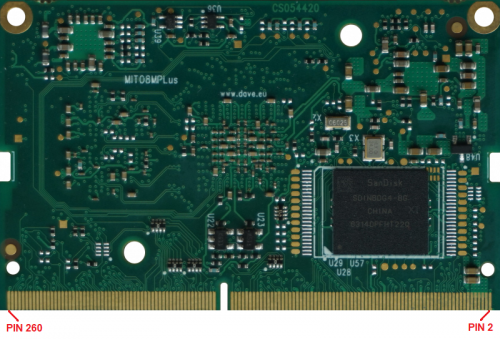

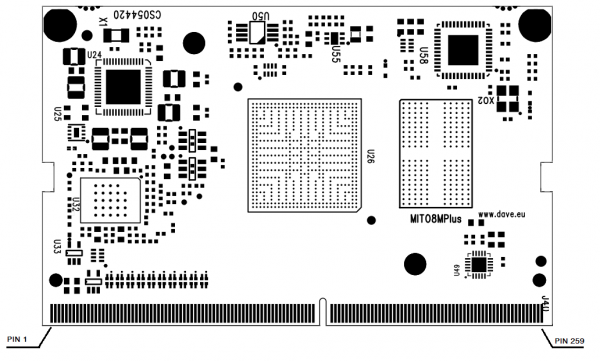

ORCA BOTTOM View[edit | edit source]

Processor and memory subsystem[edit | edit source]

The heart of ORCA module is composed by the following components:

- i.MX8M Plus SoC application processor

- Power supply unit

- LPDDR4 memory bank

- eMMC or NAND flash banks

- Connectors:

- 1 x 260 pins SO-DIMM edge connector with interfaces signals

This chapter shortly describes the main ORCA components.

Processor Info[edit | edit source]

| Processor | i.MX8M Plus Dual | i.MX8M Plus Quad |

| # Cores | 2x Arm® Cortex®-A53 1x Arm® Cortex®-M7 1x Hi-Fi4 DSP |

4x Arm® Cortex®-A53 1x Arm® Cortex®-M7 1x Hi-Fi4 DSP |

| Clock | 1.8 GHz | |

| L2 Cache | 512 KB | |

| LPDDR4 | 32 bit @ 2000 MHz (LPDDR4-4000) | |

| GPU | 3D: Vivante GC 7000UL (2 Shader) 2D: Vivante GC520L OpenGL ES 3.1 | |

| VPU | 1080p60 H.265, H.264, VP9, VP8 decoder 1080p60 H.265, H.264 encoder | |

| NPU | 2.25 TOP/s Neural Processing Unit | |

| Display Controller | Dual Channel LVDS up to 1080p60 | |

| Video Output | 1x HDMI 2.0a 1x MIPI-DSI (4-lanes) | |

| Camera Input | 2x MIPI CSI (4-lanes each) 2x ISP | |

| Ethernet | 2x 10/100/1000 Mbit/s controller with AVB and IEEE1588 | |

| PCIe | 1x PCIe 3 (1-lane) | |

| USB | 2x USB 2.0/3.0 | |

RAM memory bank[edit | edit source]

LPDD4 SDRAM memory bank is composed by 1x 32-bit width chip. The following table reports the SDRAM specifications:

| CPU connection | Multi-mode DDR controller (MMDC) |

| Size max | 8 GB |

| Width | 32 bit |

| Speed | 2000 MHz |

eMMC flash bank[edit | edit source]

On board main storage memory eMMC is connected to the SDIO3 interface and it can act as boot peripheral. The following table reports the eMMC flash specifications:

| CPU connection | SDIO3 |

| Size min | 4 GB |

| Size max | 64 GB |

| Bootable | Yes |

NAND flash bank[edit | edit source]

| Section not completed yet |

Alternative option for main storage memory can be a 8-bit wide NAND flash connected to the CPU's Raw NAND flash controller. It can act as boot peripheral. The following table reports the NAND flash specifications:

| CPU connection | Raw NAND flash controller |

| Page size | TBD |

| Size min | TBD |

| Size max | TBD |

| Width | 8 bit |

| Chip select | TBD |

| Bootable | Yes |

Memory map[edit | edit source]

For detailed information, please refer to chapter 2 “Memory Maps” of the i.MX8M Plus Applications Processor Reference Manual

Power supply unit[edit | edit source]

ORCA embeds all the elements required for powering the unit, therefore power sequencing is self-contained and simplified. Nevertheless, power must be provided from carrier board, and therefore users should be aware of the ranges power supply can assume as well as all other parameters.

Hardware versioning and tracking[edit | edit source]

ORCA SOM implements well established versioning and tracking mechanisms:

- PCB version is copper printed on PCB itself, as shown in Fig. 1

- serial number: it is printed on a white label, as shown in Fig. 2: see also Product serial number page for more details

- ConfigID: it is used by software running on the board for the identification of the product model/hardware configuration. For more details, please refer to this link

- On ORCA SOM ConfigID is stored on OTP memory

Part number composition[edit | edit source]

ORCA SOM module part number is identified by the following digit-code table:

| Part number structure | Options | Description |

|---|---|---|

| Family | DMU | Family prefix code |

| SOC |

|

Other versions can be available, please contact technical support |

| RAM |

|

|

| Storage eMMC/NAND/QSPI |

|

NAND SLC and eMMC are possible alternatives not available together. QSPI can be mounted or not. Other versions can be available, please contact technical support |

| Mounting Options |

|

Other versions can be available, please contact technical support |

| RFU |

|

|

| Temperature range |

|

Other versions can be available, please contact technical support For the DAVE Embedded Systems' product Temperature Range classification, please find more information at the page Products Classification |

| PCB revision |

|

PCB release may change for manufacturing purposes (i.e. text fixture adaptation) |

| Manufacturing option |

|

typically connected to production process and quality |

| Software Configuration |

|

If customers require custom SW deployed this section should be defined and agreed. Please contact technical support |

Example[edit | edit source]

ORCA SOM code DMUA3300M2R-00

- DMU - ORCA SOM

- A - MIMX8ML8CVNKZAB (i.MX 8M Plus Quad - Quad Core, VPU, NPU, ISP, CAN-FD - 1.6 GHz - Industrial - Tj=-40/105°C)

- 2 - 6GB DDR4

- 3 - 8GB eMMC, No QSPI, No NAND

- 0 - EdgeLock SE050, 32.768K X2, Voltage monitor, SD1 interface @ 3V3

- 0 - RFU

- M - Extended commercial grade: -20 to +70°C

- 2 - revision B

- R - RoHS compliant

- -00 - MAC address only

Pinout Table[edit | edit source]

Connectors and Pinout Table[edit | edit source]

Connectors description[edit | edit source]

In the following table are described all available connectors integrated on ORCA SOM:

| Connector name | Connector Type | Notes | Carrier board counterpart |

|---|---|---|---|

| J1 | SODIMM DDR4 edge connector 260 pin | TE Connectivity 2309407-1 |

The dedicated carrier board must mount the mating connector and connect the desired peripheral interfaces according to ORCA pinout specifications. See the images below for reference:

Pinout table naming conventions[edit | edit source]

This chapter contains the pinout description of the ORCA module, grouped in two tables (odd and even pins) that report the pin mapping of the 260-pin DDR4 SO-DIMM ORCA connector.

Each row in the pinout tables contains the following information:

| Pin | Reference to the connector pin |

| Pin Name | Pin (signal) name on the ORCA connectors |

| Internal connections |

Connections to the ORCA components

|

| Ball/pin # | Component ball/pin number connected to signal |

| Voltage | I/O voltage levels |

| Type | Pin type:

|

| Notes | Remarks on special pin characteristics |

| Pin MUX alternative functions | Muxes:

The number of functions depends on platform |

Pinout Table ODD pins declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Voltage domain | Type | Notes | Alternative Functions | |

|---|---|---|---|---|---|---|---|---|

| J1.1 | DGND | DGND | - | - | G | |||

| J1.3 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.5 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.7 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.9 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.11 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.13 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.15 | CPU_ONOFF | CPU.ONOFF | G22 | NVCC_SNVS_1V8 | I/O | internal pull-up 100k to NVCC_SNVS_1V8 | ||

| J1.17 | CPU_PORn | CPU.POR_B

PMIC.POR_B |

J29

9 |

NVCC_SNVS_1V8 | I/O | internal pull-up 100k to NVCC_SNVS_1V8 | ||

| J1.19 | PMIC_ON_REQ

//VMON_RST |

CPU.PMIC_ON_REQ

PMIC.PMIC_ON_REQ |

F22

39 |

NVCC_SNVS_1V8 | I/O | more information on Reset scheme page | ||

| J1.21 | PMIC_RST_B | PMIC.PMIC_RST_B | 8 | NVCC_SNVS_1V8 | I/O | internal pull-up 100k to NVCC_SNVS_1V8 | ||

| J1.23 | BOARD_PGOOD | MTR.RESET_B | 2 | NVCC_3V3 | O | |||

| J1.25 | BOOT_MODE0 | CPU.BOOT_MODE0 | G10 | NVCC_3V3 | I | internal 10k pull-up or pull-down

according to specific model |

||

| J1.27 | BOOT_MODE1 | CPU.BOOT_MODE1 | F8 | NVCC_3V3 | I | internal 10k pull-up or pull-down

according to specific model |

||

| J1.29 | BOOT_MODE2 | CPU.BOOT_MODE2 | G8 | NVCC_3V3 | I | internal 10k pull-up or pull-down

according to specific model |

||

| J1.31 | DGND | DGND | - | - | G | |||

| J1.33 | LVDS0_D3_N | CPU.LVDS0_D3_N | J28 | - | D | |||

| J1.35 | LVDS0_D3_P | CPU.LVDS0_D3_P | H29 | - | D | |||

| J1.37 | LVDS0_D2_N | CPU.LVDS0_D2_N | H28 | - | D | |||

| J1.39 | LVDS0_D2_P | CPU.LVDS0_D2_P | G29 | - | D | |||

| J1.41 | LVDS0_CLK_N | CPU.LVDS0_CLK_N | G28 | - | D | |||

| J1.43 | LVDS0_CLK_P | CPU.LVDS0_CLK_P | F29 | - | D | |||

| J1.45 | LVDS0_D1_N | CPU.LVDS0_D1_N | F28 | - | D | |||

| J1.47 | LVDS0_D1_P | CPU.LVDS0_D1_P | E29 | - | D | |||

| J1.49 | LVDS0_D0_N | CPU.LVDS0_D0_N | E28 | - | D | |||

| J1.51 | LVDS0_D0_P | CPU.LVDS0_D0_P | D29 | - | D | |||

| J1.53 | DGND | DGND | - | - | G | |||

| J1.55 | LVDS1_D3_N | CPU.LVDS1_D3_N | D28 | - | D | |||

| J1.57 | LVDS1_D3_P | CPU.LVDS1_D3_P | C29 | - | D | |||

| J1.59 | LVDS1_D2_N | CPU.LVDS1_D2_N | C28 | - | D | |||

| J1.61 | LVDS1_D2_P | CPU.LVDS1_D2_P | B29 | - | D | |||

| J1.63 | LVDS1_CLK_N | CPU.LVDS1_CLK_N | B28 | - | D | |||

| J1.65 | LVDS1_CLK_P | CPU.LVDS1_CLK_P | A28 | - | D | |||

| J1.67 | LVDS1_D1_N | CPU.LVDS1_D1_N | B27 | - | D | |||

| J1.69 | LVDS1_D1_P | CPU.LVDS1_D1_P | A27 | - | D | |||

| J1.71 | LVDS1_D0_N | CPU.LVDS1_D0_N | B26 | - | D | |||

| J1.73 | LVDS1_D0_P | CPU.LVDS1_D0_P | A26 | - | D | |||

| J1.75 | DGND | DGND | - | - | G | |||

| J1.77 | MIPI_CSI2_D0_P | CPU.MIPI_CSI2_D0_P | A25 | - | D | |||

| J1.79 | MIPI_CSI2_D0_N | CPU.MIPI_CSI2_D0_N | B25 | - | D | |||

| J1.81 | MIPI_CSI2_D1_P | CPU.MIPI_CSI2_D1_P | A24 | - | D | |||

| J1.83 | MIPI_CSI2_D1_N | CPU.MIPI_CSI2_D1_N | B24 | - | D | |||

| J1.85 | MIPI_CSI2_CLK_P | CPU.MIPI_CSI2_CLK_P | A23 | - | D | |||

| J1.87 | MIPI_CSI2_CLK_N | CPU.MIPI_CSI2_CLK_N | B23 | - | D | |||

| J1.89 | MIPI_CSI2_D2_P | CPU.MIPI_CSI2_D2_P | A22 | - | D | |||

| J1.91 | MIPI_CSI2_D2_N | CPU.MIPI_CSI2_D2_N | B22 | - | D | |||

| J1.93 | MIPI_CSI2_D3_P | CPU.MIPI_CSI2_D3_P | A21 | - | D | |||

| J1.95 | MIPI_CSI2_D3_N | CPU.MIPI_CSI2_D3_N | B21 | - | D | |||

| J1.97 | DGND | DGND | - | - | G | |||

| J1.99 | MIPI_CSI1_D3_P | CPU.MIPI_CSI1_D3_P | D26 | - | D | |||

| J1.101 | MIPI_CSI1_D3_N | CPU.MIPI_CSI1_D3_N | E26 | - | D | |||

| J1.103 | MIPI_CSI1_D2_P | CPU.MIPI_CSI1_D2_P | D24 | - | D | |||

| J1.105 | MIPI_CSI1_D2_N | CPU.MIPI_CSI1_D2_N | E24 | - | D | |||

| J1.107 | MIPI_CSI1_CLK_P | CPU.MIPI_CSI1_CLK_P | D22 | - | D | |||

| J1.109 | MIPI_CSI1_CLK_N | CPU.MIPI_CSI1_CLK_N | E22 | - | D | |||

| J1.111 | MIPI_CSI1_D1_P | CPU.MIPI_CSI1_D1_P | D20 | - | D | |||

| J1.113 | MIPI_CSI1_D1_N | CPU.MIPI_CSI1_D1_N | E20 | - | D | |||

| J1.115 | MIPI_CSI1_D0_P | CPU.MIPI_CSI1_D0_P | D18 | - | D | |||

| J1.117 | MIPI_CSI1_D0_N | CPU.MIPI_CSI1_D0_N | E18 | - | D | |||

| J1.119 | DGND | DGND | - | - | G | |||

| J1.121 | MIPI_DSI1_D3_P | CPU.MIPI_DSI1_D3_P | A20 | - | D | |||

| J1.123 | MIPI_DSI1_D3_N | CPU.MIPI_DSI1_D3_N | B20 | - | D | |||

| J1.125 | MIPI_DSI1_D2_P | CPU.MIPI_DSI1_D2_P | A19 | - | D | |||

| J1.127 | MIPI_DSI1_D2_N | CPU.MIPI_DSI1_D2_N | B19 | - | D | |||

| J1.129 | MIPI_DSI1_CLK_P | CPU.MIPI_DSI1_CLK_P | A18 | - | D | |||

| J1.131 | MIPI_DSI1_CLK_N | CPU.MIPI_DSI1_CLK_N | B18 | - | D | |||

| J1.133 | MIPI_DSI1_D1_P | CPU.MIPI_DSI1_D1_P | A17 | - | D | |||

| J1.135 | MIPI_DSI1_D1_N | CPU.MIPI_DSI1_D1_N | B17 | - | D | |||

| J1.137 | MIPI_DSI1_D0_P | CPU.MIPI_DSI1_D0_P | A16 | - | D | |||

| J1.139 | MIPI_DSI1_D0_N | CPU.MIPI_DSI1_D0_N | B16 | - | D | |||

| J1.141 | DGND | DGND | - | - | G | |||

| J1.143 | JTAG_MOD | CPU.JTAG_MOD | G20 | NVCC_3V3 | I/O | |||

| J1.145 | JTAG_TCK | CPU.JTAG_TCK | G18 | NVCC_3V3 | I/O | |||

| J1.147 | JTAG_TDI | CPU.JTAG_TDI | G16 | NVCC_3V3 | I | |||

| J1.149 | JTAG_TMS | CPU.JTAG_TMS | G14 | NVCC_3V3 | I/O | |||

| J1.151 | JTAG_TDO | CPU.JTAG_TDO | F14 | NVCC_3V3 | O | |||

| J1.153 | DGND | DGND | - | - | G | |||

| J1.155 | PCIE_REF_PAD_CLK_P | CPU.PCIE_REF_PAD_CLK_P | D16 | - | D | |||

| J1.157 | PCIE_REF_PAD_CLK_N | CPU.PCIE_REF_PAD_CLK_N | E16 | - | D | |||

| J1.159 | PCIE_TXN_P | CPU.PCIE_TXN_P | A15 | - | D | |||

| J1.161 | PCIE_TXN_N | CPU.PCIE_TXN_N | B15 | - | D | |||

| J1.163 | PCIE_RXN_P | CPU.PCIE_RXN_P | A14 | - | D | |||

| J1.165 | PCIE_RXN_N | CPU.PCIE_RXN_N | B14 | - | D | |||

| J1.167 | DGND | DGND | - | - | G | |||

| J1.169 | USB2_VBUS | USB2_VBUS | - | - | S | See USB section for details (5-20V tolerance) | ||

| J1.171 | DNU | DNU | - | - | - | DNU stands for Do Not Use.

This pin must be left unconnected/floating. |

||

| J1.173 | USB2_D_P | CPU.USB2_D_P | D14 | - | D | |||

| J1.175 | USB2_D_N | CPU.USB2_D_N | E14 | - | D | |||

| J1.177 | DGND | DGND | - | - | G | |||

| J1.179 | USB2_TX_P | CPU.USB2_TX_P | A13 | - | D | |||

| J1.181 | USB2_TX_N | CPU.USB2_TX_N | B13 | - | D | |||

| J1.183 | USB2_RX_P | CPU.USB2_RX_P | A12 | - | D | |||

| J1.185 | USB2_RX_N | CPU.USB2_RX_N | B12 | - | D | |||

| J1.187 | DGND | DGND | - | - | G | |||

| J1.189 | USB1_VBUS | USB1_VBUS | - | - | S | See USB section for details (5-20V tolerance) | ||

| J1.191 | ETH0_INTn | LAN.INT_N/PME_N2 | 38 | VDD_1V8 | O | Must be level translated if used @ 3V3

Internally pulled-up to 1.8V |

||

| J1.193 | USB1_D_P | CPU.USB1_D_P | D10 | - | D | |||

| J1.195 | USB1_D_N | CPU.USB1_D_N | E10 | - | D | |||

| J1.197 | DGND | DGND | - | - | G | |||

| J1.199 | USB1_TX_P | CPU.USB1_TX_P | A10 | - | D | |||

| J1.201 | USB1_TX_N | CPU.USB1_TX_N | B10 | - | D | |||

| J1.203 | USB1_RX_P | CPU.USB1_RX_P | A9 | - | D | |||

| J1.205 | USB1_RX_N | CPU.USB1_RX_N | B9 | - | D | |||

| J1.207 | DGND | DGND | - | - | G | |||

| J1.209 | GPIO1_IO08 | CPU.GPIO1_IO08 | A8 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO08 | |

| Pin ALT-1 | ENET_QOS_1588_EVENT0_IN | |||||||

| Pin ALT-2 | PWM1_OUT | |||||||

| Pin ALT-3 | ISP_PRELIGHT_TRIG_1 | |||||||

| Pin ALT-4 | ENET_QOS_1588_EVENT0_AUX_IN | |||||||

| Pin ALT-5 | USDHC2_RESET_B | |||||||

| J1.211 | GPIO1_IO11 | CPU.GPIO1_IO11 | D8 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO11 | |

| Pin ALT-1 | USB2_OTG_ID | |||||||

| Pin ALT-2 | PWM2_OUT | |||||||

| Pin ALT-4 | USDHC3_VSELECT | |||||||

| Pin ALT-5 | CCM_PMIC_READY | |||||||

| J1.213 | GPIO1_IO09 | CPU.GPIO1_IO09 | B8 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO09 | |

| Pin ALT-1 | ENET_QOS_1588_EVENT0_OUT | |||||||

| Pin ALT-2 | PWM2_OUT | |||||||

| Pin ALT-3 | ISP_SHUTTER_OPEN_1 | |||||||

| Pin ALT-4 | USDHC3_RESET_B | |||||||

| Pin ALT-5 | SDMA2_EXT_EVENT00 | |||||||

| J1.215 | GPIO1_IO00 | CPU.GPIO1_IO00 | A7 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO00 | |

| Pin ALT-1 | CCM_ENET_PHY_REF_CLK_ROOT | |||||||

| Pin ALT-3 | ISP_FL_TRIG_0 | |||||||

| Pin ALT-6 | CCM_EXT_CLK1 | |||||||

| J1.217 | GPIO1_IO01 | CPU.GPIO1_IO01 | E8 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO01 | |

| Pin ALT-1 | PWM1_OUT | |||||||

| Pin ALT-3 | ISP_SHUTTER_TRIG_0 | |||||||

| Pin ALT-6 | CCM_EXT_CLK2 | |||||||

| J1.219 | GPIO1_IO10 | CPU.GPIO1_IO10 | B7 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO10 | |

| Pin ALT-1 | USB1_OTG_ID | |||||||

| Pin ALT-2 | PWM3_OUT | |||||||

| J1.221 | GPIO1_IO13 | CPU.GPIO1_IO13 | A6 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO13 | |

| Pin ALT-1 | USB1_OTG_OC | |||||||

| Pin ALT-5 | PWM2_OUT | |||||||

| J1.223 | GPIO1_IO12 | CPU.GPIO1_IO12 | A5 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO12 | |

| Pin ALT-1 | USB1_OTG_PWR | |||||||

| Pin ALT-5 | SDMA2_EXT_EVENT01 | |||||||

| J1.225 | GPIO1_IO07 | CPU.GPIO1_IO07 | F6 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO07 | |

| Pin ALT-1 | ENET_QOS_MDIO | |||||||

| Pin ALT-3 | ISP_FLASH_TRIG_1 | |||||||

| Pin ALT-5 | USDHC1_WP | |||||||

| Pin ALT-6 | CCM_EXT_CLK4 | |||||||

| J1.227 | GPIO1_IO15 | CPU.GPIO1_IO15 | B5 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO15 | |

| Pin ALT-1 | USB2_OTG_OC | |||||||

| Pin ALT-4 | USDHC3_WP | |||||||

| Pin ALT-5 | PWM4_OUT | |||||||

| Pin ALT-6 | CCM_CLKO2 | |||||||

| J1.229 | GPIO1_IO14 | CPU.GPIO1_IO14 | A4 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO14 | |

| Pin ALT-1 | USB2_OTG_PWR | |||||||

| Pin ALT-4 | USDHC3_CD_B | |||||||

| Pin ALT-5 | PWM3_OUT | |||||||

| Pin ALT-6 | CCM_CLKO1 | |||||||

| J1.231 | GPIO1_IO05 | CPU.GPIO1_IO05 | B4 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO05 | |

| Pin ALT-1 | M7_NMI | |||||||

| Pin ALT-3 | ISP_FL_TRIG_1 | |||||||

| Pin ALT-6 | CCM_PMIC_READY | |||||||

| J1.233 | GPIO1_IO06 | CPU.GPIO1_IO06 | A3 | NVCC_3V3 | I/O | Pin ALT-0 | GPIO1_IO06 | |

| Pin ALT-1 | ENET_QOS_MDC | |||||||

| Pin ALT-3 | ISP_SHUTTER_TRIG_1 | |||||||

| Pin ALT-5 | USDHC1_CD_B | |||||||

| Pin ALT-6 | CCM_EXT_CLK3 | |||||||

| J1.235 | DGND | DGND | - | - | G | |||

| J1.237 | ETH0_TXRX3_M | LAN.TXTRM_D | 11 | - | D | |||

| J1.239 | ETH0_TXRX3_P | LAN.TXTRP_D | 10 | - | D | |||

| J1.241 | ETH0_TXRX2_M | LAN.TXTRM_C | 8 | - | D | |||

| J1.243 | ETH0_TXRX2_P | LAN.TXTRP_C | 7 | - | D | |||

| J1.245 | ETH0_TXRX1_M | LAN.TXTRM_B | 6 | - | D | |||

| J1.247 | ETH0_TXRX1_P | LAN.TXTRP_B | 5 | - | D | |||

| J1.249 | ETH0_TXRX0_M | LAN.TXTRM_A | 3 | - | D | |||

| J1.251 | ETH0_TXRX0_P | LAN.TXTRP_A | 2 | - | D | |||

| J1.253 | DGND | DGND | - | - | G | |||

| J1.255 | ETH0_LED1 | LAN.LED2 | 15 | VDD_1V8 | O | Must be level translated if used @ 3V3

Internally pulled-up to 1.8V during bootstrap |

||

| J1.257 | ETH0_LED2 | LAN.LED1/PME_N1 | 17 | VDD_1V8 | O | Must be level translated if used @ 3V3

Internally pulled-up to 1.8V during bootstrap |

||

| J1.259 | DGND | DGND | - | - | G | |||

Pinout Table EVEN pins declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Voltage domain | Type | Notes | Alternative Functions | |

|---|---|---|---|---|---|---|---|---|

| J1.2 | DGND | DGND | - | - | G | |||

| J1.4 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.6 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.8 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.10 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.12 | VIN_SOM | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.14 | DGND | DGND | - | - | G | |||

| J1.16 | SD1_CLK | CPU.SD1_CLK | W28 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_CLK | |

| Pin ALT-1 | ENET1_MDC | |||||||

| Pin ALT-3 | I2C5_SCL | |||||||

| Pin ALT-4 | UART1_TX | |||||||

| Pin ALT-5 | GPIO2_IO[0] | |||||||

| J1.18 | SD1_CMD | CPU.SD1_CMD | W29 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_CMD | |

| Pin ALT-1 | ENET1_MDIO | |||||||

| Pin ALT-3 | I2C5_SDA | |||||||

| Pin ALT-4 | UART1_RX | |||||||

| Pin ALT-5 | GPIO2_IO[1] | |||||||

| J1.20 | SD1_DATA0 | CPU.SD1_DATA0 | Y29 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA0 | |

| Pin ALT-1 | ENET1_RGMII_TD1 | |||||||

| Pin ALT-3 | I2C6_SCL | |||||||

| Pin ALT-4 | UART1_RTS_B | |||||||

| Pin ALT-5 | GPIO2_IO[2] | |||||||

| J1.22 | SD1_DATA1 | CPU.SD1_DATA1 | Y28 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA1 | |

| Pin ALT-1 | ENET1_RGMII_TD0 | |||||||

| Pin ALT-3 | I2C6_SDA | |||||||

| Pin ALT-4 | UART1_CTS_B | |||||||

| Pin ALT-5 | GPIO2_IO[3] | |||||||

| J1.24 | SD1_DATA2 | CPU.SD1_DATA2 | V29 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA2 | |

| Pin ALT-1 | ENET1_RGMII_RD0 | |||||||

| Pin ALT-3 | I2C4_SCL | |||||||

| Pin ALT-4 | UART2_TX | |||||||

| Pin ALT-5 | GPIO2_IO[4] | |||||||

| J1.26 | SD1_DATA3 | CPU.SD1_DATA3 | V28 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA3 | |

| Pin ALT-1 | ENET1_RGMII_RD1 | |||||||

| Pin ALT-3 | I2C4_SDA | |||||||

| Pin ALT-4 | UART2_RX | |||||||

| Pin ALT-5 | GPIO2_IO[5] | |||||||

| J1.28 | SD1_DATA4 | CPU.SD1_DATA4 | U26 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA4 | |

| Pin ALT-1 | ENET1_RGMII_TX_CTL | |||||||

| Pin ALT-3 | I2C1_SCL | |||||||

| Pin ALT-4 | UART2_RTS_B | |||||||

| Pin ALT-5 | GPIO2_IO[6] | |||||||

| J1.30 | SD1_DATA5 | CPU.SD1_DATA5 | AA29 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA5 | |

| Pin ALT-1 | ENET1_TX_ER | |||||||

| Pin ALT-3 | I2C1_SDA | |||||||

| Pin ALT-4 | UART2_CTS_B | |||||||

| Pin ALT-5 | GPIO2_IO[7] | |||||||

| J1.32 | SD1_DATA6 | CPU.SD1_DATA6 | AA28 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA6 | |

| Pin ALT-1 | FLEXSPI_B_DATA[2] | |||||||

| Pin ALT-2 | USDHC3_DATA2 | |||||||

| Pin ALT-3 | FLEXSPI_A_DATA[6] | |||||||

| Pin ALT-4 | ISP_PRELIGHT_TRIG_1 | |||||||

| Pin ALT-5 | GPIO3_IO[12] | |||||||

| J1.34 | SD1_DATA7 | CPU.SD1_DATA7 | U25 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_DATA7 | |

| Pin ALT-1 | ENET1_RX_ER | |||||||

| Pin ALT-3 | I2C2_SDA | |||||||

| Pin ALT-4 | UART3_RX | |||||||

| Pin ALT-5 | GPIO2_IO[9] | |||||||

| J1.36 | SD1_RESET_B | CPU.SD1_RESET_B | W25 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_RESET_B | |

| Pin ALT-1 | ENET1_TX_CLK | |||||||

| Pin ALT-3 | I2C3_SCL | |||||||

| Pin ALT-4 | UART3_RTS_B | |||||||

| Pin ALT-5 | GPIO2_IO[10] | |||||||

| J1.38 | SD1_STROBE | CPU.SD1_STROBE | W26 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC1_STROBE | |

| Pin ALT-3 | I2C3_SDA | |||||||

| Pin ALT-4 | UART3_CTS_B | |||||||

| Pin ALT-5 | GPIO2_IO[11] | |||||||

| J1.40 | DGND | DGND | - | - | G | |||

| J1.42 | SD2_CD_B | CPU.SD2_CD_B | AD29 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_CD_B | |

| Pin ALT-5 | GPIO2_IO[12] | |||||||

| J1.44 | SD2_CLK | CPU.SD2_CLK | AB29 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_CLK | |

| Pin ALT-2 | ECSPI2_SCLK | |||||||

| Pin ALT-3 | UART4_RX | |||||||

| Pin ALT-5 | GPIO2_IO[13] | |||||||

| J1.46 | SD2_CMD | CPU.SD2_CMD | AB28 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_CMD | |

| Pin ALT-2 | ECSPI2_MOSI | |||||||

| Pin ALT-3 | UART4_TX | |||||||

| Pin ALT-4 | AUDIOMIX_CLK | |||||||

| Pin ALT-5 | GPIO2_IO[14] | |||||||

| J1.48 | SD2_DATA0 | CPU.SD2_DATA0 | AC28 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_DATA0 | |

| Pin ALT-2 | I2C4_SDA | |||||||

| Pin ALT-3 | UART2_RX | |||||||

| Pin ALT-4 | AUDIOMIX_BIT_STREAM[0] | |||||||

| Pin ALT-5 | GPIO2_IO[15] | |||||||

| J1.50 | SD2_DATA1 | CPU.SD2_DATA1 | AC29 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_DATA1 | |

| Pin ALT-2 | I2C4_SCL | |||||||

| Pin ALT-3 | UART2_TX | |||||||

| Pin ALT-4 | AUDIOMIX_BIT_STREAM[1] | |||||||

| Pin ALT-5 | GPIO2_IO[16] | |||||||

| J1.52 | SD2_DATA2 | CPU.SD2_DATA2 | AA26 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_DATA2 | |

| Pin ALT-2 | ECSPI2_SS0 | |||||||

| Pin ALT-3 | AUDIOMIX_SPDIF_OUT | |||||||

| Pin ALT-4 | AUDIOMIX_BIT_STREAM[2] | |||||||

| Pin ALT-5 | GPIO2_IO[17] | |||||||

| J1.54 | SD2_DATA3 | CPU.SD2_DATA3 | AA25 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_DATA3 | |

| Pin ALT-2 | ECSPI2_MISO | |||||||

| Pin ALT-3 | AUDIOMIX_SPDIF_IN | |||||||

| Pin ALT-4 | AUDIOMIX_BIT_STREAM[3] | |||||||

| Pin ALT-5 | GPIO2_IO[18] | |||||||

| Pin ALT-6 | SRC_EARLY_RESET | |||||||

| J1.56 | SD2_RESET_B | CPU.SD2_RESET_B | AD28 | NVCC_3V3 | I/O | Pin ALT-0 | USDHC2_RESET_B | |

| Pin ALT-5 | GPIO2_IO[19] | |||||||

| Pin ALT-6 | SRC_SYSTEM_RESET | |||||||

| J1.58 | SD2_WP | CPU.SD2_WP | AC26 | NVCC_3V3 | I/O | Do not connect in case of internal NAND/NOR usage | Pin ALT-0 | USDHC2_WP |

| Pin ALT-5 | GPIO2_IO[20] | |||||||

| Pin ALT-6 | CORESIGHT_EVENTI | |||||||

| J1.60 | DGND | DGND | - | - | G | |||

| J1.62 | CLKIN1 | CPU.CLKIN1 | K28 | NVCC_3V3 | I | |||

| J1.64 | CLKIN2 | CPU.CLKIN2 | L28 | NVCC_3V3 | I | |||

| J1.66 | DGND | DGND | - | - | G | |||

| J1.68 | CLKOUT1 | CPU.CLKOUT1 | K29 | NVCC_3V3 | O | |||

| J1.70 | CLKOUT2 | CPU.CLKOUT2 | L29 | NVCC_3V3 | O | |||

| J1.72 | DGND | DGND | - | - | G | |||

| J1.74 | HDMI_CEC | CPU.HDMI_CEC | AD22 | NVCC_3V3 | I/O | Pin ALT-0 | HDMIMIX_EARC_CEC | |

| Pin ALT-3 | I2C6_SCL | |||||||

| Pin ALT-4 | CAN2_TX | |||||||

| Pin ALT-5 | GPIO3_IO[28] | |||||||

| J1.76 | HDMI_DDC_SCL | CPU.HDMI_DDC_SCL | AC22 | NVCC_3V3 | I/O | Pin ALT-0 | HDMIMIX_EARC_SCL | |

| Pin ALT-3 | I2C5_SCL | |||||||

| Pin ALT-4 | CAN1_TX | |||||||

| Pin ALT-5 | GPIO3_IO[26] | |||||||

| J1.78 | HDMI_DDC_SDA | CPU.HDMI_DDC_SDA | AF22 | NVCC_3V3 | I/O | Pin ALT-0 | HDMIMIX_EARC_SDA | |

| Pin ALT-3 | I2C5_SDA | |||||||

| Pin ALT-4 | CAN1_RX | |||||||

| Pin ALT-5 | GPIO3_IO[27] | |||||||

| J1.80 | HDMI_HPD | CPU.HDMI_HPD | AE22 | NVCC_3V3 | I/O | Pin ALT-0 | HDMIMIX_EARC_DC_HPD | |

| Pin ALT-1 | AUDIOMIX_EARC_HDMI_HPD_O | |||||||

| Pin ALT-3 | I2C6_SDA | |||||||

| Pin ALT-4 | CAN2_RX | |||||||

| Pin ALT-5 | GPIO3_IO[29] | |||||||

| J1.82 | DGND | DGND | - | - | G | |||

| J1.84 | HDMI_TXC_N | CPU.HDMI_TXC_N | AJ24 | - | D | |||

| J1.86 | HDMI_TXC_P | CPU.HDMI_TXC_P | AH24 | - | D | |||

| J1.88 | HDMI_TX0_N | CPU.HDMI_TX0_N | AJ25 | - | D | |||

| J1.90 | HDMI_TX0_P | CPU.HDMI_TX0_P | AH25 | - | D | |||

| J1.92 | HDMI_TX1_N | CPU.HDMI_TX1_N | AJ26 | - | D | |||

| J1.94 | HDMI_TX1_P | CPU.HDMI_TX1_P | AH26 | - | D | |||

| J1.96 | HDMI_TX2_N | CPU.HDMI_TX2_N | AJ27 | - | D | |||

| J1.98 | HDMI_TX2_P | CPU.HDMI_TX2_P | AH27 | - | D | |||

| J1.100 | DGND | DGND | - | - | G | |||

| J1.102 | EARC_P_UTIL | CPU.EARC_P_UTIL | AJ23 | VDDA_1V8 | D | |||

| J1.104 | EARC_N_HPD | CPU.EARC_N_HPD | AH22 | VDDA_1V8 | D | |||

| J1.106 | EARC_AUX | CPU.EARC_AUX | AH23 | VDDA_1V8 | I/O | |||

| J1.108 | DGND | DGND | - | - | G | |||

| J1.110 | ECSPI1_MISO | CPU.ECSPI1_MISO | AD20 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI1_MISO | |

| Pin ALT-1 | UART3_CTS_B | |||||||

| Pin ALT-2 | I2C2_SCL | |||||||

| Pin ALT-3 | AUDIOMIX_SAI7_RX_DATA[0] | |||||||

| Pin ALT-5 | GPIO5_IO[8] | |||||||

| J1.112 | ECSPI1_MOSI | CPU.ECSPI1_MOSI | AC20 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI1_MOSI | |

| Pin ALT-1 | UART3_TX | |||||||

| Pin ALT-2 | I2C1_SDA | |||||||

| Pin ALT-3 | AUDIOMIX_SAI7_RX_BCLK | |||||||

| Pin ALT-5 | GPIO5_IO[7] | |||||||

| J1.114 | ECSPI1_SCLK | CPU.ECSPI1_SCLK | AF20 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI1_SCLK | |

| Pin ALT-1 | UART3_RX | |||||||

| Pin ALT-2 | I2C1_SCL | |||||||

| Pin ALT-3 | AUDIOMIX_SAI7_RX_SYNC | |||||||

| Pin ALT-5 | GPIO5_IO[6] | |||||||

| J1.116 | ECSPI1_SS0 | CPU.ECSPI1_SS0 | AE20 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI1_SS0 | |

| Pin ALT-1 | UART3_RTS_B | |||||||

| Pin ALT-2 | I2C2_SDA | |||||||

| Pin ALT-3 | AUDIOMIX_SAI7_TX_SYNC | |||||||

| Pin ALT-5 | GPIO5_IO[9] | |||||||

| J1.118 | DGND | DGND | - | - | G | |||

| J1.120 | ECSPI2_MISO | CPU.ECSPI2_MISO | AH20 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI2_MISO | |

| Pin ALT-1 | UART4_CTS_B | |||||||

| Pin ALT-2 | I2C4_SCL | |||||||

| Pin ALT-3 | AUDIOMIX_SAI7_MCLK | |||||||

| Pin ALT-4 | CCM_CLKO1 | |||||||

| Pin ALT-5 | GPIO5_IO[12] | |||||||

| J1.122 | ECSPI2_MOSI | CPU.ECSPI2_MOSI | AJ21 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI2_MOSI | |

| Pin ALT-1 | UART4_TX | |||||||

| Pin ALT-2 | I2C3_SDA | |||||||

| Pin ALT-3 | AUDIOMIX_SAI7_TX_DATA[0] | |||||||

| Pin ALT-5 | GPIO5_IO[11] | |||||||

| J1.124 | ECSPI2_SCLK | CPU.ECSPI2_SCLK | AH21 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI2_SCLK | |

| Pin ALT-1 | UART4_RX | |||||||

| Pin ALT-2 | I2C3_SCL | |||||||

| Pin ALT-3 | AUDIOMIX_SAI7_TX_BCLK | |||||||

| Pin ALT-5 | GPIO5_IO[10] | |||||||

| J1.126 | ECSPI2_SS0 | CPU.ECSPI2_SS0 | AJ22 | NVCC_3V3 | I/O | Pin ALT-0 | ECSPI2_SS0 | |

| Pin ALT-1 | UART4_RTS_B | |||||||

| Pin ALT-2 | I2C4_SDA | |||||||

| Pin ALT-4 | CCM_CLKO2 | |||||||

| Pin ALT-5 | GPIO5_IO[13] | |||||||

| J1.128 | DGND | DGND | - | - | G | |||

| J1.130 | SPDIF_EXT_CLK | CPU.SPDIF_EXT_CLK | AC18 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SPDIF_EXT_CLK |

| Pin ALT-1 | PWM1_OUT | |||||||

| Pin ALT-3 | GPT1_COMPARE3 | |||||||

| Pin ALT-5 | GPIO5_IO[5] | |||||||

| J1.130 (*) | ISP_FL_TRIG_0 | CPU.NAND_ALE | N25 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_ALE |

| Pin ALT-1 | FLEXSPI_A_SCLK | |||||||

| Pin ALT-2 | AUDIOMIX_SAI3_TX_BCLK | |||||||

| Pin ALT-3 | ISP_FL_TRIG_0 | |||||||

| Pin ALT-4 | UART3_RX | |||||||

| Pin ALT-5 | GPIO3_IO[0] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE_CLK | |||||||

| J1.132 | SPDIF_RX | CPU.SPDIF_RX | AD18 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SPDIF_IN |

| Pin ALT-1 | PWM2_OUT | |||||||

| Pin ALT-2 | I2C5_SDA | |||||||

| Pin ALT-3 | GPT1_COMPARE2 | |||||||

| Pin ALT-4 | CAN1_RX | |||||||

| Pin ALT-5 | GPIO5_IO[4] | |||||||

| J1.132 (*) | ISP_SHUTTER_TRIG_0 | CPU.NAND_CE0_B | L26 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_CE0_B |

| Pin ALT-1 | FLEXSPI_A_SS0_B | |||||||

| Pin ALT-2 | AUDIOMIX_SAI3_TX_DATA[0] | |||||||

| Pin ALT-3 | ISP_SHUTTER_TRIG_0 | |||||||

| Pin ALT-4 | UART3_TX | |||||||

| Pin ALT-5 | GPIO3_IO[1] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE_CTL | |||||||

| J1.134 | SPDIF_TX | CPU.SPDIF_TX | AE18 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SPDIF_OUT |

| Pin ALT-1 | PWM3_OUT | |||||||

| Pin ALT-2 | I2C5_SCL | |||||||

| Pin ALT-3 | GPT1_COMPARE1 | |||||||

| Pin ALT-4 | CAN1_TX | |||||||

| Pin ALT-5 | GPIO5_IO[3] | |||||||

| J1.134 (*) | ISP_FLASH_TRIG_0 | CPU.NAND_DATA00 | R25 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DATA00 |

| Pin ALT-1 | FLEXSPI_A_DATA[0] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI3_RX_DATA[0] | |||||||

| Pin ALT-3 | ISP_FLASH_TRIG_0 | |||||||

| Pin ALT-4 | UART4_RX | |||||||

| Pin ALT-5 | GPIO3_IO[6] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[4] | |||||||

| J1.136 | DGND | DGND | - | - | G | |||

| J1.138 | SAI2_MCLK | CPU.SAI2_MCLK | AJ15 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI2_MCLK | |

| Pin ALT-1 | AUDIOMIX_SAI5_MCLK | |||||||

| Pin ALT-2 | ENET_QOS_1588_EVENT3_IN | |||||||

| Pin ALT-3 | CAN2_RX | |||||||

| Pin ALT-4 | ENET_QOS_1588_EVENT3_AUX_IN | |||||||

| Pin ALT-5 | GPIO4_IO[27] | |||||||

| Pin ALT-6 | AUDIOMIX_SAI3_MCLK | |||||||

| J1.140 | SAI2_RXC | CPU.SAI2_RXC | AJ16 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI2_RX_BCLK | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_BCLK | |||||||

| Pin ALT-3 | CAN1_TX | |||||||

| Pin ALT-4 | UART1_RX | |||||||

| Pin ALT-5 | GPIO4_IO[22] | |||||||

| Pin ALT-6 | AUDIOMIX_BIT_STREAM[1] | |||||||

| J1.142 | SAI2_RXD0 | CPU.SAI2_RXD0 | AJ14 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI2_RX_DATA[0] | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[0] | |||||||

| Pin ALT-2 | ENET_QOS_1588_EVENT2_OUT | |||||||

| Pin ALT-3 | AUDIOMIX_SAI2_TX_DATA[1] | |||||||

| Pin ALT-4 | UART1_RTS_B | |||||||

| Pin ALT-5 | GPIO4_IO[23] | |||||||

| Pin ALT-6 | AUDIOMIX_PDM_BIT_STREAM[3] | |||||||

| J1.144 | SAI2_RXFS | CPU.SAI2_RXFS | AH17 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI2_RX_SYNC | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_SYNC | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_TX_DATA[1] | |||||||

| Pin ALT-3 | AUDIOMIX_SAI2_RX_DATA[1] | |||||||

| Pin ALT-4 | UART1_TX | |||||||

| Pin ALT-5 | GPIO4_IO[21] | |||||||

| Pin ALT-6 | AUDIOMIX_BIT_STREAM[2] | |||||||

| J1.146 | SAI2_TXC | CPU.SAI2_TXC | AH15 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI2_TX_BCLK | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[2] | |||||||

| Pin ALT-3 | CAN1_RX | |||||||

| Pin ALT-5 | GPIO4_IO[25] | |||||||

| Pin ALT-6 | AUDIOMIX_BIT_STREAM[1] | |||||||

| J1.148 | SAI2_TXD0 | CPU.SAI2_TXD0 | AH16 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI2_TX_DATA[0] | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[3] | |||||||

| Pin ALT-2 | ENET_QOS_1588_EVENT2_IN | |||||||

| Pin ALT-3 | CAN2_TX | |||||||

| Pin ALT-4 | ENET_QOS_1588_EVENT2_AUX_IN | |||||||

| Pin ALT-5 | GPIO4_IO[26] | |||||||

| J1.150 | SAI2_TXFS | CPU.SAI2_TXFS | AJ17 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI2_TX_SYNC | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[1] | |||||||

| Pin ALT-2 | ENET_QOS_1588_EVENT3_OUT | |||||||

| Pin ALT-3 | AUDIOMIX_SAI2_TX_DATA[1] | |||||||

| Pin ALT-4 | UART1_CTS_B | |||||||

| Pin ALT-5 | GPIO4_IO[24] | |||||||

| Pin ALT-6 | AUDIOMIX_PDM_BIT_STREAM[2] | |||||||

| J1.152 | SAI3_MCLK | CPU.SAI3_MCLK | AJ20 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SAI3_MCLK |

| Pin ALT-1 | PWM4_OUT | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_MCLK | |||||||

| Pin ALT-4 | AUDIOMIX_SPDIF_OUT | |||||||

| Pin ALT-5 | GPIO5_IO[2] | |||||||

| Pin ALT-6 | AUDIOMIX_SPDIF_IN | |||||||

| J1.152 (*) | ISP_PRELIGHT_TRIG_0 | CPU.NAND_DATA01 | L25 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DATA01 |

| Pin ALT-1 | FLEXSPI_A_DATA[1] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI3_TX_SYNC | |||||||

| Pin ALT-3 | ISP_PRELIGHT_TRIG_0 | |||||||

| Pin ALT-4 | UART4_TX | |||||||

| Pin ALT-5 | GPIO3_IO[7] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[5] | |||||||

| J1.154 | SAI3_RXC | CPU.SAI3_RXC | AJ18 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP (*) |

Pin ALT-0 | AUDIOMIX_SAI3_RX_BCLK |

| Pin ALT-1 | AUDIOMIX_SAI2_RX_DATA[2] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_RX_BCLK | |||||||

| Pin ALT-3 | GPT1_CLK | |||||||

| Pin ALT-4 | UART2_CTS_B | |||||||

| Pin ALT-5 | GPIO4_IO[29] | |||||||

| Pin ALT-6 | AUDIOMIX_CLK | |||||||

| J1.154 (*) | ISP_SHUTTER_OPEN_0 | CPU.NAND_DQS | R26 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DQS |

| Pin ALT-1 | FLEXSPI_A_DQS | |||||||

| Pin ALT-2 | AUDIOMIX_SAI3_MCLK | |||||||

| Pin ALT-3 | ISP_SHUTTER_OPEN_0 | |||||||

| Pin ALT-4 | I2C3_SCL | |||||||

| Pin ALT-5 | GPIO3_IO[14] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[12] | |||||||

| J1.156 | SAI3_RXD | CPU.SAI3_RXD | AF18 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SAI3_RX_DATA[0] |

| Pin ALT-1 | AUDIOMIX_SAI2_RX_DATA[3] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_RX_DATA[0] | |||||||

| Pin ALT-4 | UART2_RTS_B | |||||||

| Pin ALT-5 | GPIO4_IO[30] | |||||||

| Pin ALT-6 | AUDIOMIX_BIT_STREAM[1] | |||||||

| J1.156 (*) | ISP_FL_TRIG_1 | CPU.NAND_DATA03 | N24 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DATA03 |

| Pin ALT-1 | FLEXSPI_A_DATA[3] | |||||||

| Pin ALT-2 | USDHC3_WP | |||||||

| Pin ALT-3 | UART4_RTS_B | |||||||

| Pin ALT-4 | ISP_FL_TRIG_1 | |||||||

| Pin ALT-5 | GPIO3_IO[9] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[7] | |||||||

| J1.158 | SAI3_RXFS | CPU.SAI3_RXFS | AJ19 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SAI3_RX_SYNC |

| Pin ALT-1 | AUDIOMIX_SAI2_RX_DATA[1] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_RX_SYNC | |||||||

| Pin ALT-3 | AUDIOMIX_SAI3_RX_DATA[1] | |||||||

| Pin ALT-4 | AUDIOMIX_SPDIF1_IN | |||||||

| Pin ALT-5 | GPIO4_IO[28] | |||||||

| Pin ALT-6 | AUDIOMIX_PDM_BIT_STREAM[0] | |||||||

| J1.158 (*) | ISP_SHUTTER_TRIG_1 | CPU.NAND_DATA04 | P29 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DATA04 |

| Pin ALT-1 | FLEXSPI_B_DATA[0] | |||||||

| Pin ALT-2 | USDHC3_DATA0 | |||||||

| Pin ALT-3 | FLEXSPI_A_DATA[4] | |||||||

| Pin ALT-4 | ISP_SHUTTER_TRIG_1 | |||||||

| Pin ALT-5 | GPIO3_IO[10] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[8] | |||||||

| J1.160 | SAI3_TXC | CPU.SAI3_TXC | AH19 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SAI3_TX_BCLK |

| Pin ALT-1 | AUDIOMIX_SAI2_TX_DATA[2] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_RX_DATA[2] | |||||||

| Pin ALT-3 | GPT1_CAPTURE1 | |||||||

| Pin ALT-4 | UART2_TX | |||||||

| Pin ALT-5 | GPIO5_IO[0] | |||||||

| Pin ALT-6 | AUDIOMIX_PDM_BIT_STREAM[2] | |||||||

| J1.160 (*) | ISP_FLASH_TRIG_1 | CPU.NAND_DATA05 | N29 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DATA05 |

| Pin ALT-1 | FLEXSPI_B_DATA[1] | |||||||

| Pin ALT-2 | USDHC3_DATA1 | |||||||

| Pin ALT-3 | FLEXSPI_A_DATA[5] | |||||||

| Pin ALT-4 | ISP_FLASH_TRIG_1 | |||||||

| Pin ALT-5 | GPIO3_IO[11] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[9] | |||||||

| J1.162 | SAI3_TXD | CPU.SAI3_TXD | AH18 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SAI3_TX_DATA[0] |

| Pin ALT-1 | AUDIOMIX_SAI2_TX_DATA[3] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_RX_DATA[3] | |||||||

| Pin ALT-3 | GPT1_CAPTURE2 | |||||||

| Pin ALT-4 | AUDIOMIX_SPDIF_EXT_CLK | |||||||

| Pin ALT-5 | GPIO5_IO[1] | |||||||

| Pin ALT-6 | SRC_BOOT_MODE[5] | |||||||

| J1.162 (*) | ISP_PRELIGHT_TRIG_1 | CPU.NAND_DATA06 | M29 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DATA06 |

| Pin ALT-1 | FLEXSPI_B_DATA[2] | |||||||

| Pin ALT-2 | USDHC3_DATA2 | |||||||

| Pin ALT-3 | FLEXSPI_A_DATA[6] | |||||||

| Pin ALT-4 | ISP_PRELIGHT_TRIG_1 | |||||||

| Pin ALT-5 | GPIO3_IO[12] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[10] | |||||||

| J1.164 | SAI3_TXFS | CPU.SAI3_TXFS | AC16 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | AUDIOMIX_SAI3_TX_SYNC |

| Pin ALT-1 | AUDIOMIX_SAI2_TX_DATA[1] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI5_RX_DATA[1] | |||||||

| Pin ALT-3 | AUDIOMIX_SAI3_TX_DATA[1] | |||||||

| Pin ALT-4 | UART2_RX | |||||||

| Pin ALT-5 | GPIO4_IO[31] | |||||||

| Pin ALT-6 | AUDIOMIX_PDM_BIT_STREAM[3] | |||||||

| J1.164 (*) | ISP_SHUTTER_OPEN_1 | CPU.NAND_DATA07 | R29 | NVCC_3V3 | I/O | Optional hardware mounting depending on order code

SPDIF or ISP / NAND (*) |

Pin ALT-0 | NAND_DATA07 |

| Pin ALT-1 | FLEXSPI_B_DATA[3] | |||||||

| Pin ALT-2 | USDHC3_DATA3 | |||||||

| Pin ALT-3 | FLEXSPI_A_DATA[7] | |||||||

| Pin ALT-4 | ISP_SHUTTER_OPEN_1 | |||||||

| Pin ALT-5 | GPIO3_IO[13] | |||||||

| Pin ALT-6 | CORESIGHT_TRACE[11] | |||||||

| J1.166 | SAI5_MCLK | CPU.SAI5_MCLK | AF14 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI5_MCLK | |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_BCLK | |||||||

| Pin ALT-2 | PWM1_OUT | |||||||

| Pin ALT-3 | I2C5_SDA | |||||||

| Pin ALT-5 | GPIO3_IO[25] | |||||||

| Pin ALT-6 | CAN2_RX | |||||||

| J1.168 | SAI5_RXC | CPU.SAI5_RXC | AD14 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI5_RX_BCLK | |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_DATA[1] | |||||||

| Pin ALT-2 | PWM3_OUT | |||||||

| Pin ALT-3 | I2C6_SDA | |||||||

| Pin ALT-4 | AUDIOMIX_CLK | |||||||

| Pin ALT-5 | GPIO3_IO[20] | |||||||

| J1.170 | SAI5_RXD0//

ISO_14443_LA |

CPU.SAI5_RXD0 | AE16 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SAI5 or SE050 ISO (**) |

Pin ALT-0 | AUDIOMIX_SAI5_RX_DATA[0] |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_DATA[2] | |||||||

| Pin ALT-2 | PWM2_OUT | |||||||

| Pin ALT-3 | I2C5_SCL | |||||||

| Pin ALT-4 | AUDIOMIX_BIT_STREAM[0] | |||||||

| Pin ALT-5 | GPIO3_IO[21] | |||||||

| J1.172 | SAI5_RXD1//

ISO_14443_LB |

CPU.SAI5_RXD1 | AD16 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SAI5 or SE050 ISO (**) |

Pin ALT-0 | AUDIOMIX_SAI5_RX_DATA[1] |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_DATA[3] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI1_TX_SYNC | |||||||

| Pin ALT-3 | AUDIOMIX_SAI5_TX_SYNC | |||||||

| Pin ALT-4 | AUDIOMIX_BIT_STREAM[1] | |||||||

| Pin ALT-5 | GPIO3_IO[22] | |||||||

| Pin ALT-6 | CAN1_TX | |||||||

| J1.174 | SAI5_RXD2//

ISO_7816_CLK |

CPU.SAI5_RXD2 | AF16 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SAI5 or SE050 ISO (**) |

Pin ALT-0 | AUDIOMIX_SAI5_RX_DATA[2] |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_DATA[4] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI1_TX_SYNC | |||||||

| Pin ALT-3 | AUDIOMIX_SAI5_TX_BCLK | |||||||

| Pin ALT-4 | AUDIOMIX_BIT_STREAM[2] | |||||||

| Pin ALT-5 | GPIO3_IO[23] | |||||||

| Pin ALT-6 | CAN1_RX | |||||||

| J1.176 | SAI5_RXD3//

ISO_7816_RST_N |

CPU.SAI5_RXD3 | AE14 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SAI5 or SE050 ISO (**) |

Pin ALT-0 | AUDIOMIX_SAI5_RX_DATA[3] |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_DATA[5] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI1_TX_SYNC | |||||||

| Pin ALT-3 | AUDIOMIX_SAI5_TX_DATA[0] | |||||||

| Pin ALT-4 | AUDIOMIX_PDM_BIT_STREAM[3] | |||||||

| Pin ALT-5 | GPIO3_IO[24] | |||||||

| Pin ALT-6 | CAN2_TX | |||||||

| J1.178 | SAI5_RXFS//

SE050_ENA |

CPU.SAI5_RXFS | AC14 | NVCC_3V3 | I/O | Hardware mounting option depending on order code

SAI5 or SE050 (**) |

Pin ALT-0 | AUDIOMIX_SAI5_RX_SYNC |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_DATA[0] | |||||||

| Pin ALT-2 | PWM4_OUT | |||||||

| Pin ALT-3 | I2C6_SCL | |||||||

| Pin ALT-5 | GPIO3_IO[19] | |||||||

| J1.180 | DGND | DGND | - | - | G | |||

| J1.182 | SAI1_MCLK | CPU.SAI1_MCLK | AE12 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_MCLK | |

| Pin ALT-1 | AUDIOMIX_SAI1_TX_BCLK | |||||||

| Pin ALT-4 | ENET1_TX_CLK | |||||||

| Pin ALT-5 | GPIO4_IO[20] | |||||||

| J1.184 | SAI1_RXC | CPU.SAI1_RXC | AH8 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_BCLK | |

| Pin ALT-1 | AUDIOMIX_PDM_CLK | |||||||

| Pin ALT-4 | ENET1_1588_EVENT0_OUT | |||||||

| Pin ALT-5 | GPIO4_IO[1] | |||||||

| J1.186 | SAI1_RXD0 | CPU.SAI1_RXD0 | AC10 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[0] | |

| Pin ALT-2 | AUDIOMIX_SAI1_TX_DATA[1] | |||||||

| Pin ALT-3 | AUDIOMIX_PDM_BIT_STREAM[0] | |||||||

| Pin ALT-4 | ENET1_1588_EVENT1_IN | |||||||

| Pin ALT-5 | GPIO4_IO[2] | |||||||

| J1.188 | SAI1_RXD1 | CPU.SAI1_RXD1 | AF10 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[1] | |

| Pin ALT-3 | AUDIOMIX_PDM_BIT_STREAM[1] | |||||||

| Pin ALT-4 | ENET1_1588_EVENT1_OUT | |||||||

| Pin ALT-5 | GPIO4_IO[3] | |||||||

| J1.190 | SAI1_RXD2 | CPU.SAI1_RXD2 | AH9 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[2] | |

| Pin ALT-1 | AUDIOMIX_SAI5_RX_DATA[2] | |||||||

| Pin ALT-3 | AUDIOMIX_BIT_STREAM[2] | |||||||

| Pin ALT-4 | ENET1_MDC | |||||||

| Pin ALT-5 | GPIO4_IO[4] | |||||||

| J1.192 | SAI1_RXD3 | CPU.SAI1_RXD3 | AJ8 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[3] | |

| Pin ALT-1 | AUDIOMIX_SAI5_RX_DATA[3] | |||||||

| Pin ALT-3 | AUDIOMIX_BIT_STREAM[3] | |||||||

| Pin ALT-4 | ENET1_MDIO | |||||||

| Pin ALT-5 | GPIO4_IO[5] | |||||||

| J1.194 | SAI1_RXD4 | CPU.SAI1_RXD4 | AD10 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[4] | |

| Pin ALT-1 | AUDIOMIX_SAI6_TX_BCLK | |||||||

| Pin ALT-2 | AUDIOMIX_SAI6_RX_BCLK | |||||||

| Pin ALT-4 | ENET1_RGMII_RD0 | |||||||

| Pin ALT-5 | GPIO4_IO[6] | |||||||

| J1.196 | SAI1_RXD5 | CPU.SAI1_RXD5 | AE10 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[5] | |

| Pin ALT-1 | AUDIOMIX_SAI6_TX_DATA[0] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI6_RX_DATA[0] | |||||||

| Pin ALT-3 | AUDIOMIX_SAI1_RX_SYNC | |||||||

| Pin ALT-4 | ENET1_RGMII_RD1 | |||||||

| Pin ALT-5 | GPIO4_IO[7] | |||||||

| J1.198 | SAI1_RXD6 | CPU.SAI1_RXD6 | AH10 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[6] | |

| Pin ALT-1 | AUDIOMIX_SAI6_TX_SYNC | |||||||

| Pin ALT-2 | AUDIOMIX_SAI6_RX_SYNC | |||||||

| Pin ALT-4 | ENET1_RGMII_RD2 | |||||||

| Pin ALT-5 | GPIO4_IO[8] | |||||||

| J1.200 | SAI1_RXD7 | CPU.SAI1_RXD7 | AH12 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_DATA[7] | |

| Pin ALT-1 | AUDIOMIX_SAI6_MCLK | |||||||

| Pin ALT-2 | AUDIOMIX_SAI1_TX_SYNC | |||||||

| Pin ALT-3 | AUDIOMIX_SAI1_TX_DATA[4] | |||||||

| Pin ALT-4 | ENET1_RGMII_RD3 | |||||||

| Pin ALT-5 | GPIO4_IO[9] | |||||||

| J1.202 | SAI1_RXFS | CPU.SAI1_RXFS | AJ9 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_RX_SYNC | |

| Pin ALT-4 | ENET1_1588_EVENT0_IN | |||||||

| Pin ALT-5 | GPIO4_IO[0] | |||||||

| J1.204 | SAI1_TXC | CPU.SAI1_TXC | AJ12 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_BCLK | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_BCLK | |||||||

| Pin ALT-4 | ENET1_RGMII_RXC | |||||||

| Pin ALT-5 | GPIO4_IO[11] | |||||||

| J1.206 | SAI1_TXD0 | CPU.SAI1_TXD0 | AJ11 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[0] | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[0] | |||||||

| Pin ALT-4 | ENET1_RGMII_TD0 | |||||||

| Pin ALT-5 | GPIO4_IO[12] | |||||||

| J1.208 | SAI1_TXD1 | CPU.SAI1_TXD1 | AJ10 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[1] | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[1] | |||||||

| Pin ALT-4 | ENET1_RGMII_TD1 | |||||||

| Pin ALT-5 | GPIO4_IO[13] | |||||||

| J1.210 | SAI1_TXD2 | CPU.SAI1_TXD2 | AH11 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[2] | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[2] | |||||||

| Pin ALT-4 | ENET1_RGMII_TD2 | |||||||

| Pin ALT-5 | GPIO4_IO[14] | |||||||

| J1.212 | SAI1_TXD3 | CPU.SAI1_TXD3 | AD12 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[3] | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_DATA[3] | |||||||

| Pin ALT-4 | ENET1_RGMII_TD3 | |||||||

| Pin ALT-5 | GPIO4_IO[15] | |||||||

| J1.214 | SAI1_TXD4 | CPU.SAI1_TXD4 | AH13 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[4] | |

| Pin ALT-1 | AUDIOMIX_SAI6_RX_BCLK | |||||||

| Pin ALT-2 | AUDIOMIX_SAI6_TX_BCLK | |||||||

| Pin ALT-4 | ENET1_RGMII_TX_CTL | |||||||

| Pin ALT-5 | GPIO4_IO[16] | |||||||

| J1.216 | SAI1_TXD5 | CPU.SAI1_TXD5 | AH14 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[5] | |

| Pin ALT-1 | AUDIOMIX_SAI6_RX_DATA[0] | |||||||

| Pin ALT-2 | AUDIOMIX_SAI6_TX_DATA[0] | |||||||

| Pin ALT-4 | ENET1_RGMII_TXC | |||||||

| Pin ALT-5 | GPIO4_IO[17] | |||||||

| J1.218 | SAI1_TXD6 | CPU.SAI1_TXD6 | AC12 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[6] | |

| Pin ALT-1 | AUDIOMIX_SAI6_RX_SYNC | |||||||

| Pin ALT-2 | AUDIOMIX_SAI6_TX_SYNC | |||||||

| Pin ALT-4 | ENET1_RX_ER | |||||||

| Pin ALT-5 | GPIO4_IO[18] | |||||||

| J1.220 | SAI1_TXD7 | CPU.SAI1_TXD7 | AJ13 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_DATA[7] | |

| Pin ALT-1 | AUDIOMIX_SAI6_MCLK | |||||||

| Pin ALT-3 | AUDIOMIX_CLK | |||||||

| Pin ALT-4 | ENET1_TX_ER | |||||||

| Pin ALT-5 | GPIO4_IO[19] | |||||||

| J1.222 | SAI1_TXFS | CPU.SAI1_TXFS | AF12 | NVCC_3V3 | I/O | Pin ALT-0 | AUDIOMIX_SAI1_TX_SYNC | |

| Pin ALT-1 | AUDIOMIX_SAI5_TX_SYNC | |||||||

| Pin ALT-4 | ENET1_RGMII_RX_CTL | |||||||

| Pin ALT-5 | GPIO4_IO[10] | |||||||

| J1.224 | DGND | DGND | - | - | G | |||

| J1.226

(SE on board) |

I2C1_SCL//

I2C_SCL_SE050 |

SE.ISO 7816 IO2 | 16 | SE_VOUT | I/O | see SE section for

more details |

||

| J1.226 | I2C1_SCL//

I2C_SCL_SE050 |

CPU.I2C1_SCL | AC8 | NVCC_3V3 | I/O | Pin ALT-0 | I2C1_SCL | |

| Pin ALT-1 | ENET_QOS_MDC | |||||||

| Pin ALT-3 | ECSPI1_SCLK | |||||||

| Pin ALT-5 | GPIO5_IO[14] | |||||||

| J1.228

(SE on board) |

I2C1_SDA//

I2C_SDA_SE050 |

SE.ISO 7816 IO1 | 3 | SE_VOUT | I/O | see SE section for

more details |

||

| J1.228 | I2C1_SDA//

I2C_SDA_SE050 |

CPU.I2C1_SDA | AH7 | NVCC_3V3 | I/O | Pin ALT-0 | I2C1_SDA | |

| Pin ALT-1 | ENET_QOS_MDIO | |||||||

| Pin ALT-3 | ECSPI1_MOSI | |||||||

| Pin ALT-5 | GPIO5_IO[15] | |||||||

| J1.230 | I2C2_SCL | CPU.I2C2_SCL | AH6 | NVCC_3V3 | I/O | Pin ALT-0 | I2C2_SCL | |

| Pin ALT-1 | ENET_QOS_1588_EVENT1_IN | |||||||

| Pin ALT-2 | USDHC3_CD_B | |||||||

| Pin ALT-3 | ECSPI1_MISO | |||||||

| Pin ALT-4 | ENET_QOS_1588_EVENT1_AUX_IN | |||||||

| Pin ALT-5 | GPIO5_IO[16] | |||||||

| J1.232 | I2C2_SDA | CPU.I2C2_SDA | AE8 | NVCC_3V3 | I/O | Pin ALT-0 | I2C2_SDA | |

| Pin ALT-1 | ENET_QOS_1588_EVENT1_OUT | |||||||

| Pin ALT-2 | USDHC3_WP | |||||||

| Pin ALT-3 | ECSPI1_SS0 | |||||||

| Pin ALT-5 | GPIO5_IO[17] | |||||||

| J1.234 | I2C3_SCL | CPU.I2C3_SCL | AJ7 | NVCC_3V3 | I/O | Pin ALT-0 | I2C3_SCL | |

| Pin ALT-1 | PWM4_OUT | |||||||

| Pin ALT-2 | GPT2_CLK | |||||||

| Pin ALT-3 | ECSPI2_SCLK | |||||||

| Pin ALT-5 | GPIO5_IO[18] | |||||||

| J1.236 | I2C3_SDA | CPU.I2C3_SDA | AJ6 | NVCC_3V3 | I/O | Pin ALT-0 | I2C3_SDA | |

| Pin ALT-1 | PWM3_OUT | |||||||

| Pin ALT-2 | GPT3_CLK | |||||||

| Pin ALT-3 | ECSPI2_MOSI | |||||||

| Pin ALT-5 | GPIO5_IO[19] | |||||||

| J1.238 | I2C4_SCL | CPU.I2C4_SCL | AF8 | NVCC_3V3 | I/O | Pin ALT-0 | I2C4_SCL | |

| Pin ALT-1 | PWM2_OUT | |||||||

| Pin ALT-2 | PCIE_CLKREQ_B | |||||||

| Pin ALT-3 | ECSPI2_MISO | |||||||

| Pin ALT-5 | GPIO5_IO[20] | |||||||

| J1.240 | I2C4_SDA | CPU.I2C4_SDA | AD8 | NVCC_3V3 | I/O | Pin ALT-0 | I2C4_SDA | |

| Pin ALT-1 | PWM1_OUT | |||||||

| Pin ALT-3 | ECSPI2_SS0 | |||||||

| Pin ALT-5 | GPIO5_IO[21] | |||||||

| J1.242 | DGND | DGND | - | - | G | |||

| J1.244 | UART1_RXD | CPU.UART1_RXD | AD6 | NVCC_3V3 | I/O | Pin ALT-0 | UART1_RX | |

| Pin ALT-1 | ECSPI3_SCLK | |||||||

| Pin ALT-5 | GPIO5_IO[22] | |||||||

| J1.246 | UART1_TXD | CPU.UART1_TXD | AJ13 | NVCC_3V3 | I/O | Pin ALT-0 | UART1_TX | |

| Pin ALT-1 | ECSPI3_MOSI | |||||||

| Pin ALT-5 | GPIO5_IO[23] | |||||||

| J1.248 | UART2_RXD | CPU.UART2_RXD | AF6 | NVCC_3V3 | I/O | Pin ALT-0 | UART2_RX | |

| Pin ALT-1 | ECSPI3_MISO | |||||||

| Pin ALT-3 | GPT1_COMPARE3 | |||||||

| Pin ALT-5 | GPIO5_IO[24] | |||||||

| J1.250 | UART2_TXD | CPU.UART2_TXD | AH4 | NVCC_3V3 | I/O | Pin ALT-0 | UART2_TX | |

| Pin ALT-1 | ECSPI3_SS0 | |||||||

| Pin ALT-3 | GPT1_COMPARE2 | |||||||

| Pin ALT-5 | GPIO5_IO[25] | |||||||

| J1.252 | UART3_RXD | CPU.UART3_RXD | AE6 | NVCC_3V3 | I/O | Pin ALT-0 | UART3_RX | |

| Pin ALT-1 | UART1_CTS_B | |||||||

| Pin ALT-2 | USDHC3_RESET_B | |||||||

| Pin ALT-3 | GPT1_CAPTURE2 | |||||||

| Pin ALT-4 | CAN2_TX | |||||||

| Pin ALT-5 | GPIO5_IO[26] | |||||||

| J1.254 | UART3_TXD | CPU.UART3_TXD | AJ4 | NVCC_3V3 | I/O | Pin ALT-0 | UART3_TX | |

| Pin ALT-1 | UART1_RTS_B | |||||||

| Pin ALT-2 | USDHC3_VSELECT | |||||||

| Pin ALT-3 | GPT1_CLK | |||||||

| Pin ALT-4 | CAN2_RX | |||||||

| Pin ALT-5 | GPIO5_IO[27] | |||||||

| J1.256 | UART4_RXD | CPU.UART4_RXD | AJ15 | NVCC_3V3 | I/O | Pin ALT-0 | UART4_RX | |

| Pin ALT-1 | UART2_CTS_B | |||||||

| Pin ALT-2 | PCIE_CLKREQ_B | |||||||

| Pin ALT-3 | GPT1_COMPARE1 | |||||||

| Pin ALT-4 | I2C6_SCL | |||||||

| Pin ALT-5 | GPIO5_IO[28] | |||||||

| J1.258 | UART4_TXD | CPU.UART4_TXD | AH5 | NVCC_3V3 | I/O | Pin ALT-0 | UART4_TX | |

| Pin ALT-1 | UART2_RTS_B | |||||||

| Pin ALT-3 | GPT1_CAPTURE1 | |||||||

| Pin ALT-4 | I2C6_SDA | |||||||

| Pin ALT-5 | GPIO5_IO[29] | |||||||

| J1.260 | DGND | DGND | - | - | G | |||

(*) SPIDF and ISP signals cannot be present at the same time. ISP signals are in alternative to NAND and eMMC usage (see i.MX8Plus NAND controller on Reference Manual for more details). Please contact sales for more information

(**) SAI5 and SE050 ISO interface cannot be present at the same time. Please contact sales for more information

Power and reset[edit | edit source]

Power Supply Unit (PSU) and recommended power-up sequence[edit | edit source]

Implementing correct power-up sequence for iMX8MPlus processors is not a trivial task because several power rails are involved.

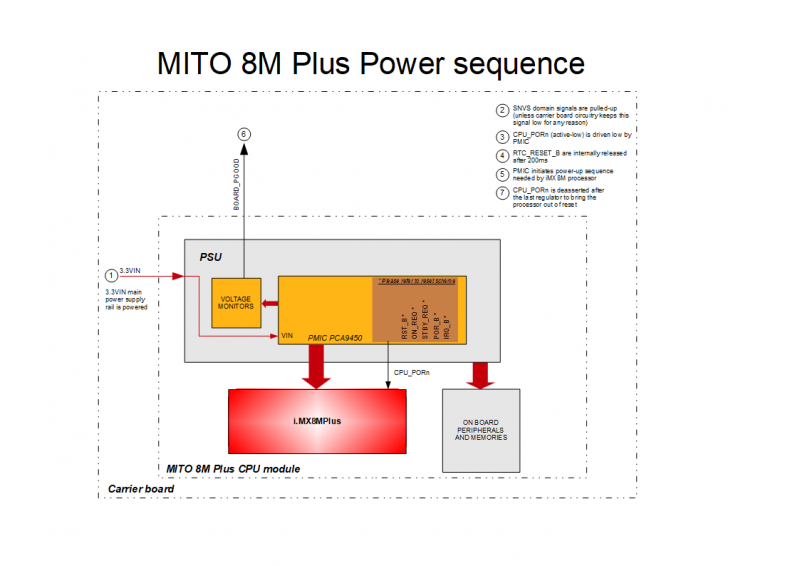

ORCA SOM simplifies this task by embedding all the needed circuitry. The following picture shows a simplified block diagram of PSU/voltage monitoring circuitry:

The PSU is composed of two main blocks:

- power management integrated circuit

- additional generic power management circuitry that completes PMIC functionalities

The PSU:

- generates the proper power-up sequence required by the SOC processor and surrounding memories and peripherals

- synchronizes the powering up of carrier board in order to prevent back power

Power-up sequence[edit | edit source]

The typical power-up sequence is the following:

- 3.3VIN main power supply rail is powered

- SNVS domain signals are pulled-up (unless carrier board circuitry keeps this signal low for any reason)

- CPU_PORn (active-low) is driven low by PMIC

- RTC_RESET_B are internally released after 200ms

- PMIC initiates power-up sequence needed by iMX8M processor

- BOARD_PGOOD goes up when NVCC_3V3 (CPU I/O power rail) is ready

- CPU_PORn is deasserted after the last regulator to bring the processor out of reset

Note on BOARD_PGOOD usage[edit | edit source]

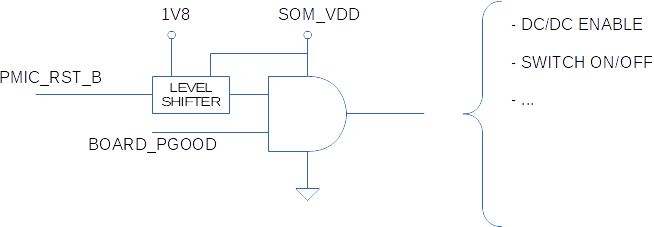

BOARD_PGOOD is generally used on carrier board to drive loads such as DC/DC enable inputs or switch on/off control signals.

Depending on the kind of such loads, BOARD_PGOOD might not be able to drive them properly because it has a 20mA output current absolute maximum rating.

In these cases a simple 2-input AND port with a level shifter for the PMIC_RST_B input can be used to address this issue. The following picture depicts a principle schematic showing this solution.

SOM_VDD denotes the power rail used to power ORCA SoM (i.e. 3V3VIN).

Additionally, we suggest using ICs with Schmitt trigger input ports.

Reset scheme and control signals[edit | edit source]

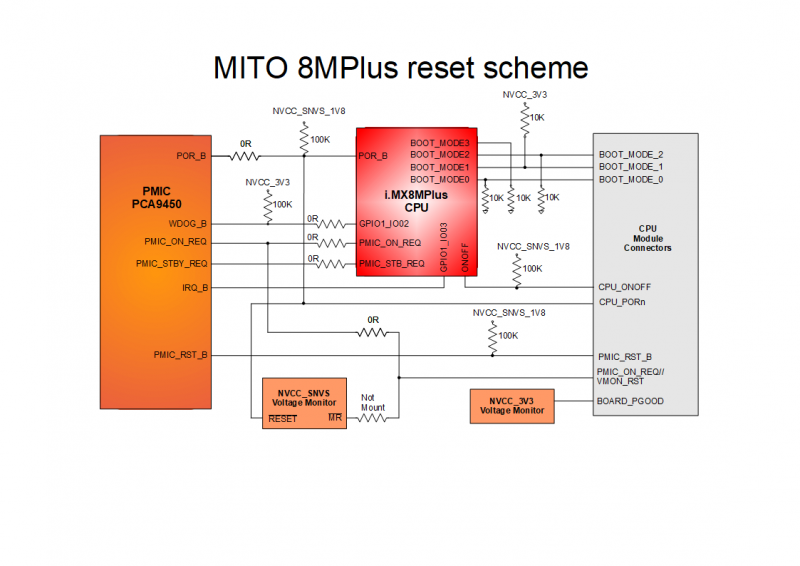

The following picture shows the simplified block diagram of reset scheme and voltage monitoring.

NVCC_VSNVS_1V8[edit | edit source]

Some signals that are related to reset circuitry are pulled-up to NVCC_VSNVS_1V8 (1.8V internal rail).

Hence it is recommended that system designer takes into account these factors in order to properly manage these signals at carrier board level.

PMIC_RST_B[edit | edit source]

EXT_RESET is internally pulled-up with a 100kΩ to NVCC_VSNVS_1V8. Connect EXT_RESET signal to GND (for example with a button or an open-collector circuit) causes the PMIC to assert its POR_B output.

When this signal is pulled low all the power supplies except for the SNVS domain will be OFF.

The RESETn will keep asserted for 250 ms after PMIC_RST_B is released, thus providing enough time for the power supplies to be completely powered down. During this time, the CPU_PORb driven by the PMIC will also keep asserted (low).

After RESETn is released, the power supplies will start to ramp up in defined sequence. When all the power supplies have reached their operating voltages, POR_B will be de-asserted, and the CPU may begin booting from reset.

PMIC_ON_REQ//VMON_RST[edit | edit source]

Two different routing options are available for this pin.

By default, this pin is connected to PMIC's PMIC_ON_REQ signal. The PMIC_ON_REQ signal is driven by iMX8MPlus SoC to place the system in power-down mode.

Optionally, PMIC_ON_REQ//VMON_RST can be routed to the master reset input of a voltage supervisor instead. For more details about this option, please write to the Sales Department.

CPU_PORn[edit | edit source]

PMIC can assert this active-low signal. Other internal IC, such as ethernet PHY or boot memory devices, could be connected to this signal. This guarantees that they are in a known state when reset signal is released.

CPU_ONOFF[edit | edit source]

CPU_ONOFF is internally pulled-up with a 100kΩ to NVCC_VSNVS_1V8. This input signal is connected directly to the ONOFF input of the CPU.

BOARD_PGOOD[edit | edit source]

BOARD_PGOOD is the output of the voltage monitor on the internal NVCC_3V3 rail (I/O pins supply) and must be used as power enable for all the electronics on MITO 8M carrier board.

When the I/O pins power rail on MITO 8M is not ready (BOARD_PGOOD low) all the integrated circuits connected to the CPU must be powered off in order to avoid back-powering or other issue related to a wrong power-up sequence.

BOOT_MODE_[0-2][edit | edit source]

BOOT_MODE_x pins can be internally pulled-up with 10kΩ to NVCC_3V3 or pulled-down with 10kΩ to DGND to provide the default boot mode. The previous block diagram shows the SD3 eMMC boot option.

To overwrite the boot configuration these pins can be pulled low or high with 1kΩ resistor, the pull-up rail has to be a 3.3V enabled by BOARD_PGOOD signal.

WDOG_B[edit | edit source]

WDOG_B is a PMIC input signal that is configured by default to generate a system reset. It is internally connected to processor's watchdog output.

Handling CPU-initiated software reset[edit | edit source]

By default, ORCA SOM implements a conservative approach regarding CPU-initiated software reset. In essence, whenever a software reset is issued, a full power-up cycle is triggered. This technique is implemented in DESK-MX8M-L. At the software level, U-Boot and Linux kernel software reset routines make use of a SOC's WDT to assert the WDOG1_WDOG_B reset signal. This signal in turn is routed to GPIO1_IO02 pad (MUX mode = 1, internal connection only). At the hardware level, this signal is connected to the PMIC WDOG_B input to achieve the desired outcome.

System boot[edit | edit source]

The boot process begins at Power On Reset (POR) where the hardware reset logic forces the ARM core to begin execution starting from the on-chip boot ROM. The boot ROM:

- determines whether the boot is secure or non-secure

- performs some initialization of the system and clean-ups

- reads the mode pins to determine the primary boot device

- once it is satisfied, it executes the boot code

Boot options[edit | edit source]

Many options are available related for ORCA SOM System boot. They are selected by the BOOT_MODE[0..2] signals as reported in the following table:

| BOOT_MODE_2 | BOOT_MODE_1 | BOOT_MODE_0 | BOOT peripheral |

|---|---|---|---|

| 0 | 0 | 0 | Boot From Internal Fuses |

| 0 | 0 | 1 | USB Serial Download |

| 0 | 1 | 0 | USDHC3 (eMMC boot only, SD3 8-bit) |

| 0 | 1 | 1 | USDHC2 (SD boot only, SD2) |

| 1 | 0 | 0 | NAND 8-bit single device 256 page |

| 1 | 0 | 1 | NAND 8-bit single device 512 page |

| 1 | 1 | 0 | QSPI 3B Read |

When the signals are left floating the primary boot device is set by default to eMMC on SD3.

The BOOT_MODE[0..2] signals are latched when processor reset is released.

The boot process is managed by on-chip boot ROM code: please refer to the processor's Reference Manual for more information.

On board JTAG connector[edit | edit source]

JTAG signals are routed to the J1 primary connector of the ORCA PCB. See the pinout section for more details.

Peripherals[edit | edit source]

Peripheral Audio[edit | edit source]

The Audio interface available on ORCA SoM is based on iMX8MPlus SoC which provides the following audio subsystems:

- Synchronous Audio Interface (SAI)

- 6x I2S/SAI

- Sony/Philips Digital Interface (SPDIF)

- PDM microphone interface

- eARC

Description[edit | edit source]

The I2S module provides a synchronous audio interface (SAI) that supports full-duplex serial interfaces with frame synchronization such as I2S, AC97, TDM, and codec/DSP interfaces. It supports the following standards and features:

- Transmitter and receiver with independent bit clock and frame sync supporting 8 data lines

- Receiver with independent bit clock and frame sync supporting 8 data lines

- Each data line can support a maximum Frame size of 32 words

- Asynchronous 128 x 32-bit FIFO for each transmit and receive data line

- Supports packing of 8-bit and 16-bit data into each 32-bit FIFO word

- Supports combining multiple data line FIFOs into single data line FIFO

- Independent 32-bit timestamp counters and bit counters for monitoring transmit and receive progress

The Sony/Philips Digital Interface (SPDIF) audio block is a stereo transceiver that allows the processor to receive and transmit digital audio.

The PDM Microphone Interface (MICFIL) includes the following features:

- Decimation filters:

- Fixed filtering characteristics for audio application.

- 24-bit signed filter output.

- Maximum dynamic range: 120dB.

- Internal clock divider for a programmable PDM clock generation.

- Full or partial set of channels operation with individual enable control.

- Programmable decimation rate.

- Programmable DC remover.

- Range adjustement capability.

- FIFOs with interrupt and DMA capability.

- Each FIFO with 32 entries length.

- Hardware Voice Activity Detector (HWVAD).

- Interrupt capability.

- Zero-Crossing Detection (ZCD) option.

The enhanced audio return channel (eARC) provides an advanced audio stream through the HDMI interface.

The asyncronous sample rate converter (ASRC) is a digital module that converts audio from a source sample rate to a destination sample rate.

The primary features for the ASRC are as follows:

- 4 Contexts - groups of channels with an independent time base

- Fully independent and concurrent context control

- Simultaneous processing of up to 32 audio channels

- Programmable filter charachteristics for each context

- 32, 24, 20, and 16-bit fixed point audio sample support

- 32-bit floating point audio sample support

- 8kHz to 384 kHz sample rate

- 1/16 to 8x sample rate conversion ratio

- Software control of fine conversion ratio

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral CAN[edit | edit source]

The CAN interface available on ORCA SoM is based on iMX8MPlus SoC which provides the following interfaces:

- 2x FlexCAN

Description[edit | edit source]

The FlexCAN module is a communication controller implementing the CAN protocol according to the ISO 11898-1 standard and CAN 2.0 B protocol specifications.

The FlexCAN module includes these distinctive features:

- Full implementation of the CAN with Flexible Data Rate (CAN FD) protocol specification and CAN protocol specification, Version 2.0 B

- Compliant with the ISO 11898-1 standard

- Full-featured Rx FIFO with storage capacity for up to six frames and automatic internal pointer handling with DMA support

- Time stamp based on 16-bit free running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Supports detection and correction of errors in memory read accesses

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral HDMI[edit | edit source]

HDMI (High-Definition Multimedia Interface) is a compact audio/video interface for transmitting uncompressed digital video data and uncompressed/compressed digital audio data.

HDMI connects digital audio/video sources-such as set-top boxes, Blu-ray Disc players, personal computers (PCs), video game consoles, and AV receivers to compatible digital audio devices, computer monitors, and digital televisions.

Description[edit | edit source]

The HDMI interface available on ORCA is based on iMX8MPlus SoC.

The HDMI port supports the following standards and features:

- High-Definition Multimedia Interface Specification, Version up to 2.0a

- Compliant with HDCP2.2 (and back compatible with HDCP1.3/HDCP1.4)

- Variety of video resolutions and formats

- Supports up to 4k2k at 60Hz resolution

- Supports 8, 10, 12, and 16bpp

- Supports RGB, YCbCr422 formats

- Variety of audio formats – PCM and compressed, over I2S interface

- I2S PCM samples are converted to comply with IEC60958 sub-frames

- Supporting I2S-TDM

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral LVDS[edit | edit source]

The LVDS interface available on ORCA is based on iMX8MPlus SoC.

This support covers all aspects of these activities:

- Connectivity to relevant devices - Displays with LVDS receivers

- Arranging the data as required by the external display receiver and by LVDS display standards

- Synchronization and control capabilities

Description[edit | edit source]

The LVDS ports can be used as follows:

- Single channel (4 lanes) output at up to 80MHz pixel clock and LVDS clock. This supports resolutions up to 1366x768p60.

- Dual asynchronous channels (8 data, 2 clocks). This is intended for a single panel with two interfaces, transferring across two channels (even pixel/odd pixel). This is supported at up to 160MHz pixel clock, which is up to 80MHz LVDS clock (due to 2 pixels per LVDS clock). This supports resolutions above 1366x768p60, up to 1080p60.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral MIPI[edit | edit source]

The MIPI interfaces available on iMX8MPlus SoC are following described:

- The Camera Serial Interface (CSI) is a specification of the Mobile Industry Processor Interface (MIPI) Alliance. It defines an interface between a camera and a host processor.

- The Display Serial Interface (DSI) is a specification by the Mobile Industry Processor Interface (MIPI) Alliance aimed at reducing the cost of display controllers in a mobile device. It is commonly targeted at LCD and similar display technologies.

The two CSI and the DSI interfaces on ORCA SOM are available on SODIMM connector.

Description[edit | edit source]

The MIPI CSI ports support the following standards and features:

- MIPI D-PHY specification V1.2

- Compliant to MIPI CSI2 Specification V1.3 except for C-PHY feature

- Support primary and secondary Image format

- YUV420, YUV420 (Legacy), YUV420 (CSPS), YUV422 of 8-bits and 10-bits

- RGB565, RGB666, RGB888

- RAW6, RAW7, RAW8, RAW10, RAW12, RAW14

- All of User defined Byte-based Data packet

- Support up to 4 lanes of D-PHY

- Interfaces:

- Compatible to PPI(Protocol-to-PHY Interface) in MIPI D-PHY Specification

- AMBA3.0 APB Slave for Register configuration.

- Image output data buswidth : 32 bits

- Image memory:

- Size of SRAM is 4KB

- Pixel clock can be gated when no ppi data is coming.

The MIPI DSI port supports the following standards and features:

- Complies to MIPI DSI Standard Specification V1.01r11

- Maximum resolution ranges up to WQHD (1920x1080p60, 24bpp)

- It should be decided on bandwidth between input clock (video clock) and output clock (D-PHY HS clock).

- Supports 1, 2, 3, or 4 data lanes

- Supports pixel format: 16bpp, 18bpp packed, 18bpp loosely packed (3 byte format), and 24bpp

- Maximum resolution ranges up to WQHD (1920x1080p60, 24bpp)

- Interfaces:

- Complies with Protocol-to-PHY Interface (PPI) in 1.0Gbps / 1.5Gbps MIPI D-PHY

- Supports RGB Interface for Video Image Input from general display controller

- Supports S-i80(Synchronous i80) Interface for Command Mode Image input from display controller

- Supports PMS control interface for PLL to configure byte clock frequency

- Supports Prescaler to generate escape clock from byte clock

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral ISP[edit | edit source]

The Image Signal Processor (ISP) available on ORCA is based on iMX8MPlus SoC wich provides the following interfaces:

- I/O signals to control mechanical shutter, flash and other advanced camera features

Description[edit | edit source]

The Image Signal Processing (ISP) core is a complete video and still picture input block. It contains image processing and color space conversion (RAW Bayer to YUV) functions.

The ISP is connected to a MIPI-CSI interface and receives 1 pixel/clock from the CSI Rx Controller.

The following features are supported by the main ISP submodule:

- ITU-R BT.601 compatible 12-bit video interface

- Variable sensor interface for RGB-Bayer Sensors

- Lens shade correction

- Filter (Noise reduction, Sharpness, Blurring)

- Programmable gamma correction for sensor adaptation and display correction

- Exposure measurement for AE (AEC/AGC) Auto focus measurement (AF)

- Mechanical shutter control

- Flash light control

- Video Stabilization

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral SDIOs[edit | edit source]

The Ultra Secured Digital Host Controller (uSDHC) provides the interface between the host system and the SD/SDIO/MMC cards or devices.

ORCA SOM provides up to two SDIO interface available for an external memory device connection. The third interface is used for the on board eMMC flash.

Description[edit | edit source]

The SDIOs interface available on ORCA is based on iMX8MPlus SoC.

The SDIOs port supports the following standards and features:

- Conforms to the SD Host Controller Standard Specification version 2.0/3.0

- Compatible with the MMC System Specification version 4.2/4.3/4.4/4.41/5.0/5.1

- Compatible with the SD Memory Card Specification version 3.0 and supports the Extended Capacity SD Memory Card

- Compatible with the SDIO Card Specification version 2.0/3.0

- Supports 1-bit/4-bit SD and SDIO modes, and 1-bit/4-bit/8-bit MMC modes

- Card bus clock frequency up to 208 MHz

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral SPI[edit | edit source]

The Enhanced Configurable Serial Peripheral Interface (ECSPI) is a full-duplex, synchronous, four-wire serial communication block.

Description[edit | edit source]

Three SPI interface are available on ORCA based on iMX8MPlus SoC.

The SPI port supports the following standards and features:

- Full-duplex synchronous serial interface

- Master/Slave configurable

- One Chip Select (SS) signal

- Transfer continuation function allows unlimited length data transfers

- 32-bit wide by 64-entry FIFO for both transmit and receive data

- Polarity and phase of the Chip Select (SS) and SPI Clock (SCLK) are configurable

- Direct Memory Access (DMA) support

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral I2C[edit | edit source]

I2C is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices.

This bus is suitable for applications requiring occasional communications over a short distance between many devices.

Description[edit | edit source]

The three I2C interface available on ORCA is based on iMX8MPlus SoC and it is designed to be compatible with the PhilipsTM I2C bus protocol.

The iMX8MPlus SOC has six I2C bus interfaces, but there is some limitation about:

- The I2C1 bus is internally used for PMIC and it is not available if the secure element unit is on board

See Pin mapping tables for connection details.

Features[edit | edit source]

The I2C port supports the following standards and features:

- Compatibility with I2C bus standard

- Multimaster operation

- Software programmability for one of 64 different serial clock frequencies

- Software-selectable acknowledge bit

- Interrupt-driven, byte-by-byte data transfer

- Arbitration-lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated Start signal generation

- Acknowledge bit generation/detection

- Bus-busy detection

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral UART[edit | edit source]

Description[edit | edit source]

The Universal Asynchronous Receiver/Transmitter (UART) interface available on ORCA is based on iMX8MPlus SoC.

UART provides serial communication capability with external devices and support NRZ encoding format, RS485 compatible 9 bit data format and IrDA-compatible infrared slow data rate (SIR) format.

The UART port supports the following standards and features:

- High-speed TIA/EIA-232-F compatible, up to Mbit/s

- Serial IR interface low-speed, IrDA-compatible (up to 115.2 Kbit/s)

- 9-bit or Multidrop mode (RS-485) support (automatic slave address detection)

- 7 or 8 data bits for RS-232 characters, or 9 bit RS-485 format

- 1 or 2 stop bits

- Programmable parity (even, odd, and no parity)

- Hardware flow control support for request to send (RTS_B) and clear to send (CTS_B) signals

- Two independent, 32-entry FIFOs for transmit and receive

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral USB[edit | edit source]

Universal Serial Bus (USB) is an industry standard that establishes specifications for cables and connectors and protocols for connection, communication and power supply (interfacing) between computers, peripherals and other computers.

Description[edit | edit source]

The two USB interface available on ORCA are based on iMX8MPlus SoC.

Each USB 3.0-compliant serial interface port supports the following standards and features:

- Complies with USB specification rev 3.0

- USB dual-role operation and can be configured as host or device

- Super-speed (5 Gbit/s), high-speed (480 Mbit/s), full-speed (12 Mbit/s), and low-speed (1.5 Mbit/s) operations

VBUS detection[edit | edit source]

On the ORCA external connector the USBx_VBUS pins are present to detect that the USB is enabled end therefore power the internal USB PHY.

These pins has a thresold of 4.6V and can accept up to 25V so a direct connection to the USB port VBUS is allowed, even when Power Deliver handshake sets the USB3.0 VBUS to the highest value of 20V.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral PCI Express[edit | edit source]

PCI Express (Peripheral Component Interconnect Express) is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards.

Description[edit | edit source]

The PCI Express interface available on ORCA is based on iMX8MPlus SoC.

The PCI Express interface supports the following standards and features:

- two PCIe PHY ports (1-lane each)

- up to 8.0 Gbps data rate

- complies to PCI Express Gen3 specification

- 8B/10B Encoding / Decoding