ETRA SOM/ETRA Hardware/pdf

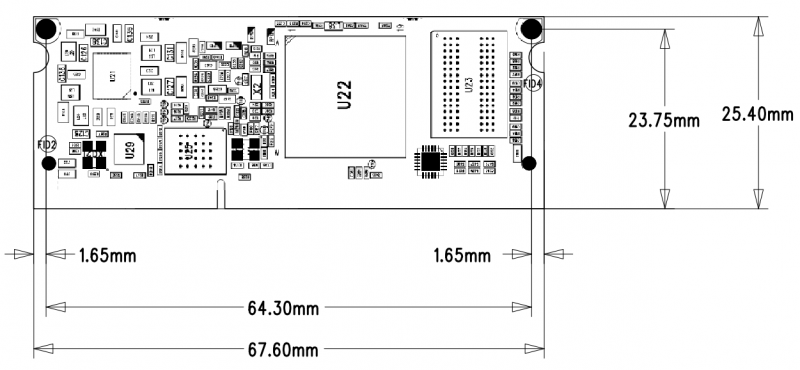

General Information[edit | edit source]

ETRA Block Diagram[edit | edit source]

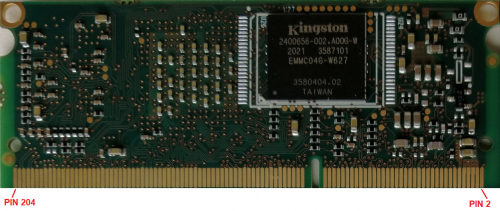

ETRA TOP View[edit | edit source]

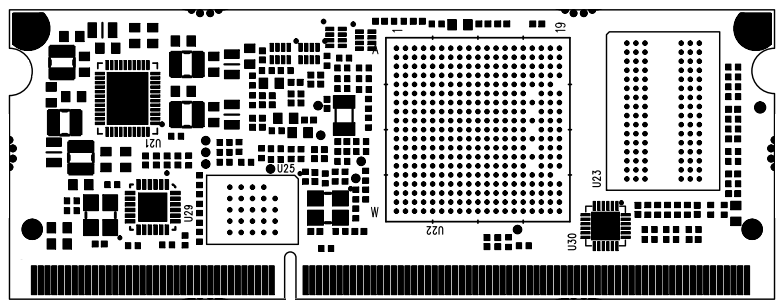

ETRA BOTTOM View[edit | edit source]

Processor and memory subsystem[edit | edit source]

The heart of ETRA module is composed by the following components:

- STM32MP1 SoC application processor

- Power supply unit

- DDR3L memory banks

- NOR and NAND flash banks

- SODIMM-DDR3 form-factor and connector with interfaces signals

This chapter shortly describes the main ETRA components.

Processor Info[edit | edit source]

| Processor | # Cores | Clock | L2 Cache | DDR3 | MCU | Graphics Acceleration | Temp grade |

| STM32MP151 | 1 | 650MHz 800 MHz |

256 KB | 16/32 bit @ 533 MHz | 32 bit Arm Cortex M4 @209MHZ | -40 +125°C | |

| STM32MP153 | 2 | 650MHz 800 MHz |

256 KB | 16/32 bit @ 533 MHz | 32 bit Arm Cortex M4 @209MHZ | -40 +125°C | |

| STM32MP157 | 2 | 650MHz 800 MHz |

256 KB | 16/32 bit @ 533 MHz | 32 bit Arm Cortex M4 @209MHZ | 3D: Vivante GC Nano | -40 +125°C -20 +105°C |

RAM memory bank[edit | edit source]

Single DDR3L SDRAM memory bank. The following table reports the SDRAM specifications:

| CPU connection | Multi-mode DDR controller (MMDC) |

| Size min | 128 MB |

| Size max | 1 GB |

| Width | 16 bit |

| Speed | 533 MHz |

NOR flash bank[edit | edit source]

NOR flash is a Serial Peripheral Interface (SPI) device. This device is connected to the QUADSPI channel. and can act as boot memory. The following table reports the NOR flash specifications:

| CPU connection | QUADSPI |

| Size min | 16 MB |

| Size max | 32 MB |

| Chip select | PB6 |

| Bootable | Yes |

NOTE: the QUADSPI pins are shared with other interfaces. Make shure to not populate the other devices to use this peripheral.

NAND flash bank[edit | edit source]

On board alternate storage memory is a 8-bit wide NAND flash connected to the CPU's Raw NAND flash controller. Optionally, it can act as boot peripheral. The following table reports the NAND flash specifications:

| CPU connection | Raw NAND flash controller |

| Page size | 512 byte, 2 kbyte or 4 kbyte |

| Size min | 128 MB |

| Size max | 2 GB |

| Width | 8 bit |

| Chip select | PG9 |

| Bootable | Yes |

NOTE: the NAND pins are shared with other interfaces. Make shure to not populate the other devices to use this peripheral.

eMMC flash bank[edit | edit source]

On board main storage memory is a 8-bit wide eMMC device connected to SDMMC2 controller and by default it acts as boot peripheral. The following table reports the eMMC flash specifications:

| CPU connection | SDMMC2 |

| Size min | 4 GB |

| Size max | 8 GB |

| Width | 4/8 bit |

| SDHC | No |

| Bootable | Yes |

NOTE: the SDMMC2 pins are shared with other interfaces. Make shure to not populate the other devices to use this peripheral. The use of LCD interface limit the bus width to 4 bit

The eMMC and NAND flashes are overlapped, and can be alternatively populated.

Memory map[edit | edit source]

For detailed information, please refer to chapter 2.5 “Memory organization” of the STM32MP1 Reference Manual (RM0436).

Power supply unit[edit | edit source]

ETRA embeds all the elements required for powering the unit, therefore power sequencing is self-contained and simplified. Nevertheless, power must be provided from carrier board, and therefore users should be aware of the ranges power supply can assume as well as all other parameters.

Hardware versioning and tracking[edit | edit source]

ETRA SOM implements well established versioning and tracking mechanisms:

- PCB version is copper printed on PCB itself, as shown in Fig. 1

- serial number: it is printed on a white label, as shown in Fig. 2: see also Product serial number page for more details

- ConfigID: it is used by software running on the board for the identification of the product model/hardware configuration. For more details, please refer to this link

- on ETRA SOM ConfigID is stored in the OTP area

| Section not completed yet |

Part number composition[edit | edit source]

ETRA SOM part number is identified by the following digit-code table:

| Part number structure | Options | Description |

|---|---|---|

| Family | DSDA | Family prefix code |

| SOC |

|

Other versions can be available, please contact technical support |

| NOR SPI |

|

|

| RAM |

|

|

| Storage |

|

eMMC and NAND SLC cannot be present at the same time. Other versions can be available, please contact technical support |

| Boot Mode/BUS expander |

|

These options depends on Storage. Other versions can be available, please contact technical support |

| RFU |

|

|

| Temperature range |

|

Other versions can be available, please contact technical support For the DAVE Embedded Systems' product Temperature Range classification, please find more information at the page Products Classification |

| PCB revision |

|

PCB release may change for manufacturing purposes (i.e. text fixture adaptation) |

| Manufacturing option |

|

typically connected to production process and quality |

| Software Configuration |

|

If customers require custom SW deployed this section should be defined and agreed. Please contact technical support |

Example[edit | edit source]

ETRA SOM code DSDAB59200I0R-00

- DSDA - ETRA SOM

- B - STM32MP151DAB3 Single core -40/125°C 800MHz

- 5 - 32MB

- 9 - 512MB DDR3L

- 2 - 4GB eMMC

- 0 - on board eMMC, BUS expander mount

- 0 - RFU

- I - Industrial grade: -40 to +85°C

- 0 - first version

- R - RoHS compliant

- -00 - standard factory u-boot pre-programmed

Pinout Table[edit | edit source]

Connectors and Pinout Table[edit | edit source]

Connectors description[edit | edit source]

In the following table are described all available connectors integrated on ETRA SOM:

| Connector name | Connector Type | Notes | Carrier board counterpart |

|---|---|---|---|

| J1 | SODIMM DDR3 edge connector 204 pin | TE Connectivity 2-2013289-1 |

The dedicated carrier board must mount the mating connector and connect the desired peripheral interfaces according to ETRA pinout specifications. See the images below for reference:

Pinout table naming conventions[edit | edit source]

This chapter contains the pinout description of the ETRA module, grouped in two tables (odd and even pins) that report the pin mapping of the SODIMM-DDR3 edge connector.

Each row in the pinout tables contains the following information:

| Pin | Reference to the connector pin |

| Pin Name | Pin (signal) name on the ETRA connectors |

| Internal connections |

Connections to the ETRA components

|

| Ball/pin # | Component ball/pin number connected to signal |

| Voltage | I/O voltage levels |

| Type | Pin type:

|

| Notes | Remarks on special pin characteristics |

| Pin MUX alternative functions | Muxes:

The number of functions depends on platform |

Pinout table XLS file[edit | edit source]

For your convenience, please find a spreadsheet with the STM32MP15x pinout and pinmux table here.

Pinout Table ODD pins declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Voltage domain | Type | Notes | Alternative Functions | |

|---|---|---|---|---|---|---|---|---|

| J1.1 | DGND | DGND | - | - | G | |||

| J1.3 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.5 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.7 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.9 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.11 | DGND | DGND | - | - | G | |||

| J1.13 | ETH_LED | LAN.LED0/PME_N1 | 23 | VDD | I/O | |||

| J1.15 | VINTLDO | PMIC.INTLDO | 40 | INTLDO | S | do not connect | ||

| J1.17 | DGND | DGND | - | - | G | |||

| J1.19 | ETH_TX_P | LAN.TXP | 6 | - | D | |||

| J1.21 | ETH_TX_M | LAN.TXM | 5 | - | D | |||

| J1.23 | ETH_RX_P | LAN.RXP | 4 | - | D | |||

| J1.25 | ETH_RX_M | LAN.RXM | 3 | - | D | |||

| J1.27 | LDO2 | PMIC.LDO2OUT | 18 | LDO2 | S | Spare LDO output | ||

| J1.29 | LDO5 | PMIC.LDO5OUT | 20 | LDO5 | S | Spare LDO output | ||

| J1.31 | - | NC | - | - | - | |||

| J1.33 | ETH_INT | LAN.INTRP | 18 | VDD | O | open drain with internal pull-up to VDD | ||

| J1.35 | DGND | DGND | - | - | G | |||

| J1.37

(NAND on board) |

PD1 | CPU.PD1 | A4 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.37 | PD1 | CPU.PD1 | A4 | VDD | I/O | Pin AF2 | I2C6_SCL | |

| Pin AF3 | DFSDM1_DATIN6 | |||||||

| Pin AF4 | I2C5_SCL | |||||||

| Pin AF6 | SAI3_SD_A | |||||||

| Pin AF8 | UART4_TX | |||||||

| Pin AF9 | FDCAN1_TX | |||||||

| Pin AF10 | SDMMC3_D0 | |||||||

| Pin AF11 | DFSDM1_CKIN7 | |||||||

| Pin AF12 | FMC_AD3/FMC_D3 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.39

(NAND on board) |

PD4 | CPU.PD4 | D6 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.39 | PD4 | CPU.PD4 | D6 | VDD | I/O | Pin AF6 | SAI3_FS_A | |

| Pin AF7 | USART2_RTS/USART2_DE | |||||||

| Pin AF10 | SDMMC3_D1 | |||||||

| Pin AF11 | DFSDM1_CKIN0 | |||||||

| Pin AF12 | FMC_NOE | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.41

(NAND on board) |

PD5 | CPU.PD5 | D7 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.41 | PD5 | CPU.PD5 | D7 | VDD | I/O | Pin AF7 | USART2_TX | |

| Pin AF10 | SDMMC3_D2 | |||||||

| Pin AF12 | FMC_NWE | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.43 | PD7 | CPU.PD7 | B4 | VDD | I/O | Pin AF0 | TRACED6 | |

| Pin AF3 | DFSDM1_DATIN4 | |||||||

| Pin AF4 | I2C2_SCL | |||||||

| Pin AF6 | DFSDM1_CKIN1 | |||||||

| Pin AF7 | USART2_CK | |||||||

| Pin AF9 | SPDIFRX_IN1 | |||||||

| Pin AF10 | SDMMC3_D3 | |||||||

| Pin AF12 | FMC_NE1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.45

(NAND on board) |

PD0 | CPU.PD0 | A3 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.45 | PD0 | CPU.PD0 | A3 | VDD | I/O | Pin AF2 | I2C6_SDA | |

| Pin AF3 | DFSDM1_CKIN6 | |||||||

| Pin AF4 | I2C5_SDA | |||||||

| Pin AF6 | SAI3_SCK_A | |||||||

| Pin AF8 | UART4_RX | |||||||

| Pin AF9 | FDCAN1_RX | |||||||

| Pin AF10 | SDMMC3_CMD | |||||||

| Pin AF11 | DFSDM1_DATIN7 | |||||||

| Pin AF12 | FMC_AD2/FMC_D2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.47 | PG15 | CPU.PG15 | A2 | VDD | I/O | Pin AF0 | TRACED7 | |

| Pin AF2 | SAI1_D2 | |||||||

| Pin AF4 | I2C2_SDA | |||||||

| Pin AF6 | SAI1_FS_A | |||||||

| Pin AF7 | USART6_CTS/USART6_NSS | |||||||

| Pin AF10 | SDMMC3_CK | |||||||

| Pin AF13 | DCMI_D13 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.49

(NOR on board) |

PF10 | CPU.PF10 | U9 | VDD | I/O | internally used for NOR flash,

do not connect |

||

| J1.49 | PF10 | CPU.PF10 | U9 | VDD | I/O | Pin AF1 | TIM16_BKIN | |

| Pin AF2 | SAI1_D3 | |||||||

| Pin AF3 | SAI4_D4 | |||||||

| Pin AF6 | SAI1_D4 | |||||||

| Pin AF9 | QUADSPI_CLK | |||||||

| Pin AF12 | SAI4_D3 | |||||||

| Pin AF13 | DCMI_D11 | |||||||

| Pin AF14 | LCD_DE | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.51

(NAND on board) |

PE7 | CPU.PE7 | T10 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.51 | PE7 | CPU.PE7 | T10 | VDD | I/O | Pin AF1 | TIM1_ETR | |

| Pin AF2 | TIM3_ETR | |||||||

| Pin AF3 | DFSDM1_DATIN2 | |||||||

| Pin AF7 | UART7_RX | |||||||

| Pin AF10 | QUADSPI_BK2_IO0 | |||||||

| Pin AF12 | FMC_AD4/FMC_D4 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.53

(NAND on board) |

PE8 | CPU.PE8 | T11 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.53 | PE8 | CPU.PE8 | T11 | VDD | I/O | Pin AF1 | TIM1_CH1N | |

| Pin AF3 | DFSDM1_CKIN2 | |||||||

| Pin AF7 | UART7_TX | |||||||

| Pin AF10 | QUADSPI_BK2_IO1 | |||||||

| Pin AF12 | FMC_AD5/FMC_D5 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.55 | NOR_WP# | NOR.WPn | C4 | VDD | I/O | internal pull-up to VDD,

this NOR pin is shared with QSPI_IO2 function |

||

| J1.57 | DGND | DGND | - | - | G | |||

| J1.59 | - | NC | - | - | - | |||

| J1.61

(eMMC on board) |

PB14 | CPU.PB14 | C9 | VDD | I/O | internally used for eMMC flash,

do not connect |

||

| J1.61 | PB14 | CPU.PB14 | C9 | VDD | I/O | Pin AF1 | TIM1_CH2N | |

| Pin AF2 | TIM12_CH1 | |||||||

| Pin AF3 | TIM8_CH2N | |||||||

| Pin AF4 | USART1_TX | |||||||

| Pin AF5 | SPI2_MISO/I2S2_SDI | |||||||

| Pin AF6 | DFSDM1_DATIN2 | |||||||

| Pin AF7 | USART3_RTS/USART3_DE | |||||||

| Pin AF9 | SDMMC2_D0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.63

(eMMC on board) |

PB15 | CPU.PB15 | A8 | VDD | I/O | internally used for eMMC flash,

do not connect |

||

| J1.63 | PB15 | CPU.PB15 | A8 | VDD | I/O | Pin AF0 | RTC_REFIN | |

| Pin AF1 | TIM1_CH3N | |||||||

| Pin AF2 | TIM12_CH2 | |||||||

| Pin AF3 | TIM8_CH3N | |||||||

| Pin AF4 | USART1_RX | |||||||

| Pin AF5 | SPI2_MOSI/I2S2_SDO | |||||||

| Pin AF6 | DFSDM1_CKIN2 | |||||||

| Pin AF9 | SDMMC2_D1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.65

(eMMC on board) |

PB3 | CPU.PB3 | A7 | VDD | I/O | internally used for eMMC flash,

do not connect |

||

| J1.65 | PB3 | CPU.PB3 | A7 | VDD | I/O | Pin AF0 | TRACED9 | |

| Pin AF1 | TIM2_CH2 | |||||||

| Pin AF4 | SAI4_CK1 | |||||||

| Pin AF5 | SPI1_SCK/I2S1_CK | |||||||

| Pin AF6 | SPI3_SCK/I2S3_CK | |||||||

| Pin AF8 | SPI6_SCK | |||||||

| Pin AF9 | SDMMC2_D2 | |||||||

| Pin AF12 | SAI4_MCLK_A | |||||||

| Pin AF13 | UART7_RX | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.67

(eMMC on board) |

PB4 | CPU.PB4 | B9 | VDD | I/O | internally used for eMMC flash,

do not connect |

||

| J1.67 | PB4 | CPU.PB4 | B9 | VDD | I/O | Pin AF0 | TRACED8 | |

| Pin AF1 | TIM16_BKIN | |||||||

| Pin AF2 | TIM3_CH1 | |||||||

| Pin AF4 | SAI4_CK2 | |||||||

| Pin AF5 | SPI1_MISO/I2S1_SDI | |||||||

| Pin AF6 | SPI3_MISO/I2S3_SDI | |||||||

| Pin AF7 | SPI2_NSS/I2S2_WS | |||||||

| Pin AF8 | SPI6_MISO | |||||||

| Pin AF9 | SDMMC2_D3 | |||||||

| Pin AF12 | SAI4_SCK_A | |||||||

| Pin AF13 | UART7_TX | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.69

(eMMC on board) |

PG6 | CPU.PG6 | A6 | VDD | I/O | internally used for eMMC flash,

do not connect |

||

| J1.69 | PG6 | CPU.PG6 | A6 | VDD | I/O | Pin AF0 | TRACED14 | |

| Pin AF1 | TIM17_BKIN | |||||||

| Pin AF10 | SDMMC2_CMD | |||||||

| Pin AF13 | DCMI_D12 | |||||||

| Pin AF14 | LCD_R7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.71

(eMMC on board) |

PE3 | CPU.PE3 | A5 | VDD | I/O | internally used for eMMC flash,

do not connect |

||

| J1.71 | PE3 | CPU.PE3 | A5 | VDD | I/O | Pin AF0 | TRACED0 | |

| Pin AF4 | TIM15_BKIN | |||||||

| Pin AF6 | SAI1_SD_B | |||||||

| Pin AF9 | SDMMC2_CK | |||||||

| Pin AF12 | FMC_A19 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.73 | DGND | DGND | - | - | G | |||

| J1.75 | PC8 | CPU.PC8 | C11 | VDD | I/O | Pin AF0 | TRACED0 | |

| Pin AF2 | TIM3_CH3 | |||||||

| Pin AF3 | TIM8_CH3 | |||||||

| Pin AF6 | UART4_TX | |||||||

| Pin AF7 | USART6_CK | |||||||

| Pin AF8 | UART5_RTS/UART5_DE | |||||||

| Pin AF12 | SDMMC1_D0 | |||||||

| Pin AF13 | DCMI_D2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.77 | PC9 | CPU.PC9 | A10 | VDD | I/O | Pin AF0 | TRACED1 | |

| Pin AF2 | TIM3_CH4 | |||||||

| Pin AF3 | TIM8_CH4 | |||||||

| Pin AF4 | I2C3_SDA | |||||||

| Pin AF5 | I2S_CKIN | |||||||

| Pin AF8 | UART5_CTS | |||||||

| Pin AF9 | QUADSPI_BK1_IO0 | |||||||

| Pin AF12 | SDMMC1_D1 | |||||||

| Pin AF13 | DCMI_D3 | |||||||

| Pin AF14 | LCD_B2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.79 | PE6 | CPU.PE6 | B3 | VDD | I/O | for LCD_G1 function

use pin J1.180 (RGB lenght match) |

Pin AF0 | TRACED2 |

| Pin AF1 | TIM1_BKIN2 | |||||||

| Pin AF2 | SAI1_D1 | |||||||

| Pin AF4 | TIM15_CH2 | |||||||

| Pin AF5 | SPI4_MOSI | |||||||

| Pin AF6 | SAI1_SD_A | |||||||

| Pin AF7 | SDMMC2_D0 | |||||||

| Pin AF8 | SDMMC1_D2 | |||||||

| Pin AF10 | SAI2_MCLK_B | |||||||

| Pin AF12 | FMC_A22 | |||||||

| Pin AF13 | DCMI_D7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.81 | PC11 | CPU.PC11 | A11 | VDD | I/O | Pin AF0 | TRACED3 | |

| Pin AF3 | DFSDM1_DATIN5 | |||||||

| Pin AF6 | SPI3_MISO/I2S3_SDI | |||||||

| Pin AF7 | USART3_RX | |||||||

| Pin AF8 | UART4_RX | |||||||

| Pin AF9 | QUADSPI_BK2_NCS | |||||||

| Pin AF10 | SAI4_SCK_B | |||||||

| Pin AF12 | SDMMC1_D3 | |||||||

| Pin AF13 | DCMI_D4 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.83 | PD2 | CPU.PD2 | B10 | VDD | I/O | Pin AF2 | TIM3_ETR | |

| Pin AF4 | I2C5_SMBA | |||||||

| Pin AF6 | UART4_RX | |||||||

| Pin AF8 | UART5_RX | |||||||

| Pin AF12 | SDMMC1_CMD | |||||||

| Pin AF13 | DCMI_D11 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.85 | PC12 | CPU.PC12 | C10 | VDD | I/O | Pin AF0 | TRACECLK | |

| Pin AF1 | MCO2 | |||||||

| Pin AF2 | SAI4_D3 | |||||||

| Pin AF6 | SPI3_MOSI/I2S3_SDO | |||||||

| Pin AF7 | USART3_CK | |||||||

| Pin AF8 | UART5_TX | |||||||

| Pin AF10 | SAI4_SD_B | |||||||

| Pin AF12 | SDMMC1_CK | |||||||

| Pin AF13 | DCMI_D9 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.87 | DGND | DGND | - | - | G | |||

| J1.89 | PD8 | CPU.PD8 | F2 | VDD | I/O | Pin AF3 | DFSDM1_CKIN3 | |

| Pin AF6 | SAI3_SCK_B | |||||||

| Pin AF7 | USART3_TX | |||||||

| Pin AF9 | SPDIFRX_IN2 | |||||||

| Pin AF12 | FMC_AD13/FMC_D13 | |||||||

| Pin AF14 | LCD_B7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.91 | PD9 | CPU.PD9 | G3 | VDD | I/O | Pin AF3 | DFSDM1_DATIN3 | |

| Pin AF6 | SAI3_SD_B | |||||||

| Pin AF7 | USART3_RX | |||||||

| Pin AF12 | FMC_AD14/FMC_D14 | |||||||

| Pin AF13 | DCMI_HSYNC | |||||||

| Pin AF14 | LCD_B0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.93

(I/O EXP on board) |

PC2 | CPU.PC2 | T2 | VDD | I/O | internally used for I/O EXP,

do not connect |

||

| J1.93 | PC2 | CPU.PC2 | T2 | VDD | I/O | Pin AF3 | DFSDM1_CKIN1 | |

| Pin AF5 | SPI2_MISO/I2S2_SDI | |||||||

| Pin AF6 | DFSDM1_CKOUT | |||||||

| Pin AF11 | ETH1_GMII_TXD2/

ETH1_MII_TXD2/ ETH1_RGMII_TXD2 | |||||||

| Pin AF13 | DCMI_PIXCLK | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP12

ADC1_INN11 | |||||||

| J1.95 | PA0 | CPU.PA0 | R3 | VDD | I/O | internally used for PMIC,

do not connect |

||

| J1.97 | PD13 | CPU.PD13 | U12 | VDD | I/O | Pin AF1 | LPTIM1_OUT | |

| Pin AF2 | TIM4_CH2 | |||||||

| Pin AF4 | I2C4_SDA | |||||||

| Pin AF5 | I2C1_SDA | |||||||

| Pin AF6 | I2S3_MCK | |||||||

| Pin AF8 | SDMMC1_D123DIR | |||||||

| Pin AF9 | QUADSPI_BK1_IO3 | |||||||

| Pin AF10 | SAI2_SCK_A | |||||||

| Pin AF12 | FMC_A18 | |||||||

| Pin AF13 | DSI_TE | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.99

(NAND on board) |

PD12 | CPU.PD12 | U11 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.99 | PD12 | CPU.PD12 | U11 | VDD | I/O | Pin AF1 | LPTIM1_IN1 | |

| Pin AF2 | TIM4_CH1 | |||||||

| Pin AF3 | LPTIM2_IN1 | |||||||

| Pin AF4 | I2C4_SCL | |||||||

| Pin AF5 | I2C1_SCL | |||||||

| Pin AF7 | USART3_RTS/USART3_DE | |||||||

| Pin AF9 | QUADSPI_BK1_IO1 | |||||||

| Pin AF10 | SAI2_FS_A | |||||||

| Pin AF12 | FMC_A17/FMC_ALE | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.101

(NAND on board) |

PD11 | CPU.PD11 | V8 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.101 | PD11 | CPU.PD11 | V8 | VDD | I/O | Pin AF3 | LPTIM2_IN2 | |

| Pin AF4 | I2C4_SMBA | |||||||

| Pin AF5 | I2C1_SMBA | |||||||

| Pin AF7 | USART3_CTS/USART3_NSS | |||||||

| Pin AF9 | QUADSPI_BK1_IO0 | |||||||

| Pin AF10 | SAI2_SD_A | |||||||

| Pin AF12 | FMC_A16/FMC_CLE | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.103 | - | NC | - | - | - | |||

| J1.105

(NAND on board) |

PG9 | CPU.PG9 | T14 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.105 | PG9 | CPU.PG9 | T14 | VDD | I/O | Pin AF0 | DBTRGO | |

| Pin AF7 | USART6_RX | |||||||

| Pin AF8 | SPDIFRX_IN4 | |||||||

| Pin AF9 | QUADSPI_BK2_IO2 | |||||||

| Pin AF10 | SAI2_FS_B | |||||||

| Pin AF12 | FMC_NE2/FMC_NCE | |||||||

| Pin AF13 | DCMI_VSYNC | |||||||

| Pin AF14 | LCD_R1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.107 | - | NC | - | - | - | |||

| J1.109 | DGND | DGND | - | - | G | |||

| J1.111 | DSI_CKN | CPU.DSI_CKN | A14 | - | D | |||

| J1.113 | DSI_CKP | CPU.DSI_CKP | B14 | - | D | |||

| J1.115 | DSI_D0N | CPU.DSI_D0N | A13 | - | D | |||

| J1.117 | DSI_D0P | DSI_D0P | B13 | - | D | |||

| J1.119 | DSI_D1N | CPU.DSI_D1N | A15 | - | D | |||

| J1.121 | DSI_D1P | CPU.DSI_D1P | B15 | - | D | |||

| J1.123 | - | NC | - | - | - | |||

| J1.125 | - | NC | - | - | - | |||

| J1.127 | - | NC | - | - | - | |||

| J1.129 | - | NC | - | - | - | |||

| J1.131 | DGND | DGND | - | - | G | |||

| J1.133 | ADP5589_R7 | EXP.R7 | 1 | VDD | I/O | Pin AF0 | Keypad row 7 | |

| Pin AF5 | GPIO 8 | |||||||

| J1.135 | ADP5589_R6 | EXP.R6 | 2 | VDD | I/O | Pin AF0 | Keypad row 6 | |

| Pin AF5 | GPIO 7 | |||||||

| J1.137 | ADP5589_R5 | EXP.R5 | 3 | VDD | I/O | Pin AF0 | Keypad row 5 | |

| Pin AF5 | GPIO 6 | |||||||

| J1.139 | ADP5589_R4 | EXP.R4 | 4 | VDD | I/O | Pin AF0 | Keypad row 4 | |

| Pin AF1 | RESET1 | |||||||

| Pin AF5 | GPIO 5 | |||||||

| J1.141 | ADP5589_R3 | EXP.R3 | 5 | VDD | I/O | Pin AF0 | Keypad row 3 | |

| Pin AF1 | Logic LC1 | |||||||

| Pin AF2 | PWM_OUT | |||||||

| Pin AF3 | CLK_OUT | |||||||

| Pin AF5 | GPIO 4 | |||||||

| J1.143 | ADP5589_R2 | EXP.R2 | 6 | VDD | I/O | Pin AF0 | Keypad row 2 | |

| Pin AF1 | LOGIC LB1 | |||||||

| Pin AF5 | GPIO 3 | |||||||

| J1.145 | ADP5589_R1 | EXP.R1 | 7 | VDD | I/O | Pin AF0 | Keypad row 1 | |

| Pin AF1 | Logic LA1 | |||||||

| Pin AF5 | GPIO 2 | |||||||

| J1.147 | ADP5589_R0 | EXP.R0 | 8 | VDD | I/O | Pin AF0 | Keypad row 0 | |

| Pin AF1 | Logic LY1 | |||||||

| Pin AF5 | GPIO 1 | |||||||

| J1.149 | ADP5589_C0 | EXP.C0 | 9 | VDD | I/O | Pin AF0 | Keypad column 0 | |

| Pin AF5 | GPIO 9 | |||||||

| J1.151 | ADP5589_C1 | EXP.C1 | 10 | VDD | I/O | Pin AF0 | Keypad column 1 | |

| Pin AF5 | GPIO 10 | |||||||

| J1.153 | DGND | DGND | - | - | G | |||

| J1.155 | ADP5589_C2 | EXP.C2 | 11 | VDD | I/O | Pin AF0 | Keypad column 2 | |

| Pin AF5 | GPIO 11 | |||||||

| J1.157 | ADP5589_C3 | EXP.C3 | 12 | VDD | I/O | Pin AF0 | Keypad column 3 | |

| Pin AF5 | GPIO 12 | |||||||

| J1.159 | ADP5589_C4 | EXP.C4 | 13 | VDD | I/O | Pin AF0 | Keypad column 4 | |

| Pin AF1 | RESET2 | |||||||

| Pin AF5 | GPIO 13 | |||||||

| J1.161 | ADP5589_C5 | EXP.C5 | 14 | VDD | I/O | Pin AF0 | Keypad column 5 | |

| Pin AF5 | GPIO 14 | |||||||

| J1.163 | ADP5589_C6 | EXP.C6 | 15 | VDD | I/O | Pin AF0 | Keypad column 6 | |

| Pin AF1 | Logic LC2 | |||||||

| Pin AF2 | PWM_IN | |||||||

| Pin AF3 | CLK_IN | |||||||

| Pin AF5 | GPIO 15 | |||||||

| J1.165 | ADP5589_C7 | EXP.C7 | 16 | VDD | I/O | Pin AF0 | Keypad column 7 | |

| Pin AF1 | Logic LB2 | |||||||

| Pin AF5 | GPIO 16 | |||||||

| J1.167 | ADP5589_C8 | EXP.C8 | 19 | VDD | I/O | Pin AF0 | Keypad column 8 | |

| Pin AF1 | Logic LA2 | |||||||

| Pin AF5 | GPIO 17 | |||||||

| J1.169 | ADP5589_C9 | EXP.C9 | 20 | VDD | I/O | Pin AF0 | Keypad column 9 | |

| Pin AF1 | Logic LY2 | |||||||

| Pin AF5 | GPIO 18 | |||||||

| J1.171 | ADP5589_C10 | EXP.C10 | 21 | VDD | I/O | Pin AF0 | Keypad column 10 | |

| Pin AF5 | GPIO 19 | |||||||

| J1.173 | - | NC | - | - | - | |||

| J1.175 | DGND | DGND | - | - | G | |||

| J1.177

(NAND on board) |

PE9 | CPU.PE9 | W7 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.177 | PE9 | CPU.PE9 | W7 | VDD | I/O | Pin AF1 | TIM1_CH1 | |

| Pin AF3 | DFSDM1_CKOUT | |||||||

| Pin AF7 | UART7_RTS/UART7_DE | |||||||

| Pin AF10 | QUADSPI_BK2_IO2 | |||||||

| Pin AF12 | FMC_AD6/FMC_D6 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.179

(I/O EXP on board) |

PC3 | CPU.PC3 | T3 | VDD | I/O | internally used for I/O EXP,

do not connect |

||

| J1.179 | PC3 | CPU.PC3 | T3 | VDD | I/O | Pin AF0 | TRACECLK | |

| Pin AF3 | DFSDM1_DATIN1 | |||||||

| Pin AF5 | SPI2_MOSI/I2S2_SDO | |||||||

| Pin AF11 | ETH1_GMII_TX_CLK/

ETH1_MII_TX_CLK | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP13

ADC1_INN12 | |||||||

| J1.181

(NAND on board) |

PD6 | CPU.PD6 | E3 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.181 | PD6 | CPU.PD6 | E3 | VDD | I/O | Pin AF1 | TIM16_CH1N | |

| Pin AF2 | SAI1_D1 | |||||||

| Pin AF3 | DFSDM1_CKIN4 | |||||||

| Pin AF4 | DFSDM1_DATIN1 | |||||||

| Pin AF5 | SPI3_MOSI/I2S3_SDO | |||||||

| Pin AF6 | SAI1_SD_A | |||||||

| Pin AF7 | USART2_RX | |||||||

| Pin AF12 | FMC_NWAIT | |||||||

| Pin AF13 | DCMI_D10 | |||||||

| Pin AF14 | LCD_B2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.183

(NAND on board) |

PE10 | CPU.PE10 | V10 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.183 | PE10 | CPU.PE10 | V10 | VDD | I/O | Pin AF1 | TIM1_CH2N | |

| Pin AF3 | DFSDM1_DATIN4 | |||||||

| Pin AF7 | UART7_CTS | |||||||

| Pin AF10 | QUADSPI_BK2_IO3 | |||||||

| Pin AF12 | FMC_AD7/FMC_D7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.185 | VBUS_OTG_OUT | PMIC.VBUSOTG | 35 | VBUSOTG | S | USB OTG VOUT | ||

| J1.187 | PG11 | CPU.PG11 | V6 | VDD | I/O | Pin AF0 | TRACED11 | |

| Pin AF4 | USART1_TX | |||||||

| Pin AF6 | UART4_TX | |||||||

| Pin AF8 | SPDIFRX_IN1 | |||||||

| Pin AF11 | ETH1_GMII_TX_EN/

ETH1_MII_TX_EN/ ETH1_RGMII_TX_CTL/ ETH1_RMII_TX_EN | |||||||

| Pin AF13 | DCMI_D3 | |||||||

| Pin AF14 | LCD_B3 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.189 | PB2 | CPU.PB2 | T13 | VDD | I/O | Pin AF0 | TRACED4 | |

| Pin AF1 | RTC_OUT2 | |||||||

| Pin AF2 | SAI1_D1 | |||||||

| Pin AF3 | DFSDM1_CKIN1 | |||||||

| Pin AF4 | USART1_RX | |||||||

| Pin AF5 | I2S_CKIN | |||||||

| Pin AF6 | SAI1_SD_A | |||||||

| Pin AF7 | SPI3_MOSI/I2S3_SDO | |||||||

| Pin AF8 | UART4_RX | |||||||

| Pin AF9 | QUADSPI_CLK | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.191 | PE1 | CPU.PE1 | B1 | VDD | I/O | Pin AF1 | LPTIM1_IN2 | |

| Pin AF5 | I2S2_MCK | |||||||

| Pin AF6 | SAI3_SD_B | |||||||

| Pin AF8 | UART8_TX | |||||||

| Pin AF12 | FMC_NBL1 | |||||||

| Pin AF13 | DCMI_D3 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.193 | PE0 | CPU.PE0 | C4 | VDD | I/O | Pin AF1 | LPTIM1_ETR | |

| Pin AF2 | TIM4_ETR | |||||||

| Pin AF4 | LPTIM2_ETR | |||||||

| Pin AF5 | SPI3_SCK/I2S3_CK | |||||||

| Pin AF6 | SAI4_MCLK_B | |||||||

| Pin AF8 | UART8_RX | |||||||

| Pin AF10 | SAI2_MCLK_A | |||||||

| Pin AF12 | FMC_NBL0 | |||||||

| Pin AF13 | DCMI_D2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.195 | PE2 | CPU.PE2 | T1 | VDD | I/O | internally used for

PMIC I2C |

Pin AF4 | I2C4_SCL |

| J1.197

(LAN PHY on board) |

PA13 | CPU.PA13 | P2 | VDD | I/O | internally used for LAN PHY,

do not connect |

||

| J1.197 | PA13 | CPU.PA13 | P2 | VDD | I/O | Pin AF0 | DBTRGO | |

| Pin AF1 | DBTRGI | |||||||

| Pin AF2 | MCO1 | |||||||

| Pin AF8 | UART4_TX | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

BOOTFAILN | |||||||

| J1.199

(NAND on board) |

PD14 | CPU.PD14 | F3 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.199 | PD14 | CPU.PD14 | F3 | VDD | I/O | internally used for

NAND flash |

Pin AF2 | TIM4_CH3 |

| Pin AF6 | SAI3_MCLK_B | |||||||

| Pin AF8 | UART8_CTS | |||||||

| Pin AF12 | FMC_AD0/FMC_D0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.201

(NAND on board) |

PD15 | CPU.PD15 | G1 | VDD | I/O | internally used for NAND flash,

do not connect |

||

| J1.201 | PD15 | CPU.PD15 | G1 | VDD | I/O | internally used for

NAND flash |

Pin AF2 | TIM4_CH4 |

| Pin AF6 | SAI3_MCLK_A | |||||||

| Pin AF8 | UART8_CTS | |||||||

| Pin AF12 | FMC_AD1/FMC_D1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.203 | DGND | DGND | - | - | G | |||

Pinout Table EVEN pins declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Voltage domain | Type | Notes | Alternative Functions | |

|---|---|---|---|---|---|---|---|---|

| J1.2 | DGND | DGND | - | - | G | |||

| J1.4 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.6 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.8 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.10 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.12 | DGND | DGND | - | - | G | |||

| J1.14 | VBAT | CPU.VBAT | H3 | VBAT | S | BACKUP VOLTAGE | ||

| J1.16 | PONKEYn | PMIC.PONKEYN | 17 | 3.3VIN | I | |||

| J1.18 | SOM_PGOOD | - | - | VDD | O | internally connected to VDD | ||

| J1.20 | BOOT_MODE0 | CPU.BOOT0 | K1 | VDD | I | internal pull-up or pull-down

according to specific model |

||

| J1.22 | PWR_ON | CPU.PWR_ON | L1 | VDD | O | |||

| J1.24 | NRST | CPU.NRST

PMIC.RSTN eMMC.RST_n NOR.NRESET |

J1

1 K5 A4 |

VDD | I/O | internal 10k pull-up to VDD | ||

| J1.26 | BOOT_MODE1 | CPU.BOOT1 | K4 | VDD | I | internal pull-up or pull-down

according to specific model |

||

| J1.28 | PA9 | CPU.PA9 | C8 | VDD | I/O | Pin AF1 | TIM1_CH2 | |

| Pin AF4 | I2C3_SMBA | |||||||

| Pin AF5 | SPI2_SCK/I2S2_CK | |||||||

| Pin AF7 | USART1_TX | |||||||

| Pin AF8 | SDMMC2_CDIR | |||||||

| Pin AF10 | SDMMC2_D5 | |||||||

| Pin AF13 | DCMI_D0 | |||||||

| Pin AF14 | LCD_R5 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.30 | DGND | DGND | - | - | G | |||

| J1.32 | WAKEUP | PMIC.WAKEUP | 2 | VINTLDO | I | |||

| J1.34 | PB13 | CPU.PB13 | T9 | VDD | I/O | Pin AF1 | TIM1_CH1N | |

| Pin AF3 | DFSDM1_CKOUT | |||||||

| Pin AF4 | LPTIM2_OUT | |||||||

| Pin AF5 | SPI2_SCK/I2S2_CK | |||||||

| Pin AF6 | DFSDM1_CKIN1 | |||||||

| Pin AF7 | USART3_CTS/USART3_NSS | |||||||

| Pin AF9 | FDCAN2_TX | |||||||

| Pin AF11 | ETH1_GMII_TXD1/

ETH1_MII_TXD1/ ETH1_RGMII_TXD1/ ETH1_RMII_TXD1 | |||||||

| Pin AF14 | UART5_TX | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.36 | BOOT_MODE2 | CPU-BOOT2 | L2 | VDD | I | internal pull-up or pull-down

according to specific model |

||

| J1.38 | PA11 | CPU.PA11 | V17 | VDD | I/O | Pin AF1 | TIM1_CH4 | |

| Pin AF2 | I2C6_SCL | |||||||

| Pin AF4 | I2C5_SCL | |||||||

| Pin AF5 | SPI2_NSS/I2S2_WS | |||||||

| Pin AF6 | UART4_RX | |||||||

| Pin AF7 | USART1_CTS/USART1_NSS | |||||||

| Pin AF9 | FDCAN1_RX | |||||||

| Pin AF14 | LCD_R4 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

OTG_FS_DM | |||||||

| J1.40 | NAND_WP# | NAND.WPn | 19 | VDD | I/O | internal pull-up to VDD | ||

| J1.42

(NOR on board) |

PB6 | CPU.PB6 | T12 | VDD | I/O | internally used for NOR flash.

do not connect |

||

| J1.42 | PB6 | CPU.PB6 | T12 | VDD | I/O | Pin AF1 | TIM16_CH1N | |

| Pin AF2 | TIM4_CH1 | |||||||

| Pin AF4 | I2C1_SCL | |||||||

| Pin AF5 | CEC | |||||||

| Pin AF6 | I2C4_SCL | |||||||

| Pin AF7 | USART1_TX | |||||||

| Pin AF9 | FDCAN2_TX | |||||||

| Pin AF10 | QUADSPI_BK1_NCS | |||||||

| Pin AF11 | DFSDM1_DATIN5 | |||||||

| Pin AF12 | UART5_TX | |||||||

| Pin AF13 | DCMI_D5 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.44 | PB7 | CPU.PB7 | B5 | VDD | I/O | internally used for

PMIC I2C |

Pin AF6 | I2C1_SDA |

| J1.46 | PE14 | CPU.PE14 | D3 | VDD | I/O | Pin AF1 | TIM1_CH4 | |

| Pin AF5 | SPI4_MOSI | |||||||

| Pin AF8 | UART8_RTS/UART8_DE | |||||||

| Pin AF10 | SAI2_MCLK_B | |||||||

| Pin AF11 | SDMMC1_D123DIR | |||||||

| Pin AF12 | FMC_AD11/FMC_D11 | |||||||

| Pin AF13 | LCD_G0 | |||||||

| Pin AF14 | LCD_CLK | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.48 | PA12 | CPU.PA12 | U16 | VDD | I/O | Pin AF1 | TIM1_ETR | |

| Pin AF2 | I2C6_SDA | |||||||

| Pin AF4 | I2C5_SDA | |||||||

| Pin AF6 | UART4_TX | |||||||

| Pin AF7 | USART1_RTS/USART1_DE | |||||||

| Pin AF8 | SAI2_FS_B | |||||||

| Pin AF9 | FDCAN1_TX | |||||||

| Pin AF14 | LCD_R5 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

OTG_FS_DP | |||||||

| J1.50 | BST_OUT | PMIC.BST_OUT | 34 | BST_OUT | S | BOOST OUTPUT | ||

| J1.52 | BST_OUT | PMIC.BST_OUT | 34 | BST_OUT | S | BOOST OUTPUT | ||

| J1.54 | PMIC_INT# | PMIC-INTN | 43 | VDD | O | |||

| J1.56 | DGND | DGND | - | - | G | |||

| J1.58 | PA14 | CPU.PA14 | R1 | VDD | I/O | Pin AF0 | DBTRGO | |

| Pin AF1 | DBTRGI | |||||||

| Pin AF2 | MCO2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.60 | VDD | VOLTAGE OUTPUT | - | VDD | S | |||

| J1.62 | VDD | VOLTAGE OUTPUT | - | VDD | S | |||

| J1.64 | 1V8 | PMIC.LDO6OUT | 21 | 1V8 | S | Spare LDO output | ||

| J1.66 | PG12 | CPU.PG12 | F1 | VDD | I/O | Pin AF1 | LPTIM1_IN1 | |

| Pin AF5 | SPI6_MISO | |||||||

| Pin AF6 | SAI4_CK2 | |||||||

| Pin AF7 | USART6_RTS/USART6_DE | |||||||

| Pin AF8 | SPDIFRX_IN2 | |||||||

| Pin AF9 | LCD_B4 | |||||||

| Pin AF10 | SAI4_SCK_A | |||||||

| Pin AF11 | ETH1_PHY_INTN | |||||||

| Pin AF12 | FMC_NE4 | |||||||

| Pin AF14 | LCD_B1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.68 | PB5 | CPU.PB5 | T8 | VDD | I/O | Pin AF0 | ETH_CLK | |

| Pin AF1 | TIM17_BKIN | |||||||

| Pin AF2 | TIM3_CH2 | |||||||

| Pin AF3 | SAI4_D1 | |||||||

| Pin AF4 | I2C1_SMBA | |||||||

| Pin AF5 | SPI1_MOSI/I2S1_SDO | |||||||

| Pin AF6 | I2C4_SMBA | |||||||

| Pin AF7 | SPI3_MOSI/I2S3_SDO | |||||||

| Pin AF8 | SPI6_MOSI | |||||||

| Pin AF9 | FDCAN2_RX | |||||||

| Pin AF10 | SAI4_SD_A | |||||||

| Pin AF11 | ETH1_PPS_OUT | |||||||

| Pin AF12 | UART5_RX | |||||||

| Pin AF13 | DCMI_D10 | |||||||

| Pin AF14 | LCD_G7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.70 | PG8 | CPU.PG8 | U7 | VDD | I/O | Pin AF0 | TRACED15 | |

| Pin AF1 | TIM2_CH1/TIM2_ETR | |||||||

| Pin AF2 | ETH_CLK | |||||||

| Pin AF3 | TIM8_ETR | |||||||

| Pin AF5 | SPI6_NSS | |||||||

| Pin AF6 | SAI4_D2 | |||||||

| Pin AF7 | USART6_RTS/USART6_DE | |||||||

| Pin AF8 | USART3_RTS/USART3_DE | |||||||

| Pin AF9 | SPDIFRX_IN3 | |||||||

| Pin AF10 | SAI4_FS_A | |||||||

| Pin AF11 | ETH1_PPS_OUT | |||||||

| Pin AF14 | LCD_G7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.72 | PA8 | CPU.PA8 | B8 | VDD | I/O | Pin AF0 | MCO1 | |

| Pin AF1 | TIM1_CH1 | |||||||

| Pin AF3 | TIM8_BKIN2 | |||||||

| Pin AF4 | I2C3_SCL | |||||||

| Pin AF5 | SPI3_MOSI/I2S3_SDO | |||||||

| Pin AF7 | USART1_CK | |||||||

| Pin AF8 | SDMMC2_CKIN | |||||||

| Pin AF9 | SDMMC2_D4 | |||||||

| Pin AF10 | OTG_FS_SOF/OTG_HS_SOF | |||||||

| Pin AF12 | SAI4_SD_B | |||||||

| Pin AF13 | UART7_RX | |||||||

| Pin AF14 | LCD_R6 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.74

(NOR on board) |

PF7 | CPU.PF7 | W8 | VDD | I/O | internally used for NOR flash.

do not connect |

||

| J1.74 | PF7 | CPU.PF7 | W8 | VDD | I/O | Pin AF1 | TIM17_CH1 | |

| Pin AF5 | SPI5_SCK | |||||||

| Pin AF6 | SAI1_MCLK_B | |||||||

| Pin AF7 | UART7_TX | |||||||

| Pin AF9 | QUADSPI_BK1_IO2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.76

(NOR on board) |

PF9 | CPU.PF9 | W9 | VDD | I/O | internally used for NOR flash.

do not connect |

||

| J1.76 | PF9 | CPU.PF9 | W9 | VDD | I/O | Pin AF0 | TRACED13 | |

| Pin AF1 | TIM17_CH1N | |||||||

| Pin AF5 | SPI5_MOSI | |||||||

| Pin AF6 | SAI1_FS_B | |||||||

| Pin AF7 | UART7_CTS | |||||||

| Pin AF9 | TIM14_CH1 | |||||||

| Pin AF10 | QUADSPI_BK1_IO1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.78

(NOR on board) |

PF8 | CPU.PF8 | U10 | VDD | I/O | internally used for NOR flash.

do not connect |

||

| J1.78 | PF8 | CPU.PF8 | U10 | VDD | I/O | Pin AF0 | TRACED12 | |

| Pin AF1 | TIM16_CH1N | |||||||

| Pin AF5 | SPI5_MISO | |||||||

| Pin AF6 | SAI1_SCK_B | |||||||

| Pin AF7 | UART7_RTS/UART7_DE | |||||||

| Pin AF9 | TIM13_CH1 | |||||||

| Pin AF10 | QUADSPI_BK1_IO0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.80

(NOR on board) |

PF6 | CPU.PF6 | V9 | VDD | I/O | internally used for NOR flash.

do not connect |

||

| J1.80 | PF6 | CPU.PF6 | V9 | VDD | I/O | Pin AF1 | TIM16_CH1 | |

| Pin AF5 | SPI5_NSS | |||||||

| Pin AF6 | SAI1_SD_B | |||||||

| Pin AF7 | UART7_RX | |||||||

| Pin AF9 | QUADSPI_BK1_IO3 | |||||||

| Pin AF12 | SAI4_SCK_B | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.82 | DGND | DGND | - | - | G | |||

| J1.84 | PMIC_3V3 | VOLTAGE OUTPUT | - | PMIC_3V3 | S | |||

| J1.86 | PMIC_3V3 | VOLTAGE OUTPUT | - | PMIC_3V3 | S | |||

| J1.88 | PMIC_3V3 | VOLTAGE OUTPUT | - | PMIC_3V3 | S | |||

| J1.90 | JTMS-SWDIO | CPU.JTMS-SWDIO | D15 | VDD | I/O | |||

| J1.92 | JTDI | CPU.JTDI | D13 | VDD | I/O | |||

| J1.94 | NJTRST | CPU.NJTRST | D12 | VDD | I/O | |||

| J1.96 | JTDO-TRACESWOO | CPU.JTDO-TRACESWOO | D14 | VDD | I/O | |||

| J1.98 | JTCK-SWCLK | CPU.JTCK-SWCLK | D16 | VDD | I/O | |||

| J1.100 | DGND | DGND | - | - | G | |||

| J1.102 | NRST_CORE | CPU.NRST_CORE | J2 | VDD | I | internally connected to NRST | ||

| J1.104 | PDR_ON | CPU.PDR_ON | N2 | VDD | I | |||

| J1.106 | PDR_ON_CORE | CPU.PDR_ON_CORE | N1 | VDD | I | |||

| J1.108 | PWR_LP | CPU.PWR_LP | P1 | VDD | O | |||

| J1.110 | - | NC | - | - | - | |||

| J1.112 | - | NC | - | - | - | |||

| J1.114 | - | NC | - | - | - | |||

| J1.116 | - | NC | - | - | - | |||

| J1.118 | - | NC | - | - | - | |||

| J1.120 | - | NC | - | - | - | |||

| J1.122 | DGND | DGND | - | - | G | |||

| J1.124 | PE13 | CPU.PE13 | C2 | VDD | I/O | Pin AF0 | HDP2 | |

| Pin AF1 | TIM1_CH3 | |||||||

| Pin AF3 | DFSDM1_CKIN5 | |||||||

| Pin AF5 | SPI4_MISO | |||||||

| Pin AF10 | SAI2_FS_B | |||||||

| Pin AF12 | FMC_AD10/FMC_D10 | |||||||

| Pin AF13 | DCMI_D6 | |||||||

| Pin AF14 | LCD_DE | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.126 | PC13 | CPU.PC13 | K3 | VDD | I/O | internally used for PMIC,

do not connect |

||

| J1.128 | PA4 | CPU.PA4 | R4 | VDD | I/O | Pin AF0 | HDP0 | |

| Pin AF2 | TIM5_ETR | |||||||

| Pin AF4 | SAI4_D2 | |||||||

| Pin AF5 | SPI1_NSS/I2S1_WS | |||||||

| Pin AF6 | SPI3_NSS/I2S3_WS | |||||||

| Pin AF7 | USART2_CK | |||||||

| Pin AF8 | SPI6_NSS | |||||||

| Pin AF12 | SAI4_FS_A | |||||||

| Pin AF13 | DCMI_HSYNC | |||||||

| Pin AF14 | LCD_VSYNC | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP18

ADC2_INP18 DAC_OUT1 | |||||||

| J1.130

(eMMC 8-bit on board) |

PC6_OPT | CPU.PC6 | D10 | VDD | I/O | internally used for eMMC,

do not connect |

||

| J1.130 | PC6_OPT | CPU.PC6 | D10 | VDD | I/O | Pin AF0 | HDP1 | |

| Pin AF2 | TIM3_CH1 | |||||||

| Pin AF3 | TIM8_CH1 | |||||||

| Pin AF4 | DFSDM1_CKIN3 | |||||||

| Pin AF5 | I2S2_MCK | |||||||

| Pin AF7 | USART6_TX | |||||||

| Pin AF8 | SDMMC1_D0DIR | |||||||

| Pin AF9 | SDMMC2_D0DIR | |||||||

| Pin AF10 | SDMMC2_D6 | |||||||

| Pin AF11 | DSI_TE | |||||||

| Pin AF12 | SDMMC1_D6 | |||||||

| Pin AF13 | DCMI_D0 | |||||||

| Pin AF14 | LCD_HSYNC | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.132 | PG7 | CPU.PG7 | W10 | VDD | I/O | Pin AF0 | TRACED5 | |

| Pin AF6 | SAI1_MCLK_A | |||||||

| Pin AF7 | USART6_CK | |||||||

| Pin AF8 | UART8_RTS/UART8_DE | |||||||

| Pin AF9 | QUADSPI_CLK | |||||||

| Pin AF11 | QUADSPI_BK2_IO3 | |||||||

| Pin AF13 | DCMI_D13 | |||||||

| Pin AF14 | LCD_CLK | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.134 | PG10 | CPU.PG10 | V7 | VDD | I/O | Pin AF0 | TRACED10 | |

| Pin AF8 | UART8_CTS | |||||||

| Pin AF9 | LCD_G3 | |||||||

| Pin AF10 | SAI2_SD_B | |||||||

| Pin AF11 | QUADSPI_BK2_IO2 | |||||||

| Pin AF12 | FMC_NE3 | |||||||

| Pin AF13 | DCMI_D2 | |||||||

| Pin AF14 | LCD_B2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.136 | PD10 | CPU.PD10 | C5 | VDD | I/O | Pin AF0 | RTC_REFIN | |

| Pin AF1 | TIM16_BKIN | |||||||

| Pin AF3 | DFSDM1_CKOUT | |||||||

| Pin AF4 | I2C5_SMBA | |||||||

| Pin AF5 | SPI3_MISO/I2S3_SDI | |||||||

| Pin AF6 | SAI3_FS_B | |||||||

| Pin AF7 | USART3_CK | |||||||

| Pin AF12 | FMC_AD15/FMC_D15 | |||||||

| Pin AF14 | LCD_B3 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.138 | PE12 | CPU.PE12 | D2 | VDD | I/O | Pin AF1 | TIM1_CH3N | |

| Pin AF3 | DFSDM1_DATIN5 | |||||||

| Pin AF5 | SPI4_SCK | |||||||

| Pin AF8 | SDMMC1_D0DIR | |||||||

| Pin AF10 | SAI2_SCK_B | |||||||

| Pin AF12 | FMC_AD9/FMC_D9 | |||||||

| Pin AF14 | LCD_B4 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.140 | PA3 | CPU.PA3 | P3 | VDD | I/O | Pin AF1 | TIM2_CH4 | |

| Pin AF2 | TIM5_CH4 | |||||||

| Pin AF3 | LPTIM5_OUT | |||||||

| Pin AF4 | TIM15_CH2 | |||||||

| Pin AF7 | USART2_RX | |||||||

| Pin AF9 | LCD_B2 | |||||||

| Pin AF11 | ETH1_GMII_COL/

ETH1_MII_COL | |||||||

| Pin AF14 | LCD_B5 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP15

PVD_IN | |||||||

| J1.142 | PB8 | CPU.PB8 | W6 | VDD | I/O | Pin AF0 | HDP6 | |

| Pin AF1 | TIM16_CH1 | |||||||

| Pin AF2 | TIM4_CH3 | |||||||

| Pin AF3 | DFSDM1_CKIN7 | |||||||

| Pin AF4 | I2C1_SCL | |||||||

| Pin AF5 | SDMMC1_CKIN | |||||||

| Pin AF6 | I2C4_SCL | |||||||

| Pin AF7 | SDMMC2_CKIN | |||||||

| Pin AF8 | UART4_RX | |||||||

| Pin AF9 | FDCAN1_RX | |||||||

| Pin AF10 | SDMMC2_D4 | |||||||

| Pin AF11 | ETH1_GMII_TXD3/

ETH1_MII_TXD3/ ETH1_RGMII_TXD3 | |||||||

| Pin AF12 | SDMMC1_D4 | |||||||

| Pin AF13 | DCMI_D6 | |||||||

| Pin AF14 | LCD_B6 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.144 | PB9 | CPU.PB9 | D9 | VDD | I/O | Pin AF0 | HDP7 | |

| Pin AF1 | TIM17_CH1 | |||||||

| Pin AF2 | TIM4_CH4 | |||||||

| Pin AF3 | DFSDM1_DATIN7 | |||||||

| Pin AF4 | I2C1_SDA | |||||||

| Pin AF5 | SPI2_NSS/I2S2_WS | |||||||

| Pin AF6 | I2C4_SDA | |||||||

| Pin AF7 | SDMMC2_CDIR | |||||||

| Pin AF8 | UART4_TX | |||||||

| Pin AF9 | FDCAN1_TX | |||||||

| Pin AF10 | SDMMC2_D5 | |||||||

| Pin AF11 | SDMMC1_CDIR | |||||||

| Pin AF12 | SDMMC1_D5 | |||||||

| Pin AF13 | DCMI_D7 | |||||||

| Pin AF14 | LCD_B7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.146 | DGND | DGND | - | - | G | |||

| J1.148 | PA6 | CPU.PA6 | T5 | VDD | I/O | Pin AF1 | TIM1_BKIN | |

| Pin AF2 | TIM3_CH1 | |||||||

| Pin AF3 | TIM8_BKIN | |||||||

| Pin AF4 | SAI4_CK2 | |||||||

| Pin AF5 | SPI1_MISO/I2S1_SDI | |||||||

| Pin AF8 | SPI6_MISO | |||||||

| Pin AF9 | TIM13_CH1 | |||||||

| Pin AF11 | MDIOS_MDC | |||||||

| Pin AF12 | SAI4_SCK_A | |||||||

| Pin AF13 | DCMI_PIXCLK | |||||||

| Pin AF14 | LCD_G2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP3

ADC2_INP3 | |||||||

| J1.150 | PE11 | CPU.PE11 | C1 | VDD | I/O | Pin AF1 | TIM1_CH2 | |

| Pin AF3 | DFSDM1_CKIN4 | |||||||

| Pin AF5 | SPI4_NSS | |||||||

| Pin AF7 | USART6_CK | |||||||

| Pin AF10 | SAI2_SD_B | |||||||

| Pin AF12 | FMC_AD8/FMC_D8 | |||||||

| Pin AF13 | DCMI_D4 | |||||||

| Pin AF14 | LCD_G3 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.152 | PB10 | CPU.PB10 | W5 | VDD | I/O | Pin AF1 | TIM2_CH3 | |

| Pin AF3 | LPTIM2_IN1 | |||||||

| Pin AF4 | I2C2_SCL | |||||||

| Pin AF5 | SPI2_SCK/I2S2_CK | |||||||

| Pin AF6 | DFSDM1_DATIN7 | |||||||

| Pin AF7 | USART3_TX | |||||||

| Pin AF9 | QUADSPI_BK1_NCS | |||||||

| Pin AF11 | ETH1_GMII_RX_ER/

ETH1_MII_RX_ER | |||||||

| Pin AF14 | LCD_G4 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.154 | PF11 | CPU.PF11 | U5 | VDD | I/O | Pin AF5 | SPI5_MOS | |

| Pin AF10 | SAI2_SD_B | |||||||

| Pin AF13 | DCMI_D12 | |||||||

| Pin AF14 | LCD_G5 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP2 | |||||||

| J1.156 | PC7 | CPU.PC7 | A9 | VDD | I/O | Pin AF0 | HDP4 | |

| Pin AF2 | TIM3_CH2 | |||||||

| Pin AF3 | TIM8_CH2 | |||||||

| Pin AF4 | DFSDM1_DATIN3 | |||||||

| Pin AF6 | I2S3_MCK | |||||||

| Pin AF7 | USART6_RX | |||||||

| Pin AF8 | SDMMC1_D123DIR | |||||||

| Pin AF9 | SDMMC2_D123DIR | |||||||

| Pin AF10 | SDMMC2_D7 | |||||||

| Pin AF12 | SDMMC1_D7 | |||||||

| Pin AF13 | DCMI_D1 | |||||||

| Pin AF14 | LCD_G6 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.158

(eMMC 8-bit on board) |

PD3_OPT | CPU.PD3 | C6 | VDD | I/O | internally used for eMMC,

do not connect |

||

| J1.158 | PD3_OPT | CPU.PD3 | C6 | VDD | I/O | Pin AF0 | HDP5 | |

| Pin AF3 | DFSDM1_CKOUT | |||||||

| Pin AF5 | SPI2_SCK/I2S2_CK | |||||||

| Pin AF6 | DFSDM1_DATIN0 | |||||||

| Pin AF7 | USART2_CTS/USART2_NSS | |||||||

| Pin AF8 | SDMMC1_D123DIR | |||||||

| Pin AF9 | SDMMC2_D7 | |||||||

| Pin AF10 | SDMMC2_D123DIR | |||||||

| Pin AF11 | SDMMC1_D7 | |||||||

| Pin AF12 | FMC_CLK | |||||||

| Pin AF13 | DCMI_D5 | |||||||

| Pin AF14 | LCD_G7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.160 | PC10 | CPU.PC10 | D11 | VDD | I/O | Pin AF0 | TRACED2 | |

| Pin AF3 | DFSDM1_CKIN5 | |||||||

| Pin AF6 | SPI3_SCK/I2S3_CK | |||||||

| Pin AF7 | USART3_TX | |||||||

| Pin AF8 | UART4_TX | |||||||

| Pin AF9 | QUADSPI_BK1_IO1 | |||||||

| Pin AF10 | SAI4_MCLK_B | |||||||

| Pin AF12 | SDMMC1_D2 | |||||||

| Pin AF13 | DCMI_D8 | |||||||

| Pin AF14 | LCD_R2 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.162 | PB0 | CPU.PB0 | W3 | VDD | I/O | Pin AF1 | TIM1_CH2N | |

| Pin AF2 | TIM3_CH3 | |||||||

| Pin AF3 | TIM8_CH2N | |||||||

| Pin AF6 | DFSDM1_CKOUT | |||||||

| Pin AF8 | UART4_CTS | |||||||

| Pin AF9 | LCD_R3 | |||||||

| Pin AF11 | ETH1_GMII_RXD2/

ETH1_MII_RXD2/ ETH1_RGMII_RXD2 | |||||||

| Pin AF12 | MDIOS_MDIO | |||||||

| Pin AF14 | LCD_G1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP9

ADC1_INN5 ADC2_INP9 ADC2_INN5 | |||||||

| J1.164 | DGND | DGND | - | - | G | |||

| J1.166 | PA5 | CPU.PA5 | P4 | VDD | I/O | Pin AF1 | TIM2_CH1/TIM2_ETR | |

| Pin AF3 | TIM8_CH1N | |||||||

| Pin AF4 | SAI4_CK1 | |||||||

| Pin AF5 | SPI1_SCK/I2S1_CK | |||||||

| Pin AF8 | SPI6_SCK | |||||||

| Pin AF12 | SAI4_MCLK_A | |||||||

| Pin AF14 | LCD_R4 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP19

ADC1_INN18 ADC2_INP19 ADC2_INN18 DAC_OUT2 | |||||||

| J1.168 | PC0 | CPU.PC0 | T7 | VDD | I/O | Pin AF3 | DFSDM1_CKIN0 | |

| Pin AF4 | LPTIM2_IN2 | |||||||

| Pin AF6 | DFSDM1_DATIN4 | |||||||

| Pin AF8 | SAI2_FS_B | |||||||

| Pin AF10 | QUADSPI_BK2_NCS | |||||||

| Pin AF14 | LCD_R5 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP10

ADC2_INP10 | |||||||

| J1.170 | PB1 | CPU.PB1 | V3 | VDD | I/O | Pin AF1 | TIM1_CH3N | |

| Pin AF2 | TIM3_CH4 | |||||||

| Pin AF3 | TIM8_CH3N | |||||||

| Pin AF6 | DFSDM1_DATIN1 | |||||||

| Pin AF9 | LCD_R6 | |||||||

| Pin AF11 | ETH1_GMII_RXD3/

ETH1_MII_RXD3/ ETH1_RGMII_RXD3 | |||||||

| Pin AF12 | MDIOS_MDC | |||||||

| Pin AF14 | LCD_G0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

ADC1_INP5

ADC2_INP5 | |||||||

| J1.172 | PE15 | CPU.PE15 | E1 | VDD | I/O | Pin AF0 | HDP3 | |

| Pin AF1 | TIM1_BKIN | |||||||

| Pin AF4 | TIM15_BKIN | |||||||

| Pin AF7 | USART2_CTS/USART2_NSS | |||||||

| Pin AF8 | UART8_CTS | |||||||

| Pin AF10 | FMC_NCE2 | |||||||

| Pin AF12 | FMC_AD12/FMC_D12 | |||||||

| Pin AF14 | LCD_R7 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.174

(eMMC 8-bit on board) |

PE4_OPT | CPU.PE4 | B11 | VDD | I/O | internally used for eMMC,

do not connect |

||

| J1.174 | PE4_OPT | CPU.PE4 | B11 | VDD | I/O | Pin AF0 | TRACED1 | |

| Pin AF2 | SAI1_D2 | |||||||

| Pin AF3 | DFSDM1_DATIN3 | |||||||

| Pin AF4 | TIM15_CH1N | |||||||

| Pin AF5 | SPI4_NSS | |||||||

| Pin AF6 | SAI1_FS_A | |||||||

| Pin AF7 | SDMMC2_CKIN | |||||||

| Pin AF8 | SDMMC1_CKIN | |||||||

| Pin AF9 | SDMMC2_D4 | |||||||

| Pin AF11 | SDMMC1_D4 | |||||||

| Pin AF12 | FMC_A20 | |||||||

| Pin AF13 | DCMI_D4 | |||||||

| Pin AF14 | LCD_B0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.176 | PA10 | CPU.PA10 | T16 | VDD | I/O | Pin AF1 | TIM1_CH3 | |

| Pin AF5 | SPI3_NSS/I2S3_WS | |||||||

| Pin AF7 | USART1_RX | |||||||

| Pin AF11 | MDIOS_MDIO | |||||||

| Pin AF12 | SAI4_FS_B | |||||||

| Pin AF13 | DCMI_D1 | |||||||

| Pin AF14 | LCD_B1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| Additional

functions |

OTG_FS_ID

OTG_HS_ID | |||||||

| J1.178 | PE5 | CPU.PE5 | B7 | VDD | I/O | Pin AF0 | TRACED3 | |

| Pin AF2 | SAI1_CK2 | |||||||

| Pin AF3 | DFSDM1_CKIN3 | |||||||

| Pin AF4 | TIM15_CH1 | |||||||

| Pin AF5 | SPI4_MISO | |||||||

| Pin AF6 | SAI1_SCK_A | |||||||

| Pin AF7 | SDMMC2_D0DIR | |||||||

| Pin AF8 | SDMMC1_D0DIR | |||||||

| Pin AF9 | SDMMC2_D6 | |||||||

| Pin AF11 | SDMMC1_D6 | |||||||

| Pin AF12 | FMC_A21 | |||||||

| Pin AF13 | DCMI_D6 | |||||||

| Pin AF14 | LCD_G0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.180 | PE6_OPT | CPU.PE6 | B3 | VDD | I/O | for SDMMC1_D2 function

use pin J1.79 (SDMMC lenght match) |

Pin AF0 | TRACED2 |

| Pin AF1 | TIM1_BKIN2 | |||||||

| Pin AF2 | SAI1_D1 | |||||||

| Pin AF4 | TIM15_CH2 | |||||||

| Pin AF5 | SPI4_MOSI | |||||||

| Pin AF6 | SAI1_SD_A | |||||||

| Pin AF7 | SDMMC2_D0 | |||||||

| Pin AF10 | SAI2_MCLK_B | |||||||

| Pin AF12 | FMC_A22 | |||||||

| Pin AF13 | DCMI_D7 | |||||||

| Pin AF14 | LCD_G1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.182 | PG13 | CPU.PG13 | U2 | VDD | I/O | Pin AF0 | TRACED0 | |

| Pin AF1 | LPTIM1_OUT | |||||||

| Pin AF2 | SAI1_CK2 | |||||||

| Pin AF4 | SAI4_CK1 | |||||||

| Pin AF5 | SPI6_SCK | |||||||

| Pin AF6 | SAI1_SCK_A | |||||||

| Pin AF7 | USART6_CTS/USART6_NSS | |||||||

| Pin AF10 | SAI4_MCLK_A | |||||||

| Pin AF11 | ETH1_GMII_TXD0/

ETH1_MII_TXD0/ ETH1_RGMII_TXD0/ ETH1_RMII_TXD0 | |||||||

| Pin AF12 | FMC_A24 | |||||||

| Pin AF14 | LCD_R0 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.184

(eMMC 8-bit on board) |

PA15_OPT | CPU.PA15 | C7 | VDD | I/O | internally used for eMMC,

do not connect |

||

| J1.184 | PA15_OPT | CPU.PA15 | C7 | VDD | I/O | Pin AF0 | DBTRGI | |

| Pin AF1 | TIM2_CH1/TIM2_ETR | |||||||

| Pin AF2 | SAI4_D2 | |||||||

| Pin AF3 | SDMMC1_CDIR | |||||||

| Pin AF4 | CEC | |||||||

| Pin AF5 | SPI1_NSS/I2S1_WS | |||||||

| Pin AF6 | SPI3_NSS/I2S3_WS | |||||||

| Pin AF7 | SPI6_NSS | |||||||

| Pin AF8 | UART4_RTS/UART4_DE | |||||||

| Pin AF9 | SDMMC2_D5 | |||||||

| Pin AF10 | SDMMC2_CDIR | |||||||

| Pin AF11 | SDMMC1_D5 | |||||||

| Pin AF12 | SAI4_FS_A | |||||||

| Pin AF13 | UART7_TX | |||||||

| Pin AF14 | LCD_R1 | |||||||

| Pin AF15 | EVENTOUT | |||||||

| J1.186 | VBUS_OTG_IN | CPU.OTG_VBUS | U15 | VBUS_OTG_IN | S | |||

| J1.188 | VBUS_SW | PMIC.SWOUT | 38 | VBUS_SW | S | |||

| J1.190 | DGND | DGND | - | - | G | |||

| J1.192 | - | NC | - | - | - | |||

| J1.194 | - | NC | - | - | - | |||

| J1.196 | USB_DM2 | CPU.USB_DM2 | V13 | - | D | |||

| J1.198 | USB_DP2 | CPU.USB_DP2 | W13 | - | D | |||

| J1.200 | USB_DP1 | CPU.USB_DP1 | V14 | - | D | |||

| J1.202 | USB_DM1 | CPU.USB_DM1 | W14 | - | D | |||

| J1.204 | DGND | DGND | - | - | G | |||

Power and reset[edit | edit source]

Power Supply Unit (PSU) and recommended power-up sequence[edit | edit source]

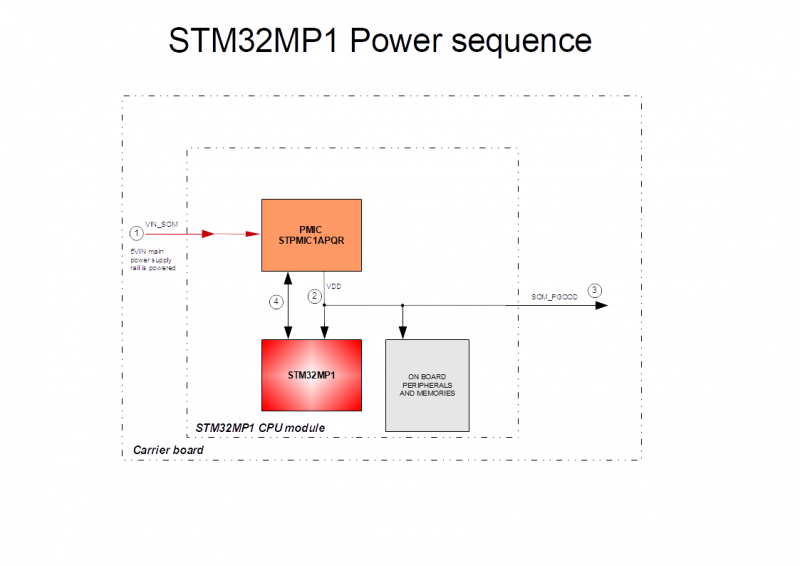

Implementing correct power-up sequence for STM32MP1 processors is not a trivial task because several power rails are involved.

ETRA SOM includes a PMIC that manage all the power on and poweroff timings to ensure the correct sequence

The following picture shows a simplified block diagram of PSU circuitry:

The PMIC:

- generates the proper power-up sequence required by the SOC processor and surrounding memories and peripherals

- synchronizes the powering up of carrier board in order to prevent back power

- provides some spare regulated voltages that can be used to power carrier board devices

Power-up sequence[edit | edit source]

The typical power-up sequence is the following:

- VIN_SOM main power supply rail is powered

- PMIC initiates the powerup sequence needed by STM32MP1 SoC

- VDD rail is powered and the SOM_PGOOD signal is asserted

- PMIC deassert processor reset and check it's status

Note on SOM_PGOOD usage[edit | edit source]

SOM_PGOOD is generally used on carrier board to drive loads such as DC/DC enable inputs or switch on/off control signals.

Depending on the kind of such loads, SOM_PGOOD might not be able to drive them properly. On ETRA SOM this signal is driven by the VDD rail so, if many loads has to be driven, connect them to the VDD output pins through a resistor.

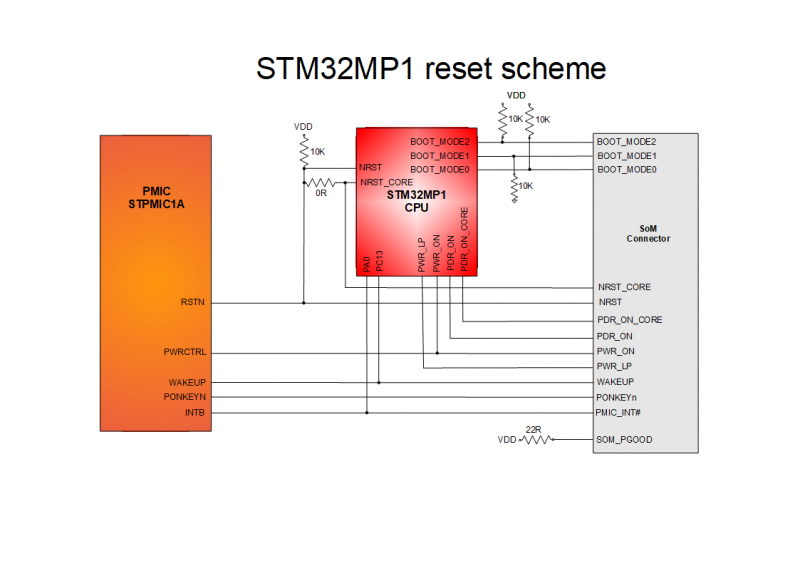

Reset scheme and control signals[edit | edit source]

The following picture shows the simplified block diagram of reset scheme and voltage monitoring.

VDD[edit | edit source]

Some signals that are related to reset circuitry are pulled-up to VDD rail. This voltage is generated by the PMIC and act as power good to switch on/off the all the peripheral that could back power the CPU.

NRST[edit | edit source]

Open drain rest signal, tie to DGND to reset the system.

It is driven by:

- the PMIC to force the CPU in reset state

- the CPU over a soft reset to restart the application

This signal is also used to reset the following on board peripherals:

- SPI NOR

- eMMC

SOM_PGOOD[edit | edit source]

This is a convencional signal to drive DC/DC enable inputs or switch on/off control signals. It is connected to the VDD through a 22Ohm resistor.

PONKEYn[edit | edit source]

User power on key (active low with internal pull-up), used to wake up the sysytem from power down.

NRST_CORE[edit | edit source]

Reset signal for the core, to be used if the VDD_CORE is not disabled during the reset. Internally tied to NRST signal.

PWR_ON[edit | edit source]

Power on CPU output signal, The state of this signal depends on power state of the processor.

PDR_ON[edit | edit source]

Input pin that disables the VDD internal voltage monitor. When this signal is set to logic 1 the processor does not issue a reset cycle when the VDD goes below the VVD_OK threshold.

Driven by default by PMIC, internally used for deep sleep modes.

PDR_ON_CORE[edit | edit source]

Input pin that disables the VDD_CORE internal voltage monitor. When this signal is set to logic 1 the processor does not issue a core reset cycle when the VDD_CORE goes below the VVD_OK threshold.

Driven by default by PMIC, internally used for deep sleep modes.

PWR_LP[edit | edit source]

CPU low power mode output, internally used by the PMIC to check the CPU low power state.

WAKEUP[edit | edit source]

PMIC power on signal from CPU, used in low power mode by the CPU internal RTC to restart the PMIC.

System boot[edit | edit source]

The boot process begins at Power On Reset (POR) where the hardware reset logic forces the ARM core to begin execution starting from the on-chip boot ROM. The boot ROM:

- determines whether the boot is secure or non-secure

- performs some initialization of the system and clean-ups

- reads the OTP settings

- reads the mode pins to determine the primary boot device

- once it is satisfied, it executes the boot code

Boot options[edit | edit source]

The default primary boot device is internally set by pull-up or pull-down resistors according to the Boot Mode fileld of the ordering code.

The BOOT_MODEx signals are also present on the SoM connector to override the primary boot device.

The following table shows all the available options:

| BOOT_MODE2 | BOOT_MODE1 | BOOT_MODE0 | PRIMARY BOOT DEVICE |

| 0 | 0 | 0 | UART and USB |

| 0 | 0 | 1 | Serial NOR on QUADSPI |

| 0 | 1 | 0 | eMMC on SDMMC2 |

| 0 | 1 | 1 | SLC NAND on FMC |

| 1 | 0 | 0 | no boot (for debug access) |

| 1 | 0 | 1 | SD card on SDMMC1 |

| 1 | 1 | 0 | UART and USB |

| 1 | 1 | 1 | Serial NAND on QUADSPI |

Use 1k resistors either to VDD or DGND to drive externally the BOOT_MODEx signals.

On board OTP[edit | edit source]

The reading of BOOT_MODEx pins can be disabled by OTP configuration, in this case the OTP settings are used by the ROM code to determine the boot device.

Boot sources can be individually disabled by the OTP settings.

On board JTAG connector[edit | edit source]

JTAG signals are routed to the primary ETRA connector J1, see the Connectors and Pinout Table

Peripherals[edit | edit source]

Peripheral Audio[edit | edit source]

The Audio interface available on ETRA SOM is based on STM32MP1 SoC which provides the following audio subsystems:

- Synchronous Audio Interface (SAI)

- 4x I2S/SAI (16+ channels, each up to 32-bits @192 kHz)

- Two independent audio subblocks which can be transmitters or receivers with their respective 8-word integrated FIFOs

- Sony/Philips Digital Interface (SPDIF)

- S/PDIF Tx/Rx

Description[edit | edit source]

The I2S (Inter IC Sound) module provides a synchronous audio interface (SAI) that supports full- duplex serial interfaces with frame synchronization such as I2S, LSB or MSB-justified, AC'97, TDM, and PCM/DSP interfaces.

It supports the following standards and features:

- Two independent audio subblocks

- Synchronous or asynchronous mode between the audio subblocks

- Possible synchronization between multiple SAIs

- Master or slave configuration independent for both audio subblocks

- 2-channel DMA interface

The Sony/Philips Digital Interface (SPDIF) audio block is a stereo transceiver that allows the processor to receive and transmit digital audio.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral CAN[edit | edit source]

The Controller Area Network (CAN) is a robust standard BUS used in automotive applications. It allows multiple devices to transmit at the same time, the highest priority device continues the transmission while the others wait for the next available slot.

An external CAN tranciever is needed to operate.

Description[edit | edit source]

The CAN interface available on ETRA SOM is based on STM32MP1 SoC.

The CAN port supports the following standards and features:

- two Flexible Data CAN (FDCAN) modules with shared message RAM and a clock calibration unit

- compliant with ISO 11898-1: 2015 (CAN protocol specification version 2.0 part A, B) and CAN FD protocol specification version 1.0

- the first CAN module supports time triggered CAN (TTCAN), specified in ISO 11898-4

- 10 Kbyte message RAM implements filters, receive FIFOs, receive buffers, transmit event FIFOs, transmit buffers (and triggers for TTCAN)

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral Ethernet[edit | edit source]

The Ethernet peripheral enables the devices to transmit and receive data over Ethernet in compliance with the IEEE 802.3-2002 standard.

Description[edit | edit source]

The 10/100/1000-Mbit/s Ethernet interface available on ETRA SOM is based on STM32MP1 SoC.

On ETRA SOM the SoC is directly interfaced with an onboard ETH PHY chip (MICROCHIP KSZ8091RNAIA) with the following features:

- Auto-Negotiation to Automatically Select the Highest Link-Up Speed (10/100 Mbps) and Duplex (Half/Full)

- On-Chip Termination Resistors for the Differential Pairs

- HP Auto MDI/MDI-X to Reliably Detect and Correct Straight-Through and Crossover Cable Connections

- Energy Efficient Ethernet (EEE) support with Low-Power Idle (LPI) mode for 100BASE-TX and Transmit Amplitude Reduction with 10BASE-TE option

- Wake-on-LAN (WoL) Support with Either Magic Packet, Link Status Change, or Robust Custom-Packet Detection

Important note for the external magnetic connection[edit | edit source]

The Ethernet peripheral requires an external insulator magnetic on the carrier board.

The two transformer center tap pins on the PHY side should not be connected to any power supply source on the board; rather, the center tap pins should be separated from one another and connected through separate 0.1 µF common-mode capacitors to ground. Separation is required because the common-mode voltage could be different between the four differential pairs, depending on the connected speed mode.

See section 11 (Magnetic connection and selection) on KSZ8091RN datasheet for more details.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral HDMI-CEC[edit | edit source]

Consumer electronics control (CEC) is part of HDMI (high-definition multimedia interface) standard as appendix supplement 1. It contains a protocol that provides high-level control functions between various audiovisual products.

Description[edit | edit source]

The HDMI-CEC interface available on ETRA SOM is based on STM32MP1 SoC.

The HDMI-CEC port supports the following standards and features:

- complies with HDMI-CEC v1.4 specification

- independent 32 kHz CEC kernel

- works in Stop mode for ultra-low-power applications

- Arbitration lost detection with automatic trasmission retry

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral LCD[edit | edit source]

The LCD-TFT (liquid crystal display - thin film transistor) display controller provides a parallel digital RGB (red, green, blue) and control signals for horizontal, vertical synchronization, pixel clock and data enable as output to interface directly to a variety of LCD and TFT panels.

Description[edit | edit source]

The LCD-TFT display controller (LTDC) interface available on ETRA SOM is based on STM32MP1 SoC.

The LCD-TFT port supports the following standards and features:

- up to 24-bit RGB parallel pixel output; 8 bits-per-pixel (RGB888)

- 2 display layers with dedicated FIFOs (64x64-bit)

- color look-up table up to 256 color (256x24-bit) per layer

- flexible blending between two layers using alpha value

- programmable window position and size

- up to 4 programmable interrupt events

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral DSI[edit | edit source]

Display Serial Interface (DSI in short) is part of a group of communication protocols defined by the MIPI® Alliance.

Description[edit | edit source]

The DSI interface available on ETRA SOM is based on STM32MP1 SoC.

The DSI port supports the following standards and features:

- interface with MIPI® D-PHY

- supports all commands defined in the MIPI® Alliance specification for DCS

- supports up to two D-PHY data lanes

- LTDC interface color coding mappings into 24-bit interface:

- 16-bit RGB, configurations 1, 2, and 3

- 18-bit RGB, configurations 1 and 2

- 24-bit RGB

- video mode pattern generator

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral DCMI[edit | edit source]

The Digital CaMera Interface (DCMI) is a synchronous parallel interface able to receive a high-speed data flow from an external CMOS camera module.

Description[edit | edit source]

The DCMI interface available on ETRA SOM is based on STM32MP1 SoC.

The DCMI port supports the following standards and features:

- 8-, 10-, 12- or 14-bit parallel interface

- embedded/external line and frame synchronization

- note that the VSYNC external signal is not available if the NAND flash is populated on board of the SoM

- continuous or snapshot mode

- crop feature

- supports the following data formats:

- 8/10/12/14-bit progressive video: either monochrome or raw bayer

- YCbCr 4:2:2 progressive video

- RGB 565 progressive video

- compressed data: JPEG

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral SDMMC[edit | edit source]

Secure digital input/output MultiMediaCard interface (SDMMC) provides an interface between the AHB bus and SD memory cards, SDIO cards and eMMC devices.

ETRA SOM provides up to two SDMMC interfaces: the second interface (SDMMC2) is internally used if the eMMC flash is populated in the SOM.

Description[edit | edit source]

The SDMMC interface available on ETRA SOM is based on STM32MP1 SoC.

The SDMMC port supports the following standards and features:

- compliance with Embedded MultiMediaCard System Specification Version 5.1

- card support for three different databus modes: 1-bit (default), 4-bit and 8-bit (HS400 is not supported)

- full compatibility with previous versions of MultiMediaCards (backward compatibility)

- full compliance with SD memory card specifications version 6.0 (SPI mode and UHS-II mode not supported)

- full compliance with SDIO card specification version 4.0 (SPI mode and UHS-II mode not supported)

- data transfer up to 208 Mbyte/s for the 8-bit mode

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral SPI[edit | edit source]

The Serial Peripheral Interface (SPI) is a full-duplex, synchronous, four-wire serial communication block.

Description[edit | edit source]

The SPI interface available on ETRA SOM is based on STM32MP1 SoC.

The SPI port supports the following standards and features:

- full-duplex synchronous transfers on three lines

- half-duplex synchronous transfer on two lines (with bidirectional data line)

- simplex synchronous transfers on two lines (with unidirectional data line)

- 4-bit to 32-bit data size selection

- multi master or multi slave mode capability

- hardware or software management of SS for both master and slave

- configurable SS signal polarity and timing, MISO x MOSI swap capability

- two 16x or 8x 8-bit embedded Rx and TxFIFOs with DMA capability

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral QUADSPI[edit | edit source]

The QUADSPI is a dedicated communication interface for single, dual or quad SPI Flash memories.

Description[edit | edit source]

The QUADSPI interface available on ETRA SOM is based on STM32MP1 SoC.

The QUADSPI port supports the following standards and features:

- three functional modes: indirect, status-polling, and memory-mapped

- indirect mode: all the operations are performed using the QUADSPI registers

- status polling mode: the external Flash memory status register is periodically read and an interrupt can be generated in case of flag setting

- memory-mapped mode: the external Flash memory is mapped to the device address space and is seen by the system as if it was an internal memory

- dual-flash mode, where 8 bits can be sent/received simultaneously by accessing two Flash memories in parallel

- integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses

- DMA channel for indirect mode operations

- interrupt generation on FIFO threshold, timeout, operation complete, and access error

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral I2C[edit | edit source]

I2C is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices.

This bus is suitable for applications requiring occasional communications over a short distance between many devices.

Description[edit | edit source]

The I2C interface available on ETRA SOM is based on TSM32MP1 SoC.

The I2C port supports the following standards and features:

- slave and master modes

- multimaster capability

- standard-mode (up to 100 kHz), fast-mode (up to 400 kHz) and fast-mode Plus (up to 1 MHz)

- 7-bit and 10-bit addressing mode

- programmable setup and hold times

- 1-byte buffer with DMA capability

- programmable analog and digital noise filters

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral USART[edit | edit source]

UART (USART on STM32MP1) provides serial communication capability with external devices and support NRZ encoding format, RS485 compatible 9 bit data format and IrDA-compatible infrared slow data rate (SIR) format.

Description[edit | edit source]

The USART interface available on ETRA SOM is based on STM32MP1 SoC.

The USART port supports the following standards and features:

- full-duplex asynchronous communication

- baud rate generator systems

- two internal FIFOs for transmit and receive data

- auto baud rate detection

- programmable data word length (7, 8 or 9 bits)

- programmable data order with MSB-first or LSB-first shifting

- configurable stop bits (1 or 2 stop bits)

- synchronous master/slave mode and clock output/input for synchronous communications

- single-wire Half-duplex communications

- continuous communications using DMA

- swappable Tx/Rx pin configuration

- hardware flow control for modem and RS-485 transceiver

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral ADC[edit | edit source]

Description[edit | edit source]

The Analog-to-digital converter (ADC) interface available on ETRA SOM is based on STM32MP1 SoC.

The ADC port supports the following standards and features:

- up to 2x ADCs which can operate in dual mode

- 16, 14, 12, 10 or 8-bit configurable resolution

- ADC conversion time is independent from the AHB bus clock frequency

- can manage Single-ended or differential inputs

- self-calibration (both offset and linearity)

- up to 6 fast channels

- up to 14 slow channels

- speed adaptive low-power mode to reduce ADC consumption when operating at low frequency

- 3 analog watchdogs per ADC

- ADC input range from DGND to VDD

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral DAC[edit | edit source]

Description[edit | edit source]

The DAC interface available on ETRA SOM is based on STM32MP1 SoC.

The DAC port supports the following standards and features:

- one DAC interface, maximum two output channels

- synchronized update capability

- noise-wave and Triangular-wave generation

- dual DAC channel for independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- DAC output channel buffered/unbuffered modes

Pin mapping[edit | edit source]

DAC I/O connections:

- DAC1_OUT1 on PA4

- DAC1_OUT2 on PA5

The Pin mapping is described in the Pinout table section

Peripheral USB Host[edit | edit source]

USB host controller supporting the standard registers used for full-speed (OHCI controller) and high-speed (EHCI controller).

Description[edit | edit source]

The USB Host interface available on ETRA SOM is based on STM32MP1 SoC.

The USB Host port supports the following standards and features:

- two physical ports supported using an on-chip 2-port high-speed PHY

- the second port is shared with USB OTG peripheral

- supports OHCI model for full- and low-speed operation

- supports EHCI model for high-speed operation

- LPM (link power management) support

- DMA engine with local 512 Byte packet buffer

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral USB OTG[edit | edit source]

The USB OTG is a dual-role device (DRD) controller that supports both device and host functions and is fully compliant with the On-The-Go Supplement to the USB 2.0 Specification. It can also be configured as a host-only or device-only controller, fully compliant with the USB 2.0 Specification.

Description[edit | edit source]

The USB OTG interface available on ETRA SOM is based on STM32MP1 SoC.

The USB OTG port supports the following standards and features:

- it is USB-IF certified to the Universal Serial Bus Specification Rev 2.0

- integrated support for A-B device identification (ID line)

- integrated support for host Negotiation protocol (HNP) and session request protocol (SRP)

- it allows host to turn VBUS off to conserve battery power in OTG applications

- it supports OTG monitoring of VBUS levels with internal comparators

- it supports dynamic host-peripheral switch of role

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral GPIOs[edit | edit source]

The general-purpose input/output (GPIO) peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs.

Description[edit | edit source]

The primary GPIOs interface available on ETRA SOM is based on STM32MP1 SoC.

The STM32MP1 GPIO ports supports the following standards and features:

- output states: push-pull or open drain + pull-up/down

- speed selection for each I/O