ZERO SOM/ZERO Hardware/pdf

General Information[edit | edit source]

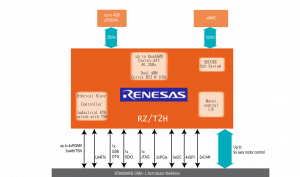

ZERO Block Diagram[edit | edit source]

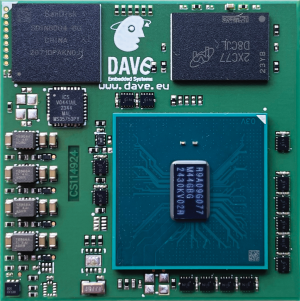

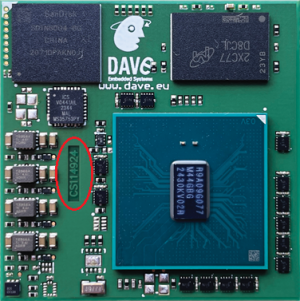

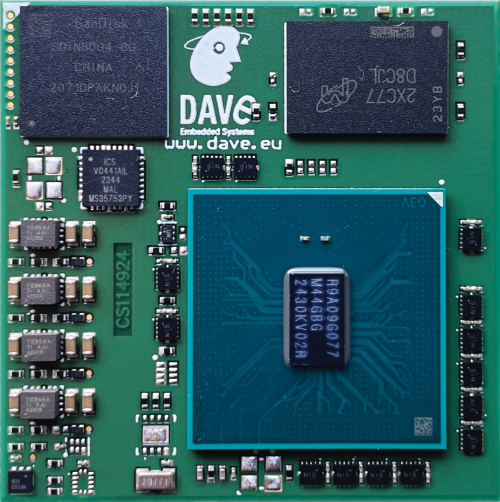

ZERO TOP View[edit | edit source]

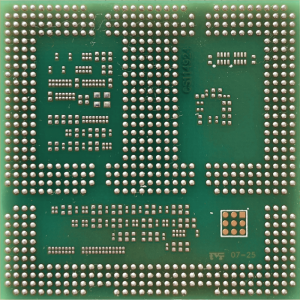

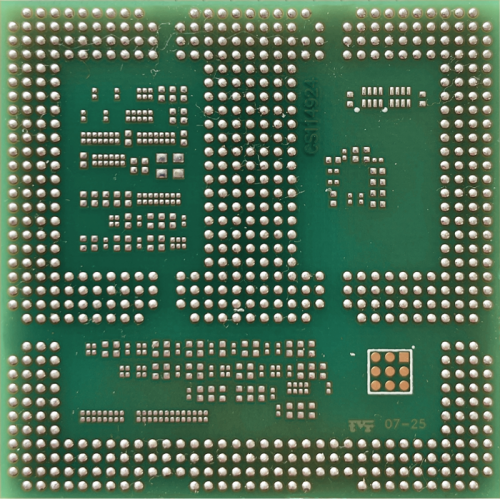

ZERO BOTTOM View[edit | edit source]

Processor and memory subsystem[edit | edit source]

The heart of ZERO module is composed of the following components:

- RZ/T2H SoC application processor

- Power supply unit

- LPDDR4 memory bank

- eMMC flash memory

- OSM L 45x45mm form factor

This chapter briefly describes the main ZERO components.

Processor Info[edit | edit source]

| Processor | RZ/T2H | |

| # Cores | 1x/2x/4x Arm® Cortex®-A55

2x Arm® Cortex®-R52 | |

| Clock | 1.2 GHz (Industrial)

500/1000MHz | |

| OnChip SRAM | 2 MB | |

| L3

Cache |

1024 KB | |

| LPDDR4 | 32 bit @ 1600 MHz

(LPDDR4-3200) | |

| Display Controller | RGB 888

up to 1280x800@60 fps | |

| Ethernet | 1 channel / 3 ports EtherCAT slave Controller

3 port PHY Ethernet switch 10/100/1000 Mbps 1 port / 3 units Ethernet MAC 10/100/1000 Mbps | |

| PCIe | Gen3 2-lanes | |

| USB | 1x USB 2.0 Host/OTG | |

| Multi function Timer Unit | 8x 16 bits channel

1x 23 bits channel | |

| General PWM Timer | 56x 32 bits channels

(45 ch 9 axes motor control) | |

| AD converter | 3x 12 bits | |

| Serial interface | 3x I2C

4x SPI 2x CAN 6x SCI (UART) | |

| Watchdog Timer | 6x 14 bits channels | |

RAM memory bank[edit | edit source]

LPDDR4 SDRAM memory bank is composed of 1x 32-bit width chip. The following table reports the SDRAM specifications:

| CPU connection | SDRAM Subsystem Mermoy Controller (DDRSS) |

| Size max | 4 GB |

| Width | 32 bit |

| Speed | 1600 MHz |

eMMC flash bank[edit | edit source]

The onboard main storage memory eMMC is connected to the SDHI (SD Host Interface) and it can act as boot peripheral. The following table reports the eMMC flash specifications:

| CPU connection | SDI1 |

| Size min | 8 GB |

| Size max | 64 GB |

| Bootable | Yes |

Memory map[edit | edit source]

For detailed information, please refer to the RZ/T2H Hardware User’s Manual.

Power supply unit[edit | edit source]

ZERO embeds all the elements required to power the unit, therefore, power sequencing is self-contained and simplified. Nevertheless, power must be provided from the carrier board, and therefore users should be aware that the power supply range can assumes as well as all other parameters.

Hardware versioning and tracking[edit | edit source]

ZERO SOM implements well-established versioning and tracking mechanisms:

- PCB version is copper printed on PCB itself, as shown in Fig. 1

- serial number: it is printed on a white label, as shown in Fig. 2: see also Product serial number page for more details

- ConfigID: it is used by software running on the board for the identification of the product model/hardware configuration. For more details, please refer to this link

Part number composition[edit | edit source]

ZERO SOM module part number is identified by the following digit-code table:

| Part number structure | Options | Description |

|---|---|---|

| Family | DSAB | Family prefix code |

| SOC |

|

Other versions can be available, please contact technical support |

| RAM |

|

|

| Storage |

|

|

| Boot mode |

|

|

| Option |

|

|

| RFU |

|

|

| Temperature range |

|

|

| PCB revision |

|

PCB release may change for manufacturing purposes (i.e. text fixture adaptation) |

| Manufacturing option |

|

typically connected to production process and quality |

| Software Configuration | -00: standard factory u-boot pre-programmed | If customers require custom SW deployed this section should be defined and agreed. Please contact technical support |

Example[edit | edit source]

ZERO SOM code DSABA30000I1R-00

- A: R9A09G077M44GBG quad core A55 1.2GHz

- 3: 8GB LPDDR4

- 0: 8GB eMMC

- 0: boot from eMMC

- 0: no options

- 0: RFU

- I: Industrial grade: -40 to +85°C

- 1: rev. A PCB version

- R: RoHS compliant

- -00: standard factory u-boot pre-programmed

Pinout Table[edit | edit source]

Connectors[edit | edit source]

Connectors description[edit | edit source]

In the following table are described all available connectors integrated on ZERO:

| Connector Type | Notes | Carrier board counterpart |

|---|---|---|

| OSM Size-L 45x45mm |

The dedicated carrier board must present the OSM Size-L footprint for soldering the ZERO SOM according to the pinout specifications. See the images below for reference:

Pinout Table[edit | edit source]

Naming conventions[edit | edit source]

This chapter contains the description of the ZERO SoM pinout, listed following the OSM Size-L pin-out.

Each row in the pin-out tables contains the following information:

| OSM Size | Size factor |

| OSM contact | Contact name (grid position), sorted by OSM size factor |

| OSM Name | OSM standard version 1.2 contact signal name |

| SoC or other components | Internal system-on-chip or other component signal name |

| SoC Voltage domain | Signal voltage domain |

| OSM Voltage | Voltage domain defined by OSM standard |

| Level shift | Indicates if an internal level shifter is inserted between the SoC pad and the external OSM contact |

| OSM violation | Indicates if the connected signal does not comply with the OSM standard

(due to different functionality or violation of voltage domain) |

OSM Pinout[edit | edit source]

| OSM Size | OSM contact | OSM Name | SoC or other components | SOC Voltage domain | OSM Voltage | Level shift | OSM violation | |

|---|---|---|---|---|---|---|---|---|

| Size-0 | A14 | UART_A_RX | SOC.P13_4/D28/GTIOC03_3B/RXD3/SCL3/MISO3/SPI_SSL31/MCLK40/ENCIFCK13/SCKE09/HDSL10_SEL2 | VDD1833_6 | SDIO_A_IOPWR | 1.8 | 1 | |

| A15 | COM_AREA_01 | 1.8 | ||||||

| A16 | COM_AREA_02 | 1.8 | ||||||

| A17 | COM_AREA_03 | |||||||

| A18 | COM_AREA_04 | |||||||

| A19 | COM_AREA_05 | 1.8 | ||||||

| A20 | COM_AREA_06 | 1.8 | ||||||

| A21 | COM_AREA_07 | 5 | ||||||

| A22 | UART_C_RX | |||||||

| B13 | UART_A_TX | SOC.P13_5/IRQ4/D29/GTIOC06_3A/TXD3/SDA3/MOSI3/SPI_SSL32/MDAT40/ENCIFOE13/DEE09/HDSL10_MISO2 | VDD1833_6 | SDIO_A_IOPWR | 1.8 | 1 | ||

| B15 | COM_AREA_08 | 3.3 | ||||||

| B16 | COM_AREA_09 | 3.3 | ||||||

| B17 | COM_AREA_10 | 3.3 | ||||||

| B18 | COM_AREA_11 | 3.3 | ||||||

| B19 | COM_AREA_12 | 3.3 | ||||||

| B20 | COM_AREA_13 | 3.3 | ||||||

| B21 | COM_AREA_14 | 3.3 | ||||||

| B22 | Vendor Defined | BOOT_SEL2# | ||||||

| B23 | UART_C_TX | |||||||

| C13 | UART_A_RTS | SOC.P13_6/D30/GTIOC06_3B/GTIOC04_3A/SS3#/CTS3#/RTS3#/SPI_SSL23/MCLK41/ENCIFDO13/TXDE09/HDSL10_MOSI2 | VDD1833_6 | SDIO_A_IOPWR | 1.8 | 1 | ||

| C14 | UART_A_CTS | SOC.P13_7/IRQ14/D31/GTIOC06_4A/GTIOC04_3B/CTS3#/MDAT41/ENCIFDI13/RXDE09/HDSL11_LINK | VDD1833_6 | SDIO_A_IOPWR | 1.8 | 1 | ||

| C15 | COM_AREA_15 | 3.3 | ||||||

| C16 | Vendor Defined | BOOT_SEL3# | ||||||

| C17 | COM_AREA_16 | 1.8 | ||||||

| C18 | TEST_GENERIC (vendor defined) | SOC.BSCANP | 1.8 | |||||

| C19 | COM_AREA_17 | 3.3 | ||||||

| C20 | SDIO_A_IOPWR | SDIO_A_IOPWR | 1.8V or 3.3V | |||||

| C21 | COM_AREA_18 | 3.3 | ||||||

| C22 | UART_D_RX | SOC.P16_3/IRQ10/GTETRGSA/ESC_LINKACT0/RXD5/SCL5/MISO5/DUEI04/HDSL13_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| C23 | UART_D_TX | SOC.P16_4/IRQ11/GTETRGSB/ESC_LINKACT1/TXD5/SDA5/MOSI5/TST_OUT04/HDSL13_SMPL | VDD33 | 3.3 | 1.8 | 1 | ||

| D13 | UART_B_TX | SOC.P11_1/IRQ4/ESC_LEDRUN/TXD1/SDA1/MOSI1/MDAT22/DUEI15/HDSL08_MISO2 | VDD33 | 3.3 | 1.8 | 1 | ||

| D14 | UART_B_RX | SOC.P11_0/IRQ13/A5/GTIOC00_3B/ESC_RESETOUT#/RXD1/SCL1/MISO1/MCLK22/DISP_DATAG0/HDSL08_SEL2/POUTZ | VDD33 | 3.3 | 1.8 | 1 | ||

| D15 | UART_B_RTS | SOC.P11_2/IRQ5/SS1#/CTS1#/RTS1#/MCLK30/TST_OUT15/HDSL08_MOSI2 | VDD33 | 3.3 | 1.8 | 1 | ||

| D16 | UART_B_CTS | SOC.P11_3/IRQ6/CTS1#/MDAT30/SI15#/HDSL09_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| D17 | GPIO_A_0 | SOC.P05_5/XSPI0_DS/TST_OUT07/HDSL04_MOSI1 | VDD1833_4 | 1.8 | 1.8 | |||

| D18 | GND | |||||||

| D19 | GPIO_B_0 | SOC.P06_2/IRQ8/IIC_SCL0/XSPI0_IO4/DUEI09/HDSL05_LINK | VDD1833_4 | 1.8 | 1.8 | |||

| D20 | SDIO_A_WP | SDIO_A_IOPWR | ||||||

| D21 | SDIO_A_PWR_EN | SDIO_A_IOPWR | ||||||

| D22 | UART_CON_RX | SOC.P27_4/MTIOC2B/GTIOC08_3B/GTIOC02_1B/RXD0/SCL0/MISO0/CANTXDP1/SPI_MISO0/HSPI_IO2/ENCIFOE14/DEE10/HDSL04_MOSI2 | VDD33 | 3.3 | 1.8 | 1 | ||

| D23 | UART_CON_TX | SOC.P27_5/MTIOC1A/GTIOC08_4A/GTIOC02_2A/TXD0/SDA0/MOSI0/SPI_SSL00/HSPI_IO3/ENCIFDO14/TXDE10/HDSL05_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| E15 | GND | |||||||

| E16 | ETH_A_(R)(G)MII_CRS | SOC.P22_3/IRQ5/A22/GTETRGC/ETH0_CRS/SCK5/CANRXDP0/DUEI14/HDSL01_MISO1 | VDD33 | 3.3 | 1 | |||

| E17 | GPIO_A_1 | SOC.P07_3/POE11#/IIC_SCL1/XSPI0_INT0#/MCLK01/ENCIFDO04/ENCIFDO12/TXDE04/TXDE08/HDSL05_MISO2 | VDD1833_4 | 1.8 | 1.8 | |||

| E18 | PWM_0 | SOC.P00_7/IRQ5/MTCLKB/MTIOC1B/GTIOC00_3B/IIC_SDA0/USB_EXICEN/ENCIFOE00/ENCIFOE04/DEE00/DEE04/HDSL00_SEL2 | VDD33 | 3.3 | 1.8 | 1 | ||

| E19 | GPIO_B_1 | SOC.P13_3/D27/GTIOC03_3A/SCK3/SPI_SSL30/MDAT01/ENCIFDI12/ENCIFDI03/RXDE08/RXDE03/HDSL10_CLK2 | VDD1833_6 | SDIO_A_IOPWR | 1.8 | |||

| E20 | SDIO_A_CMD | SOC.P12_1/D17/MTIC5W/GTIOC05_1B/CMTW0_TOC0/CANTX1/SD0_CMD/TST_OUT01/HDSL09_CLK2 | VDD1833_6 | SDIO_A_IOPWR | SDIO_A_IOPWR | |||

| E21 | GND | |||||||

| F15 | ETH_A_(R)(G)MII_COL | SOC.P22_4/IRQ6/A21/GTETRGD/ETH0_COL/SS5#/CTS5#/RTS5#/CANTXDP0/TST_OUT14/HDSL01_MOSI1 | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| F16 | GND | |||||||

| F17 | GPIO_A_2 | SOC.P06_6/MDD/XSPI0_RESET0# | VDD1833_4 | 1.8 | 1.8 | |||

| F18 | PWM_1 | SOC.P00_3/IRQ2/D3/MTIOC4C/GTIOC00_1B/ETH3_COL/ADTRG1#/DUEI01/HDSL00_SEL1 | VDD33 | 3.3 | 1.8 | 1 | ||

| F19 | GPIO_B_2 | SOC.P06_7/IRQ12/POE4#/GTETRGD/GMAC1_MDC/IIC_SCL2/HDSL05_MISO1 | VDD1833_4 | 1.8 | 1.8 | |||

| F20 | GND | |||||||

| F21 | SDIO_A_CLK | SOC.P12_0/D16/MTIC5V/GTIOC05_1A/CMTW0_TIC0/CANRX1/SD0_CLK/DUEI01/HDSL09_MOSI1 | VDD1833_6 | SDIO_A_IOPWR | SDIO_A_IOPWR | 1 | ||

| G15 | ETH_A_(S)(R)(G)MII_TXD1 | SOC.P20_2/ETH0_TXD1 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| G16 | ETH_A_(S)(R)(G)MII_TXD3 | SOC.P20_4/ETH0_TXD3/CANTX0 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| G17 | GPIO_A_3 | SOC.P07_0/IRQ13/GMAC1_MDIO/IIC_SDA2/XSPI0_RESET1#/HDSL05_MOSI1 | 1.8 | |||||

| G18 | PWM_2 | SOC.P00_4/IRQ3/D4/MTIOC4B/GTIOC00_2A/ADTRG2#/TST_OUT01/HDSL00_MISO1 | VDD33 | 3.3 | 1.8 | 1 | ||

| G19 | GPIO_B_3 | SOC.P06_5/IRQ11/GTETRGC/IIC_SDA1/XSPI0_IO7/HDSL05_SEL1 | VDD1833_4 | 1.8 | 1.8 | |||

| G20 | SDIO_A_D0 | SOC.P12_2/D18/GTIOC05_2A/CMTW0_TIC1/CANRXDP1/SD0_DATA0/SI01#/HDSL09_SEL2 | VDD1833_6 | SDIO_A_IOPWR | SDIO_A_IOPWR | |||

| G21 | SDIO_A_D1 | SOC.P12_3/D19/GTIOC05_2B/CMTW0_TOC1/SCK2/CANTXDP1/SD0_DATA1/HDSL09_MISO2 | VDD1833_6 | SDIO_A_IOPWR | SDIO_A_IOPWR | |||

| H15 | ETH_A_(S)(R)(G)MII_TXD0 | SOC.P20_1/MDV/ETH0_TXD0 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| H16 | ETH_A_(S)(R)(G)MII_TXD2 | SOC.P20_3/ETH0_TXD2/CANRX0 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| H17 | GPIO_A_4 | SOC.P09_2/MCLK20/TST_OUT12/HDSL07_SEL1 | VDD33 | 3.3 | 1.8 | 1 | ||

| H18 | PWM_3 | SOC.P00_5/MTIOC4D/MTIOC8C/GTIOC00_2B/USB_VBUSEN/SI01#/HDSL00_MOSI1 | VDD33 | 3.3 | 1.8 | |||

| H19 | GPIO_B_4 | SOC.P06_4/IRQ10/GTETRGB/IIC_SCL1/XSPI0_IO6/SI09#/HDSL05_CLK1 | VDD1833_4 | 1.8 | 1.8 | |||

| H20 | SDIO_A_D2 | SOC.P12_4/IRQ1/D20/GTIOC05_3A/CMTW1_TIC0/RXD2/SCL2/MISO2/SD0_DATA2/MCLK02/ENCIFCK05/SCKE05/HDSL09_MOSI2 | VDD1833_6 | SDIO_A_IOPWR | SDIO_A_IOPWR | |||

| H21 | SDIO_A_D3 | SOC.P12_5/D21/GTIOC05_3B/GTIOC01_3A/CMTW1_TOC0/TXD2/SDA2/MOSI2/SD0_DATA3/MDAT02/ENCIFOE05/DEE05/HDSL10_LINK | VDD1833_6 | SDIO_A_IOPWR | SDIO_A_IOPWR | |||

| J15 | ETH_A_(R)(G)MII_TX_CLK | SOC.P20_0/ETH0_TXCLK/HDSL15_MOSI2 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| J16 | GND | |||||||

| J17 | GPIO_A_5 | SOC.P06_3/IRQ9/GTETRGA/IIC_SDA0/XSPI0_IO5/TST_OUT09/HDSL05_SMPL | 1.8 | |||||

| J18 | PWM_4 | SOC.P00_6/IRQ4/MTCLKA/MTIOC8D/GTIOC00_3A/IIC_SCL0/USB_OVRCUR/ENCIFCK00/ENCIFCK04/SCKE00/SCKE04/HDSL00_CLK2 | VDD33 | 3.3 | 1.8 | 1 | ||

| J19 | GPIO_B_5 | SOC.P05_2/IRQ4/IIC_SCL2/XSPI0_CKN/TST_OUT06/HDSL04_CLK1 | VDD1833_4 | 1.8 | 1.8 | |||

| J20 | GND | |||||||

| J21 | SDIO_A_CD# | SDIO_A_IOPWR | ||||||

| K15 | ETH_A_(S)(R)(G)MII_RXD0 | SOC.P20_7/ETH0_RXD0/SI11#/HDSL00_CLK1 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| K16 | ETH_A_(R)(G)MII_TX_EN(_ER) | SOC.P20_5/ETH0_TXEN/DUEI11/HDSL00_LINK | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| K17 | GPIO_A_6 | SOC.P01_5/MTIOC7C/MTIC5W/GTIOC01_1B/GTIOC04_1B/XSPI1_IO1/DUEI03/HDSL01_SEL1 | VDD1833_5 | 1.8 | 1.8 | |||

| K18 | PWM_5 | SOC.P11_6/GTIOC05_0A/TST_OUT00/HDSL09_SEL1 | VDD33 | 3.3 | 1.8 | 1 | ||

| K19 | GPIO_B_6 | SOC.P01_6/MTIOC7B/MTIOC0A/GTIOC01_2A/GTIOC04_2A/XSPI1_IO2/TST_OUT03/HDSL01_MISO1 | VDD1833_5 | 1.8 | 1.8 | |||

| K20 | SDIO_B_CLK | SDIO_B_IOPWR | ||||||

| K21 | SDIO_B_CMD | SDIO_B_IOPWR | ||||||

| L15 | ETH_A_(S)(R)(G)MII_RXD1 | SOC.P21_0/ETH0_RXD1/DUEI12/HDSL00_SEL1 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| L16 | ETH_A_(R)(G)MII_RX_ ER | SOC.P22_2/A23/GTETRGB/ETH0_RXER/RXD5/SCL5/MISO5/CANRX0/HDSL01_SEL1 | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| L17 | GPIO_A_7 | SOC.P09_3/MDAT20/SI12#/HDSL07_MISO1 | VDD33 | 3.3 | 1.8 | 1 | ||

| L18 | GND | |||||||

| L19 | GPIO_B_7 | SOC.P01_0/IRQ6/MTIOC3A/MTIOC1A/GTIOC00_4A/GTIOC00_2B/IIC_SCL1/XSPI1_CKP/ENCIFDO00/ENCIFDO04/TXDE00/TXDE04/HDSL00_MISO2 | VDD1833_5 | 1.8 | 1.8 | |||

| L20 | SDIO_B_D0 | SDIO_B_IOPWR | ||||||

| L21 | SDIO_B_D1 | SDIO_B_IOPWR | ||||||

| M15 | ETH_A_(R)(G)MII_RX_ DV(_ER) | SOC.P21_3/ETH0_RXDV/DUEI13/HDSL00_CLK2 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| M16 | GND | |||||||

| M17 | ETH_IOPWR | |||||||

| M18 | ADC_0 | SOC.AN204 | 0 – 1.8V | |||||

| M19 | VCC_2_TEST | |||||||

| M20 | GND | |||||||

| M21 | SDIO_B_D2 | SDIO_B_IOPWR | ||||||

| N15 | ETH_A_(S)(R)(G)MII_RXD2 | SOC.P21_1/ETH0_RXD2/CANRXDP0/TST_OUT12/HDSL00_MISO1 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| N16 | ETH_A_SDP | SOC.P21_7/ETH0_REFCLK/RMII0_REFCLK/CANTXDSOC.P1/HDSL01_LINK | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| N17 | JTAG_TCK(SWCLK) | SOC.P08_3/TCK/SI10#/HDSL06_CLK2 (*1) | VDD33 | 3.3 | 1.8 | 1 | ||

| N18 | ADC_1 | SOC.AN205 | ||||||

| N19 | JTAG_TMS(SWDIO) | SOC.P08_1/TMS/DUEI10/HDSL06_MISO1 (*1) | VDD33 | 3.3 | 1.8 | 1 | ||

| N20 | SDIO_B_D3 | SDIO_B_IOPWR | ||||||

| N21 | SDIO_B_D4 | SDIO_B_IOPWR | ||||||

| P15 | ETH_A_(S)(R)(G)MII_RXD3 | SOC.P21_2/ETH0_RXD3/CANTXDP0/SI12#/HDSL00_MOSI1 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| P16 | Vendor Defined | SOC.P08_5/IRQ8/RSTOUT#/GTETRGSA/IIC_SCL1/SD1_PWEN/MCLK02/HDSL06_MISO2 (*1) | VDD33 | 3.3 | ||||

| P17 | JTAG_TDI | SOC.P08_2/TDI/TST_OUT10/HDSL06_MOSI1 (*1) | VDD33 | 3.3 | 1.8 | 1 | ||

| P18 | GND | |||||||

| P19 | JTAG_RTCK | |||||||

| P20 | SDIO_B_D5 | SDIO_B_IOPWR | ||||||

| P21 | SDIO_B_D6 | SDIO_B_IOPWR | ||||||

| R15 | ETH_A_(R)(G)MII_RX_ CLK | SOC.P20_6/ETH0_RXCLK/TST_OUT11/HDSL00_SMPL | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| R16 | GND | |||||||

| R17 | JTAG_TDO(SWO) | SOC.P08_4/TDO/HDSL06_SEL2 (*1) | VDD33 | 3.3 | 1.8 | 1 | ||

| R18 | BOOT_SEL1# | 1.8 | ||||||

| R19 | JTAG_nTRST | SOC.TRST# | VDD33 | 3.3 | 1.8 | 1 | ||

| R20 | GND | |||||||

| R21 | SDIO_B_D7 | SDIO_B_IOPWR | ||||||

| T15 | ETH_MDIO | SOC.P26_2/GMAC1_MDIO/ETHSW_MDIO/ESC_MDIO/CANTXDP1/HDSL04_LINK | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| T16 | ETH_MDC | SOC.P26_1/GMAC1_MDC/ETHSW_MDC/ESC_MDC/CANRXDP1/HDSL03_MOSI2 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| T17 | FORCE_RECOVERY# | bootstrsp circuit | 1.8 | |||||

| T18 | RESERVED | |||||||

| T19 | RESERVED | |||||||

| T20 | SDIO_B_IOPWR | |||||||

| T21 | SDIO_B_CD# | |||||||

| U15 | SPI_A_SDI_(IO0) | SOC.P05_6/XSPI0_IO0/SI07#/HDSL04_CLK2 | VDD1833_4 | 1.8 | 1.8 | |||

| U16 | SPI_A_SCK | SOC.P05_1/IRQ3/XSPI0_CKP/DUEI06/HDSL04_SMPL | VDD1833_4 | 1.8 | 1.8 | |||

| U17 | RESET_IN# | 1.8 | ||||||

| U18 | NC | |||||||

| U19 | BOOT_SEL0# | 1.8 | ||||||

| U20 | SDIO_B_WP | SDIO_B_IOPWR | ||||||

| U21 | SDIO_B_PWR_EN | SDIO_B_IOPWR | ||||||

| V15 | SPI_A_SDO_(IO1) | SOC.P05_7/XSPI0_IO1/DUEI08/HDSL04_SEL2 | VDD1833_4 | 1.8 | 1.8 | |||

| V16 | GND | |||||||

| V17 | Carrier_PWR_EN | 1.8 | ||||||

| V18 | I2S_MCLK | |||||||

| V19 | I2S_B_DATA_IN | |||||||

| V20 | GND | |||||||

| V21 | I2S_A_DATA_IN | |||||||

| W15 | SPI_A_HOLD_(IO3) | SOC.P06_1/XSPI0_IO3/SI08#/HDSL04_MOSI2 | VDD1833_4 | 1.8 | 1.8 | |||

| W16 | SPI_A_WP_(IO2) | SOC.P06_0/XSPI0_IO2/TST_OUT08/HDSL04_MISO2 | VDD1833_4 | 1.8 | 1.8 | |||

| W17 | RTC_PWR | |||||||

| W18 | I2S_LRCLK | |||||||

| W19 | I2S_B_DATA_OUT | |||||||

| W20 | I2S_BITCLK | |||||||

| W21 | I2S_A_DATA_OUT | |||||||

| Y13 | CARRIER_STBY# | |||||||

| Y14 | RESET_OUT# | SYS_RST_OUT# | 1.8 | |||||

| Y15 | SPI_A_CS0# | SOC.P05_3/IRQ5/XSPI0_CS0#/SI06#/HDSL04_SEL1 | VDD1833_4 | 1.8 | 1.8 | |||

| Y16 | VCC_3_TEST | |||||||

| Y17 | VCC_IN_5V | |||||||

| Y18 | GND | |||||||

| Y19 | VCC_IN_3V3 | |||||||

| Y20 | VCC_4_TEST | |||||||

| Y21 | SPI_B_SCK | SOC.P32_3/GTIOC10_0B/GTIOC01_0B/SPI_RSPCK1/ENCIFOE10/DEE10/HDSL08_MISO2 | VDD33 | 3.3 | 1.8 | 1 | ||

| Y22 | SPI_B_SDI | SOC.P32_5/GTIOC10_1B/GTIOC01_1B/SPI_MISO1/ENCIFDI10/RXDE10/HDSL09_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| Y23 | SPI_B_SDO | SOC.P32_4/GTIOC10_1A/GTIOC01_1A/SPI_MOSI1/ENCIFDO10/TXDE10/HDSL08_MOSI2 | VDD33 | 3.3 | 1.8 | 1 | ||

| AA13 | RESERVED | |||||||

| AA14 | GND | |||||||

| AA15 | I2C_A_SCL | SOC.P02_3/IRQ10/MTIOC6C/MTIOC1B/GTIOC01_4B/ETH3_COL/IIC_SCL0/IIC_SCL2/XSPI1_IO7/MDAT22/USB_OVRCUR/ENCIFDI01/RXDE01/HDSL01_MOSI2 | VDD1833_5 | 1.8 | 1.8 | |||

| AA16 | I2C_A_SDA | SOC.P02_4/IRQ11/POE0#/IIC_SDA0/MDAT20/USB_EXICEN/MBX_HINT#/HDSL02_LINK | VDD1833_5 | 1.8 | 1.8 | |||

| AA17 | GND | |||||||

| AA18 | VBAT | |||||||

| AA19 | GND | |||||||

| AA20 | I2C_B_SCL | SOC.P04_7/IRQ1/MTIOC6A/MTIOC0A/GTIOC03_4A/IIC_SCL1/ENCIFDO03/TXDE03/HDSL03_MOSI2 | VDD33 | 3.3 | 1.8 | 1 | ||

| AA21 | I2C_B_SDA | SOC.P05_0/IRQ2/MTIOC6C/MTIOC0B/GTIOC03_4B/IIC_SDA1/ENCIFDI03/RXDE03/HDSL04_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| AA22 | GND | |||||||

| AA23 | SPI_B_CS0# | SOC.P32_6/GTIOC10_2A/GTIOC01_2A/SPI_SSL10/ENCIFCK11/SCKE11/HDSL09_SMPL | VDD33 | 3.3 | 1.8 | 1 | ||

| AB13 | USB_A_D_N | SOC.USB_QDM | ||||||

| AB14 | USB_A_ID | SOC.USB_OTG_ID | 1.8 | |||||

| AB15 | GND | |||||||

| AB16 | USB_A_VBUS | SOC.USB_VBUSIN | 5 | |||||

| AB17 | CAN_A_RX | SOC.P24_3/IRQ14/ESC_I2CCLK/IIC_SCL1/CANRX0/MCLK70/HDSL03_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| AB18 | VBAT | |||||||

| AB19 | CAN_B_RX | SOC.P22_5/IRQ7/A20/GTETRGSA/GMAC0_PTPTRG0/ESC_LATCH0/CTS5#/CANRX1/SD0_CD/SI14#/HDSL01_CLK2 | VDD33 | 1.8 | 1.8 | 1 | ||

| AB20 | USB_B_VBUS | SOC.P03_0/D8/MTIOC4C/MTIC5V/GTIOC02_1B/GTADSM07_1/CMTW0_TOC1/MDAT01/HDSL02_MISO1 | VDD33 | 3.3 | 5 | 1 | ||

| AB21 | GND | |||||||

| AB22 | USB_B_ID | SOC.P03_1/D9/MTIOC4B/MTIOC1B/GTIOC02_2A/GTADSM08_0/CMTW1_TIC0/ENCIFDO02/TXDE02/HDSL02_MOSI1 | VDD33 | 3.3 | 1.8 | 1 | ||

| AB23 | USB_B_D_N | SOC.P03_2/IRQ12/D10/MTIOC4D/MTIOC1A/GTIOC02_2B/GTADSM08_1/CMTW1_TOC0/ENCIFDI02/RXDE02/HDSL02_CLK2 | VDD33 | 3.3 | 1 | |||

| AC14 | USB_A_D_P | SOC.USB_QDP | ||||||

| AC15 | USB_A_OC# | SOC.P00_1/IRQ0/D1/MTIOC3D/GTIOC00_0B/ETH3_RXER/USB_OVRCUR/TST_OUT00/HDSL00_SMPL | VDD33 | 3.3 | 1.8 | 1 | ||

| AC16 | USB_A_EN | SOC.P00_0/SEI/D0/MTIOC3B/GTIOC00_0A/ETH3_TXER/USB_VBUSEN/DUEI00/HDSL00_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| AC17 | CAN_A_TX | SOC.P24_4/IRQ15/ESC_I2CDATA/IIC_SDA1/CANTX0/MDAT70/HDSL03_SMPL | VDD33 | 3.3 | 1.8 | 1 | ||

| AC18 | DEBUG_EN | 1.8 | ||||||

| AC19 | CAN_B_TX | SOC.P22_6/IRQ8/A19/GTETRGSB/GMAC0_PTPTRG1/ESC_LATCH1/DE5/CANTX1/SD0_WP/DUEI15/HDSL01_SEL2 | VDD33 | 1.8 | 1.8 | 1 | ||

| AC20 | USB_B_EN | SOC.P13_0/D24/GTIOC02_3A/DE2/SPI_RSPCK3/SD0_DATA6/MCLK00/ENCIFCK12/ENCIFCK03/SCKE08/SCKE03/HDSL10_SEL1 | VDD1833_6 | SDIO_A_IOPWR | 1.8 | 1 | ||

| AC21 | USB_B_OC# | SOC.P13_1/D25/GTIOC02_3B/SPI_MOSI3/SD0_DATA7/MDAT00/ENCIFOE12/ENCIFOE03/DEE08/DEE03/HDSL10_MISO1 | VDD1833_6 | SDIO_A_IOPWR | 1.8 | 1 | ||

| AC22 | USB_B_D_P | SOC.P03_5/IRQ15/MTIOC3A/MTIC5W/GTIOC02_4A/IIC_SCL2/ENCIFDO02/TXDE02/HDSL02_MOSI2 | VDD33 | 3.3 | 1 | |||

| Size-S | A2 | CSI_DATA1_N | SOC.P03_3/IRQ13/D11/MTCLKA/MTIOC8C/GTIOC02_3A/GTADSM09_0/CMTW1_TIC1/IIC_SCL1/ENCIFCK02/SCKE02/HDSL02_SEL2 | VDD33 | 3.3 | 1 | ||

| A3 | CSI_DATA1_P | SOC.P03_4/IRQ14/D12/MTCLKB/MTIOC8D/GTIOC02_3B/GTADSM09_1/CMTW1_TOC1/RTCAT1HZ/IIC_SDA1/ENCIFOE02/DEE02/HDSL02_MISO2 | VDD33 | 3.3 | 1 | |||

| A4 | GND | |||||||

| A5 | CSI_DATA2_N | SOC.P03_6/MTIOC3C/MTIOC1A/GTIOC02_4B/IIC_SDA2/ENCIFDI02/RXDE02/HDSL03_LINK | VDD33 | 3.3 | 1 | |||

| A6 | CSI_DATA2_P | SOC.P28_5/CANRX0/SPI_SSL13/MCLK71/ENCIFCK08/ENCIFCK00/SCKE08/SCKE00/HDSL05_MISO2 | VDD33 | 3.3 | 1 | |||

| A7 | GND | |||||||

| A8 | USB_C_SSTX_P | SOC.P28_6/CANTX0/MDAT71/ENCIFOE08/ENCIFOE00/DEE08/DEE00/HDSL05_MOSI2 | VDD33 | 3.3 | 1 | |||

| A9 | USB_C_SSTX_N | SOC.P11_4/IRQ7/DE1/MCLK31/HDSL09_SMPL | VDD33 | 3.3 | 1 | |||

| A10 | GND | |||||||

| B1 | CSI_DATA0_P | SOC.P11_5/MDAT31/DUEI00/HDSL09_CLK1 | VDD33 | 3.3 | 1 | |||

| B2 | GND | |||||||

| B3 | CSI_CLOCK_N | SOC.P14_7/IRQ9/POE11#/GTIOC09_3A/CMTW0_TOC1/ESC_I2CDATA/IIC_SDA0/SD0_IOVS/MCLK32/SI02#/HDSL11_MISO2 | VDD33 | 3.3 | 1 | |||

| B4 | CSI_CLOCK_P | SOC.P15_0/GTIOC09_3B/MDAT32/ENCIFCK06/SCKE06/HDSL11_MOSI2 | VDD33 | 3.3 | 1 | |||

| B5 | GND | |||||||

| B6 | CSI_DATA3_N | SOC.P03_7/MTIOC6B/MTIOC1B/GTIOC03_0A/CMTW0_TIC0/DUEI04/HDSL03_SMPL | VDD33 | 3.3 | 1 | |||

| B7 | CSI_DATA3_P | SOC.P04_0/MTIOC6D/GTIOC03_0B/CMTW0_TOC0/TST_OUT04/HDSL03_CLK1 | VDD33 | 3.3 | 1 | |||

| B8 | GND | |||||||

| B9 | GND | |||||||

| B10 | USB_C_SSRX_P | SOC.P04_1/MTIOC7A/GTIOC03_1A/CMTW0_TIC1/SI04#/HDSL03_SEL1 | VDD33 | 3.3 | 1 | |||

| B11 | USB_C_SSRX_N | SOC.P04_2/MTIOC7C/GTIOC03_1B/CMTW0_TOC1/DUEI05/HDSL03_MISO1 | VDD33 | 3.3 | 1 | |||

| C1 | CSI_DATA0_N | SOC.P04_3/MTIOC7B/GTIOC03_2A/CMTW1_TIC0/TST_OUT05/HDSL03_MOSI1 | VDD33 | 3.3 | 1 | |||

| C2 | CAM_MCK | SOC.P04_4/MTIOC7D/GTIOC03_2B/CMTW1_TOC0/ADTRG0#/SI05#/HDSL03_CLK2 | VDD33 | 3.3 | 1 | |||

| C3 | I2C_CAM_SDA / CSI_TX_N | SOC.P04_5/SEI/MTCLKC/MTIOC0C/GTIOC03_3A/CMTW1_TIC1/IIC_SCL0/ADTRG1#/ENCIFCK03/SCKE03/HDSL03_SEL2 | VDD33 | 3.3 | 1 | |||

| C4 | I2C_CAM_SCL / CSI_TX_P | SOC.P04_6/IRQ0/MTCLKD/MTIOC0D/GTIOC03_3B/CMTW1_TOC1/IIC_SDA0/ADTRG2#/MBX_HINT#/ENCIFOE03/DEE03/HDSL03_MISO2 | VDD33 | 3.3 | 1 | |||

| C5 | VCC_6_TEST | |||||||

| C6 | ETH_B_MDC | SOC.P21_4/GMAC0_MDC/ETHSW_MDC/ESC_MDC/CANRX1/TST_OUT13/HDSL00_SEL2 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| C7 | ETH_B_MDIO | SOC.P21_5/GMAC0_MDIO/ETHSW_MDIO/ESC_MDIO/CANTX1/SI13#/HDSL00_MISO2 | VDD1833_0 | 1.8 | ETH_IOPWR | 1 | ||

| C8 | USB_C_OC# | |||||||

| C9 | USB_C_VBUS | |||||||

| C10 | USB_C_EN | |||||||

| C11 | GND | |||||||

| D1 | GND | |||||||

| D2 | ETH_B_(R)(G)MII_CRS | SOC.P27_0/IRQ1/CS5#/ETH1_CRS/CANTXDP0/SPI_SSL02/HSPI_INT#/ENCIFDI01/RXDE01/HDSL04_MOSI1 | VDD33 | 3.3 | ETH_IOPWR | 1 | ||

| D3 | GPIO_C_0 | SOC.P02_0/IRQ7/MTCLKC/MTIOC0C/GTIOC01_3A/ETH3_TXER/IIC_SDA1/XSPI1_IO4/MCLK21/ENCIFCK01/SCKE01/HDSL01_CLK2 | VDD1833_5 | 1.8 | 1.8 | |||

| D4 | GPIO_C_1 | SOC.P01_3/MTIOC6D/MTIC5U/GTIOC01_0B/GTIOC04_0B/XSPI1_DS/TST_OUT02/HDSL01_SMPL | VDD1833_5 | 1.8 | 1.8 | |||

| D5 | GND | |||||||

| D6 | Vendor Defined | PCIe_CLK_GEN.PCIe_B_CLK_EN# | 1.8 | |||||

| D7 | Vendor Defined | PCIe_CLK_GEN.PCIe_A_CLK_EN# | 1.8 | |||||

| D8 | GND | |||||||

| D9 | USB_C_ID | SOC.P08_6/SEI/CKIO/GTIOC08_3A/GTETRGSB/IIC_SDA1/SD1_IOVS/MDAT02/MCLK11/DUEI11/HDSL06_MOSI2 | VDD33 | 3.3 | 1 | |||

| D10 | USB_C_D_P | SOC.P15_1/GTIOC09_4A/MCLK40/ENCIFOE06/DEE06/HDSL12_LINK | VDD33 | 3.3 | 1 | |||

| D11 | USB_C_D_N | SOC.P15_2/GTIOC09_4B/MDAT40/ENCIFDO06/TXDE06/HDSL12_SMPL | VDD33 | 3.3 | 1 | |||

| E1 | ETH_B_(R)(G)MII_COL | SOC.P27_1/IRQ2/GTIOC02_0A/ETH1_COL/CANRX1/SPI_SSL03/HSPI_CS#/HDSL04_CLK2 | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| E2 | GND | |||||||

| E3 | GPIO_C_2 | SOC.P01_2/MTIOC6B/MTIOC8B/GTIOC01_0A/GTIOC04_0A/XSPI1_CS1#/DUEI02/HDSL01_LINK | VDD1833_5 | 1.8 | 1.8 | |||

| E4 | GPIO_C_3 | SOC.P01_1/MTIOC3C/MTIOC8A/GTIOC00_4B/XSPI1_CS0#/MCLK20/ENCIFDI00/ENCIFDI04/RXDE00/RXDE04/HDSL00_MOSI2 | VDD1833_5 | 1.8 | 1.8 | |||

| F1 | ETH_B_(S)(R)(G)MII_TXD1 | SOC.P24_7/MD1/ETH1_TXD1 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| F2 | ETH_B_(S)(R)(G)MII_TXD3 | SOC.P25_1/MDW0/ETH1_TXD3/CANTXDP0 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| F3 | GPIO_C_4 | SOC.P07_7/IIC_SCL0/XSPI0_WP0#/MCLK10/ENCIFDO05/TXDE05/HDSL06_CLK1 | VDD1833_4 | 1.8 | 1.8 | |||

| F4 | GPIO_C_5 | SOC.P08_0/RTCAT1HZ/IIC_SDA0/XSPI0_WP1#/MDAT10/MBX_HINT#/ENCIFDI05/RXDE05/HDSL06_SEL1 | VDD1833_4 | 1.8 | 1.8 | |||

| G1 | ETH_B_(S)(R)(G)MII_TXD0 | SOC.P24_6/MD0/ETH1_TXD0 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| G2 | ETH_B_(S)(R)(G)MII_TXD2 | SOC.P25_0/MD2/ETH1_TXD2/CANRXDP0 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| G3 | GPIO_C_6 | SOC.P01_4/MTIOC7A/MTIC5V/GTIOC01_1A/GTIOC04_1A/XSPI1_IO0/SI02#/HDSL01_CLK1 | VDD1833_5 | 1.8 | 1.8 | |||

| G4 | GPIO_C_7 | SOC.P35_6/GTADSM09_1/TXD4/SDA4/MOSI4/SPI_SSL12/MDAT92/SI10#/HDSL11_MOSI1 | VDD33 | 3.3 | 1.8 | 1 | ||

| H1 | ETH_B_(R)(G)MII_TX_CLK | SOC.P24_5/ETH1_TXCLK/HDSL03_CLK1 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| H2 | GND | |||||||

| H3 | RGB_CS# | SOC.P33_0/GTIOC10_3A/SPI_SSL12/MCLK82/ENCIFDO11/TXDE11/HDSL09_SEL1 | VDD33 | 3.3 | 3.3 | |||

| H4 | GND | |||||||

| J1 | ETH_B_(S)(R)(G)MII_RXD0 | SOC.P25_4/ETH1_RXD0/TST_OUT03/HDSL03_MISO1 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| J2 | ETH_B_(R)(G)MII_TX_EN(_ER) | SOC.P25_2/MDW1/ETH1_TXEN | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| J3 | RGB_RESET# | SOC.P33_1/GTIOC10_3B/SPI_SSL13/MDAT82/ENCIFDI11/RXDE11/HDSL09_MISO1 | VDD33 | 3.3 | 3.3 | |||

| J4 | RGB_DE | SOC.P09_7/WE0#/MTIOC7C/GTIOC04_1B/GTIOC10_1B/MDAT71/DISP_DE/DUEI14/HDSL07_MISO2 | VDD33 | 3.3 | 3.3 | |||

| K1 | ETH_B_(S)(R)(G)MII_RXD1 | SOC.P25_5/ETH1_RXD1/SI03#/HDSL03_MOSI1 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| K2 | ETH_B_(R)MII_RX_ER | SOC.P26_7/IRQ0/CS3#/ETH1_RXER/ESC_LEDSTER/CANRXDP0/SPI_SSL01/ENCIFDO01/TXDE01/HDSL04_MISO1 | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| K3 | RGB_HSYNC | SOC.P09_5/D14/MTIOC6D/GTIOC04_0B/GTIOC10_0B/MDAT70/DISP_HSYNC/TST_OUT13/HDSL07_CLK2 | VDD33 | 3.3 | 3.3 | |||

| K4 | RGB_DISP | SOC.P23_7/ETHSW_LPI1/MCLK61/DUEI02/HDSL02_CLK2 | VDD33 | 3.3 | 3.3 | |||

| L1 | ETH_B_(R)(G)MII_RX_DV(_ER) | SOC.P26_0/ETH1_RXDV/SI04#/HDSL03_MISO2 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| L2 | GND | |||||||

| L3 | RGB_VSYNC | SOC.P09_6/D15/MTIOC7A/GTIOC04_1A/GTIOC10_1A/MCLK71/DISP_VSYNC/SI13#/HDSL07_SEL2 | VDD33 | 3.3 | 3.3 | |||

| L4 | GND | |||||||

| M1 | ETH_B_(S)(R)(G)MII_RXD2 | SOC.P25_6/ETH1_RXD2/CANRX1/DUEI04/HDSL03_CLK2 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| M2 | ETH_B_SDP | SOC.P26_4/ETH1_REFCLK/RMII1_REFCLK | VDD1833_1 | 1.8 | ETH_IOPWR | |||

| M3 | RGB_B5 | SOC.P18_6/IRQ3/A14/GTIOC07_4A/GTADSM05_0/CTS1#/CANRXDP1/MCLK12/DISP_DATAB7/ENCIFDO13/ENCIFDO14/TXDE09/TXDE10/HDSL14_MOSI2 | VDD33 | 3.3 | 3.3 | |||

| M4 | RGB_(PIXEL)CLK | SOC.P09_4/D13/MTIOC6B/GTIOC04_0A/GTIOC10_0A/MCLK70/DISP_CLK/DUEI13/HDSL07_MOSI1 | VDD33 | 3.3 | 3.3 | |||

| N1 | ETH_B_(S)(R)(G)MII_RXD3 | SOC.P25_7/ETH1_RXD3/CANTX1/TST_OUT04/HDSL03_SEL2 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| N2 | RESERVED | |||||||

| N3 | RGB_B3 | SOC.P18_4/IRQ1/A12/GTIOC07_3A/GTADSM04_0/ESC_LEDSTER/TXD1/SDA1/MOSI1/CANRX1/MCLK11/DISP_DATAB5/ENCIFCK13/ENCIFCK14/SCKE09/SCKE10/HDSL14_SEL2 | VDD33 | 3.3 | 3.3 | |||

| N4 | RGB_B4 | SOC.P18_5/IRQ2/A13/GTIOC07_3B/GTADSM04_1/SS1#/CTS1#/RTS1#/CANTX1/MDAT11/DISP_DATAB6/ENCIFOE13/ENCIFOE14/DEE09/DEE10/HDSL14_MISO2 | VDD33 | 3.3 | 3.3 | |||

| P1 | ETH_B_(R)(G)MII_RX_CLK | SOC.P25_3/ETH1_RXCLK/DUEI03/HDSL03_SEL1 | VDD1833_1 | 1.8 | ETH_IOPWR | 1 | ||

| P2 | GND | |||||||

| P3 | RGB_B2 | SOC.P18_3/IRQ0/A11/GTADSM03_1/RTCAT1HZ/ETH1_COL/GMAC1_MDIO/RXD1/SCL1/MISO1/CANTX0/SD1_IOVS/MDAT10/DISP_DATAB4/HDSL14_CLK2 | VDD33 | 3.3 | 3.3 | |||

| P4 | GND | |||||||

| R1 | GND | |||||||

| R2 | PCIe_SM_ALERT# | SOC.P28_2/IRQ7/GTIOC08_1B/ETHSW_TDMAOUT3/SPI_SSL10/DUEI06/HDSL05_MOSI1 | VDD33 | 3.3 | 1.8 | 1 | ||

| R3 | RGB_B1 | SOC.P18_2/SEI/A10/GTADSM03_0/GTIOC07_3B/ETH1_CRS/GMAC1_MDC/SCK1/CANRX0/SD1_PWEN/MCLK10/DISP_DATAB3/HDSL14_MOSI1 | VDD33 | 3.3 | 3.3 | |||

| R4 | RGB_B0 | SOC.P18_1/IRQ15/A9/GTADSM02_1/GTIOC07_3A/ESC_LEDERR/CTS0#/CANTXDP0/SD1_IOVS/DISP_DATAB2/SI08#/HDSL14_MISO1 | VDD33 | 3.3 | 3.3 | |||

| T1 | PCIe_SMCLK | SOC.P07_5/IIC_SCL2/XSPI0_ECS0#/MCLK02/ENCIFCK05/SCzKE05/HDSL06_LINK | VDD1833_4 | 1.8 | 1.8 | |||

| T2 | PCIe_Wake | SOC.P28_1/IRQ6/GTIOC08_1A/ETHSW_TDMAOUT2/SPI_MISO1/SI05#/HDSL05_MISO1 | VDD33 | 3.3 | 1.8 | 1 | ||

| T3 | RGB_G4 | SOC.P14_6/IRQ8/POE10#/GTIOC06_2B/GTIOC09_2B/CMTW0_TIC1/ESC_I2CCLK/DE4/IIC_SCL0/SD0_PWEN/DISP_DATAG6/TST_OUT02/HDSL11_SEL2 | VDD33 | 3.3 | 3.3 | |||

| T4 | RGB_G5 | SOC.P17_6/WE2#/GTADSM01_0/GTETRGD/CMTW1_TIC1/ETHSW_PTPOUT0/ESC_SYNC0/RXD0/SCL0/MISO0/SD1_PWEN/DISP_DATAG7/SI07#/HDSL14_SMPL | VDD33 | 3.3 | 3.3 | |||

| U1 | PCIe_SMDAT | SOC.P07_6/IIC_SDA2/XSPI0_ECS1#/MDAT02/ENCIFOE05/DEE05/HDSL06_SMPL | VDD1833_4 | 1.8 | 1.8 | |||

| U2 | GND | |||||||

| U3 | RGB_G3 | SOC.P14_5/TEND/POE8#/GTIOC06_2A/GTIOC09_2A/GTIOC06_3B/CMTW0_TOC0/ESC_RESETOUT#/CTS4#/DISP_DATAG5/ENCIFDI00/RXDE00/HDSL11_CLK2 | VDD33 | 3.3 | 3.3 | |||

| U4 | GND | |||||||

| V1 | GND | |||||||

| V2 | PCIe_A_PERST# | SOC.P05_4/IRQ6/IIC_SDA2/XSPI0_CS1#/DUEI07/HDSL04_MISO1 | VDD1833_4 | 1.8 | 1.8 | |||

| V3 | RGB_G1 | SOC.P14_3/IRQ6/DREQ/POE0#/GTIOC06_1A/GTIOC09_1A/ESC_LINKACT2/TXD4/SDA4/MOSI4/SD1_CD/DISP_DATAG3/ENCIFOE00/DEE00/HDSL11_MISO1 | VDD33 | 3.3 | 3.3 | |||

| V4 | RGB_G2 | SOC.P14_4/DACK/POE4#/GTIOC06_1B/GTIOC09_1B/GTIOC06_3A/CMTW0_TIC0/ESC_IRQ/SS4#/CTS4#/RTS4#/SD1_WP/DISP_DATAG4/MBX_HINT#/ENCIFDO00/TXDE00/HDSL11_MOSI1 | VDD33 | 3.3 | 3.3 | |||

| W1 | PCIe_REFCLK_P | PCIe_CLK_GEN.DIF1 | ||||||

| W2 | PCIe_CLKREQ# | PCIe_CLK_GEN.vOE1# | 1.8 | |||||

| W3 | GND | |||||||

| W4 | RGB_G0 | SOC.P14_2/BS#/GTIOC06_0B/GTIOC09_0B/GTIOC05_3B/RXD4/SCL4/MISO4/SD0_WP/DISP_DATAG2/ENCIFCK00/SCKE00/HDSL11_SEL1 | VDD33 | 3.3 | 3.3 | |||

| Y1 | PCIe_REFCLK_N | PCIe_CLK_GEN.DIF1# | ||||||

| Y2 | GND | |||||||

| Y3 | VCC_5_TEST | |||||||

| Y4 | RGB_R5 | SOC.P10_7/IRQ9/A4/MTIC5U/GTIOC05_0B/GTIOC00_3A/SCK1/MDAT21/DISP_DATAR7/HDSL08_CLK2/POUTB | VDD33 | 3.3 | 3.3 | |||

| Y5 | RGB_R4 | SOC.P10_6/IRQ0/A3/MTIOC0B/GTIOC05_0A/DE0/MCLK21/DISP_DATAR6/HDSL08_MOSI1/POUTA | VDD33 | 3.3 | 3.3 | |||

| Y6 | RGB_R2 | SOC.P10_4/IRQ3/A1/MTIOC1A/GTIOC04_4A/SS0#/CTS0#/RTS0#/MCLK11/MCLK01/DISP_DATAR4/ENCIFDO04/TXDE04/HDSL08_SEL1 | VDD33 | 3.3 | 3.3 | |||

| Y7 | RGB_R0 | SOC.P10_2/IRQ1/CS0#/MTCLKC/MTIOC2A/GTIOC04_3A/GTIOC10_3A/RXD0/SCL0/MISO0/MCLK10/MCLK00/DISP_DATAR2/ENCIFCK04/SCKE04/HDSL08_SMPL | VDD33 | 3.3 | 3.3 | |||

| Y8 | VCC_IN_5V | |||||||

| Y9 | VCC_IN_5V | |||||||

| Y10 | VCC_IN_5V | |||||||

| Y11 | VCC_IN_5V | |||||||

| AA1 | GND | |||||||

| AA2 | RESERVED | |||||||

| AA3 | DSI_TE | SOC.P08_7/IRQ0/A0/GTIOC08_3B/IIC_SCL2/IIC_SCL1/MDAT11/TST_OUT11/HDSL07_LINK | VDD33 | 3.3 | 1 | |||

| AA4 | GND | |||||||

| AA5 | RGB_R3 | SOC.P10_5/A2/MTIOC1B/MTIOC0A/GTIOC04_4B/CTS0#/MDAT11/MDAT01/DISP_DATAR5/ENCIFDI04/RXDE04/HDSL08_MISO1 | VDD33 | 3.3 | 3.3 | |||

| AA6 | RGB_R1 | SOC.P10_3/IRQ2/RD#/MTCLKD/MTIOC2B/GTIOC04_3B/GTIOC10_3B/TXD0/SDA0/MOSI0/MDAT10/MDAT00/DISP_DATAR3/ENCIFOE04/DEE04/HDSL08_CLK1 | VDD33 | 3.3 | 3.3 | |||

| AA7 | GND | |||||||

| AA8 | GND | |||||||

| AA9 | PWR_BTN# | SEQ.5V_Q | ||||||

| AA10 | GND | |||||||

| AA11 | GND | |||||||

| AB1 | PCIe_A_HSI0_P | SOC.PCIE_RXDP_L0 | ||||||

| AB2 | PCIe_A_HSI0_N | SOC.PCIE_RXDN_L0 | ||||||

| AB3 | GND | |||||||

| AB4 | DSI_DATA3_P | SOC.P10_0/IRQ4/WE1#/MTIOC7B/GTIOC04_2A/GTIOC10_2A/MCLK72/DISP_DATAR0/TST_OUT14/HDSL07_MOSI2 | VDD33 | 3.3 | 1 | |||

| AB5 | DSI_DATA3_N | SOC.P10_1/IRQ7/WAIT#/MTIOC7D/GTIOC04_2B/GTIOC10_2B/SCK0/MDAT72/DISP_DATAR1/SI14#/HDSL08_LINK | VDD33 | 3.3 | 1 | |||

| AB6 | GND | |||||||

| AB7 | DSI_CLOCK_P | SOC.P09_1/MDAT12/DUEI12/HDSL07_CLK1 | VDD33 | 3.3 | 1 | |||

| AB8 | DSI_CLOCK_N | SOC.P02_6/D6/MTIOC3D/MTIOC8B/GTIOC02_0B/GTADSM06_1/CMTW0_TOC0/SD0_IOVS/MDAT00/HDSL02_CLK1/POUTB | VDD33 | 3.3 | 1 | |||

| AB9 | GND | |||||||

| AB10 | DSI_DATA0_P | SOC.P02_5/D5/MTIOC3B/MTIOC8A/GTIOC02_0A/GTADSM06_0/CMTW0_TIC0/IIC_SCL0/SD0_PWEN/MCLK00/HDSL02_SMPL/POUTA | VDD33 | 3.3 | 1 | |||

| AB11 | DSI_DATA0_N | SOC.P02_7/D7/MTIOC4A/MTIC5U/GTIOC02_1A/GTADSM07_0/CMTW0_TIC1/MCLK01/HDSL02_SEL1/POUTZ | VDD33 | 3.3 | 1 | |||

| AC2 | PCIe_A_HSO0_P | SOC.PCIE_TXDP_L0 | ||||||

| AC3 | PCIe_A_HSO0_N | SOC.PCIE_TXDN_L0 | ||||||

| AC4 | GND | |||||||

| AC5 | DSI_DATA2_P | SOC.P09_0/IIC_SDA2/MCLK12/SI11#/HDSL07_SMPL | VDD33 | 3.3 | 1 | |||

| AC6 | DSI_DATA2_N | |||||||

| AC7 | GND | |||||||

| AC8 | DSI_DATA1_P | |||||||

| AC9 | DSI_DATA1_N | SOC.P00_2/IRQ1/D2/MTIOC4A/GTIOC00_1A/ETH3_CRS/ADTRG0#/USB_EXICEN/SI00#/HDSL00_CLK1 | VDD33 | 3.3 | 1 | 1 | ||

| AC10 | GND | |||||||

| Size-M | A26 | GND | ||||||

| A27 | USB_D_SSTX_P | |||||||

| A28 | USB_D_SSTX_N | |||||||

| A29 | GND | |||||||

| A30 | eDP_A_LANE0_P | |||||||

| A31 | eDP_A_LANE0_N | |||||||

| A32 | GND | |||||||

| A33 | eDP_A_LANE2_P | |||||||

| A34 | eDP_A_LANE2_N | |||||||

| B25 | USB_D_SSRX_P | |||||||

| B26 | USB_D_SSRX_N | |||||||

| B27 | GND | |||||||

| B28 | GND | |||||||

| B29 | VCC_8_TEST | |||||||

| B30 | GND | |||||||

| B31 | eDP_A_LANE1_P | |||||||

| B32 | eDP_A_LANE1_N | |||||||

| B33 | GND | |||||||

| B34 | eDP_A_LANE3_P | |||||||

| B35 | eDP_A_LANE3_N | |||||||

| C25 | GND | |||||||

| C26 | USB_D_EN | |||||||

| C27 | USB_D_VBUS | |||||||

| C28 | USB_D_OC# | |||||||

| C29 | SPI_C_SDI | 1.8 | ||||||

| C30 | SPI_C_CS0# | 1.8 | ||||||

| C31 | eDP_A_BL_PWM | SOC.P15_4/GTIOC09_5B/MDAT41/ENCIFCK07/SCKE07/HDSL12_SEL1 | VDD33 | 3.3 | 1 | |||

| C32 | GND | |||||||

| C33 | eDP_A_AUX_P | |||||||

| C34 | eDP_A_AUX_N | |||||||

| C35 | GND | |||||||

| D25 | USB_D_D_P | |||||||

| D26 | USB_D_D_N | |||||||

| D27 | USB_D_ID | |||||||

| D28 | GND | |||||||

| D29 | SPI_C_SCK | |||||||

| D30 | SPI_C_SDO | |||||||

| D31 | eDP_A_BL_EN | |||||||

| D32 | eDP_A_AUX_SEL | SOC.P13_2/IRQ3/D26/SPI_MISO3/SD0_RST#/MCLK01/ENCIFDO12/ENCIFDO03/TXDE08/TXDE03/HDSL10_MOSI1 | VDD1833_6 | SDIO_A_IOPWR | 1 | |||

| D33 | eDP_A_HPD | |||||||

| D34 | GND | |||||||

| D35 | eDP_B_LANE0_P | |||||||

| E32 | eDP_B_BL_EN | SOC.P12_7/IRQ2/D23/GTIOC05_4B/CMTW1_TOC1/CTS2#/SD0_DATA5/MDAT10/ENCIFDI05/RXDE05/HDSL10_CLK1 | VDD1833_6 | SDIO_A_IOPWR | 1 | |||

| E33 | eDP_B_BL_PWM | SOC.P15_6/IRQ1/GTIOC09_6B/MDAT42/ENCIFDO07/TXDE07/HDSL12_MOSI1 | VDD33 | 3.3 | 1 | |||

| E34 | eDP_B_LANE1_P | |||||||

| E35 | eDP_B_LANE0_N | |||||||

| F32 | eDP_B_UX_SEL | SOC.P15_7/SS5#/CTS5#/RTS5#/MCLK50/ENCIFDI07/RXDE07/HDSL12_CLK2 | VDD33 | 3.3 | 1 | |||

| F33 | GND | |||||||

| F34 | eDP_B_LANE1_N | |||||||

| F35 | GND | |||||||

| G32 | eDP_B_HPD | |||||||

| G33 | eDP_B_AUX_P | SOC.P12_6/D22/GTIOC05_4A/GTIOC01_3B/CMTW1_TIC1/SS2#/CTS2#/RTS2#/SD0_DATA4/MCLK10/ENCIFDO05/TXDE05/HDSL10_SMPL | 1 | |||||

| G34 | GND | |||||||

| G35 | eDP_B_LANE2_P | |||||||

| H32 | GND | |||||||

| H33 | eDP_B_UX_N | SOC.P11_7/GTIOC05_0B/SI00#/HDSL09_MISO1 | VDD33 | 3.3 | 1 | |||

| H34 | eDP_B_LANE3_P | SOC.P16_1/DE5/MCLK51/TST_OUT03/HDSL12_MISO2 | VDD33 | 3.3 | 1 | |||

| H35 | eDP_B_LANE2_N | |||||||

| J32 | RESERVED | |||||||

| J33 | GND | |||||||

| J34 | eDP_B_LANE3_N | SOC.P16_2/SCK5/MDAT51/SI03#/HDSL12_MOSI2 | VDD33 | 3.3 | 1 | |||

| J35 | GND | |||||||

| K32 | GND | |||||||

| K33 | RESERVED | |||||||

| K34 | GND | |||||||

| K35 | PCIe_B_HSO0_P | SOC.PCIE_TXDP_L1 | ||||||

| L32 | RESERVED | |||||||

| L33 | PCIe_B_PERST# | SOC.P14_0/IRQ5/A0/GTIOC06_4B/ETHSW_PTPOUT2/ESC_SYNC0/DE3/MCLK42/HDSL11_SMPL | VDD1833_6 | SDIO_A_IOPWR | ||||

| L34 | PCIe_B_HSI0_P | SOC.PCIE_RXDP_L1 | ||||||

| L35 | PCIe_B_HSO0_N | SOC.PCIE_TXDN_L1 | ||||||

| M32 | GND | |||||||

| M33 | RESERVED | |||||||

| M34 | PCIe_B_HSI0_N | SOC.PCIE_RXDN_L1 | ||||||

| M35 | GND | |||||||

| N32 | RESERVED | |||||||

| N33 | ETH_CDE_MDC | SOC.P30_5/GTIOC09_6A/GMAC2_MDC/ETHSW_MDC/ESC_MDC/SPI_RSPCK3/DUEI07/HDSL07_MISO1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| N34 | GND | |||||||

| N35 | ETH_C_(R)(G)MII_TX_CLK | SOC.P29_1/GTIOC09_0A/ETH2_TXCLK/ENCIFCK09/SCKE09/HDSL06_CLK1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| P32 | RESERVED | |||||||

| P33 | ETH_CDE_MDIO | SOC.P30_6/GTIOC09_6B/GMAC2_MDIO/ETHSW_MDIO/ESC_MDIO/SPI_MOSI3/TST_OUT07/HDSL07_MOSI1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| P34 | RESERVED | |||||||

| P35 | ETH_C_(S)(R)(G)MII_RXD3 | SOC.P30_3/IRQ11/GTIOC09_5A/ETH2_RXD3/SPI_MISO2/ENCIFDO11/TXDE11/HDSL07_CLK1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| R32 | GND | |||||||

| R33 | RESERVED | |||||||

| R34 | ETH_C_SDP | SOC.P31_0/ETH2_REFCLK/RMII2_REFCLK/GTETRGSA/SPI_SSL30/HDSL07_SEL2 | VDD1833_2 | 1.8 | ETH_IOPWR | |||

| R35 | ETH_C_(S)(R)(G)MII_RXD2 | SOC.P30_2/IRQ10/GTIOC09_4B/ETH2_RXD2/SPI_MOSI2/ENCIFOE11/DEE11/HDSL07_SMPL | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| T32 | RESERVED | |||||||

| T33 | RESERVED | |||||||

| T34 | GND | |||||||

| T35 | ETH_C_(R)(G)MII_RX_DV(_ER) | SOC.P30_4/GTIOC09_5B/ETH2_RXDV/ENCIFDI11/RXDE11/HDSL07_SEL1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| U32 | GPIO_D_0 | SOC.P07_1/IRQ14/POE8#/IIC_SCL0/XSPI0_RSTO0#/MCLK00/ENCIFCK04/ENCIFCK12/SCKE04/SCKE08/HDSL05_CLK2 | VDD1833_4 | 1.8 | 1.8 | |||

| U33 | GPIO_D_1 | SOC.P07_2/IRQ15/POE10#/IIC_SDA0/XSPI0_RSTO1#/MDAT00/ENCIFOE04/ENCIFOE12/DEE04/DEE08/HDSL05_SEL2 | VDD1833_4 | 1.8 | 1.8 | |||

| V32 | GPIO_D_2 | SOC.P01_7/MTIOC7D/MTIOC0B/GTIOC01_2B/GTIOC04_2B/XSPI1_IO3/SI03#/HDSL01_MOSI1 | VDD1833_5 | 1.8 | 1.8 | |||

| V33 | GPIO_D_3 | SOC.P07_4/IIC_SDA1/XSPI0_INT1#/MDAT01/ENCIFDI04/ENCIFDI12/RXDE04/RXDE08/HDSL05_MOSI2 | VDD1833_4 | 1.8 | 1.8 | |||

| U34 | ETH_C_(R)(G)MII_RX_ER | SOC.P31_3/POE4#/ETH2_RXER/ETHSW_TDMAOUT1/ESC_LEDERR/SPI_SSL33/MDAT80/MCLK31/HSPI_IO5/ENCIFOE09/DEE09/HDSL08_LINK | VDD33 | 3.3 | ETH_IOPWR | 1 | ||

| U35 | ETH_C_(S)(R)(G)MII_RXD1 | SOC.P30_1/GTIOC09_4A/ETH2_RXD1/ENCIFCK11/SCKE11/HDSL07_LINK | VDD1833_2 | 1.8 | ETH_IOPWR | |||

| V34 | ETH_C_(R)(G)MII_TX_EN | SOC.P29_6/GTIOC09_2B/ETH2_TXEN/SPI_SSL22/ENCIFOE10/DEE10/HDSL06_SEL2 | VDD1833_2 | 1.8 | ETH_IOPWR | |||

| V35 | ETH_C(S)(R)(G)MII_RXD0 | SOC.P30_0/GTIOC09_3B/ETH2_RXD0/ENCIFDI10/RXDE10/HDSL06_MOSI2 | VDD1833_2 | 1.8 | ETH_IOPWR | |||

| W32 | GPIO_D_4 | SOC.P14_1/RD/WR#/GTIOC06_0A/GTIOC09_0A/GTIOC05_3A/RTCAT1HZ/SCK4/SD0_CD/MDAT42/DISP_DATAG1/DUEI02/HDSL11_CLK1 | VDD33 | 3.3 | 1.8 | 1 | ||

| W33 | GPIO_D_5 | SOC.P17_5/A7/DACK/GTADSM00_1/GTETRGC/CMTW1_TOC0/SCK0/CANTX0/SD1_WP/TST_OUT07/HDSL14_LINK | VDD33 | 3.3 | 1.8 | 1 | ||

| W34 | GND | |||||||

| W35 | ETH_C_(R)(G)MII_RX_CLK | SOC.P29_7/GTIOC09_3A/ETH2_RXCLK/SPI_SSL23/ENCIFDO10/TXDE10/HDSL06_MISO2 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| Y25 | VCC_IN_5V | |||||||

| Y26 | VCC_IN_5V | |||||||

| Y27 | VCC_IN_5V | |||||||

| Y28 | VCC_IN_5V | |||||||

| Y29 | Vendor Defined | SOC.P15_3/GTIOC09_5A/MCLK41/ENCIFDI06/RXDE06/HDSL12_CLK1 | VDD33 | 3.3 | 1.8 | |||

| Y30 | Vendor Defined | SOC.P17_3/IRQ15/GTETRGA/SI06#/HDSL13_MISO2 | VDD1833_7 | 3.3 | 1.8 | |||

| Y31 | Vendor Defined | SOC.P19_4/GTIOC07_2A/TST_OUT10/HDSL15_MOSI1 | VDD33 | 3.3 | 1.8 | |||

| Y32 | GPIO_D_6 | SOC.P02_2/IRQ9/MTIOC6A/MTIOC1A/GTIOC01_4A/ETH3_CRS/IIC_SDA2/XSPI1_IO6/MCLK22/USB_VBUSEN/ENCIFDO01/TXDE01/HDSL01_MISO2 | VDD1833_5 | 1.8 | 1.8 | |||

| Y33 | GPIO_D_7 | SOC.P02_1/IRQ8/MTCLKD/MTIOC0D/GTIOC01_3B/ETH3_RXER/IIC_SCL2/XSPI1_IO5/MDAT21/ENCIFOE01/DEE01/HDSL01_SEL2 | VDD1833_5 | 1.8 | 1.8 | |||

| Y34 | ETH_C_(S)(R)(G)MII_TXD2 | SOC.P29_4/IRQ8/GTIOC09_1B/ETH2_TXD2/SPI_SSL20/ENCIFDI09/RXDE09/HDSL06_MOSI1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| Y35 | ETH_C_(S)(R)(G)MII_TXD0 | SOC.P29_2/GTIOC09_0B/ETH2_TXD0/ENCIFOE09/DEE09/HDSL06_SEL1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| AA25 | GND | |||||||

| AA26 | GND | |||||||

| AA27 | GND | |||||||

| AA28 | GND | |||||||

| AA29 | Vendor Defined | RTC.IRQ/FOUT | ||||||

| AA30 | Vendor Defined | SOC.P17_7/WE3#/AH#/GTADSM01_1/CMTW1_TOC1/ETHSW_PTPOUT1/ESC_SYNC1/TXD0/SDA0/MOSI0/SD1_IOVS/DISP_DATAB0/DUEI08/HDSL14_CLK1 | VDD33 | 3.3 | 1.8 | 1 | ||

| AA31 | Vendor Defined | SOC.P18_0/IRQ7/A8/TEND/GTADSM02_0/ESC_LEDRUN/SS0#/CTS0#/RTS0#/CANRXDP0/SD1_PWEN/DISP_DATAB1/TST_OUT08/HDSL14_SEL1 | VDD33 | 3.3 | 1.8 | 1 | ||

| AA32 | GND | |||||||

| AA33 | VCC_7_TEST | |||||||

| AA34 | ETH_C_(S)(R)(G)MII_TXD3 | SOC.P29_5/IRQ9/GTIOC09_2A/ETH2_TXD3/SPI_SSL21/ENCIFCK10/SCKE10/HDSL06_CLK2 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| AA35 | ETH_C_(S)(R)(G)MII_TXD1 | SOC.P29_3/GTIOC09_1A/ETH2_TXD1/ENCIFDO09/TXDE09/HDSL06_MISO1 | VDD1833_2 | 1.8 | ETH_IOPWR | 1 | ||

| AB25 | RESERVED | |||||||

| AB26 | RESERVED | |||||||

| AB27 | UFS_RESET# | SOC.P16_0/IRQ2/CTS5#/MDAT50/TXDE07/DUEI03/HDSL12_SEL2 | VDD33 | 3.3 | 1 | |||

| AB28 | GND | |||||||

| AB29 | UFS_TX1_P | SOC.P19_1/GTIOC07_0B/TST_OUT09/HDSL15_CLK1 | VDD33 | 3.3 | 1 | |||

| AB30 | UFS_TX1_N | SOC.P19_0/GTIOC07_0A/DUEI09/HDSL15_SMPL | VDD33 | 3.3 | 1 | |||

| AB31 | GND | |||||||

| AB32 | UFS_RX1_P | SOC.P19_2/GTIOC07_1A/SI09#/HDSL15_SEL1 | VDD33 | 3.3 | 1 | |||

| AB33 | UFS_RX1_N | SOC.P24_0/IRQ11/ETHSW_LPI2/MDAT61/TST_OUT02/HDSL02_SEL2 | VDD33 | 3.3 | 1 | |||

| AB34 | GND | |||||||

| AB35 | ETH_C_(R)(G)MII_COL | SOC.P31_5/DACK/POE10#/ETH2_COL/ETHSW_PTPOUT3/ESC_SYNC1/SPI_MOSI0/SPI_SSL31/MDAT81/MCLK32/HSPI_IO7/ENCIFDI09/RXDE09/HDSL08_CLK1/POUTZ | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| AC26 | UFS_CLK | SOC.P15_5/IRQ0/GTIOC09_6A/MCLK42/ENCIFOE07/DEE07/HDSL12_MISO1 | 1 | |||||

| AC27 | GND | |||||||

| AC28 | UFS_TX0_P | SOC.P19_7/MDAT52/HDSL15_MISO2 | VDD33 | 3.3 | 1 | |||

| AC29 | UFS_TX0_N | SOC.P19_6/MCLK52/HDSL15_SEL2 | VDD33 | 3.3 | 1 | |||

| AC30 | GND | |||||||

| AC31 | UFS_RX0_P | SOC.P19_3/GTIOC07_1B/DUEI10/HDSL15_MISO1 | VDD33 | 3.3 | 1 | |||

| AC32 | UFS_RX0_N | SOC.P18_7/IRQ4/A15/GTIOC07_4B/GTADSM05_1/ETHSW_PTPOUT3/ESC_SYNC1/DE1/CANTXDP1/MDAT12/ENCIFDI13/ENCIFDI14/RXDE09/RXDE10/HDSL15_LINK | VDD33 | 3.3 | 1 | |||

| AC33 | GND | |||||||

| AC34 | ETH_C_(R)(G)MII_CRS | SOC.P31_4/DREQ/POE8#/ETH2_CRS/ETHSW_PTPOUT2/ESC_SYNC0/SPI_RSPCK0/SPI_SSL30/MCLK81/MDAT31/HSPI_IO6/ENCIFDO09/TXDE09/HDSL08_SMPL/POUTB | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| Size-S | AE2 | GND | ||||||

| AE3 | ETH_D_(R)(G)MII_CRS | SOC.P35_1/TEND/GTADSM07_0/ETH3_CRS/SPI_SSL30/SPI_MISO1/MCLK90/DUEI09/HDSL11_LINK | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| AE4 | VCC_IN_5V | |||||||

| AF1 | ETH_D_(S)(R)(G)MII_TXD0 | SOC.P33_3/IRQ12/A17/GTADSM00_1/ETH3_TXD0/RXD1/SCL1/MISO1/SPI_MOSI1/SPI_RSPCK0/MDAT50/PCIE_RSTOUT0B/ENCIFOE01/DEE01/HDSL09_CLK2 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AF2 | ETH_D_(S)(R)(G)MII_TXD3 | SOC.P33_6/IRQ15/A20/GTADSM02_0/ETH3_TXD3/TXD2/SDA2/MOSI2/SPI_SSL11/SPI_SSL00/MCLK52/ENCIFCK06/SCKE06/HDSL09_MOSI2 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AF3 | ETH_D_(R)(G)MII_COL | SOC.P35_2/GTADSM07_1/ETH3_COL/SPI_SSL31/SPI_SSL10/MDAT90/ADTRG2#/TST_OUT09/HDSL11_SMPL | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| AF4 | VCC_IN_5V | |||||||

| AG1 | ETH_D_(S)(R)(G)MII_TXD1 | SOC.P33_4/IRQ13/A18/GTADSM01_0/ETH3_TXD1/TXD1/SDA1/MOSI1/SPI_MISO1/SPI_MOSI0/MCLK51/PCIE_RSTOUT1B/ENCIFDO01/TXDE01/HDSL09_SEL2 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AG2 | ETH_D_(S)(R)(G)MII_TXD2 | SOC.P33_5/IRQ14/A19/GTADSM01_1/ETH3_TXD2/RXD2/SCL2/MISO2/SPI_SSL10/SPI_MISO0/MDAT51/ENCIFDI01/RXDE01/HDSL09_MISO2 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AG3 | GND | |||||||

| AG4 | VCC_IN_5V | |||||||

| AH1 | ETH_D_(R)(G)MII_TX_CLK | SOC.P33_2/A16/GTADSM00_0/ETH3_TXCLK/SCK1/SPI_RSPCK1/SPI_SSL30/MCLK50/ENCIFCK01/SCKE01/HDSL09_MOSI1 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AH2 | GND | |||||||

| AH3 | VCC_IN_5V | |||||||

| AH4 | VCC_IN_5V | |||||||

| AJ1 | ETH_D_(S)(R)(G)MII_RXD0 | SOC.P34_1/A23/GTADSM03_1/GTIOC03_0B/ETH3_RXD0/SPI_MISO2/ENCIFDI06/RXDE06/HDSL10_CLK1 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AJ2 | ETH_D_(R)(G)MII_TX_EN(_ER) | SOC.P33_7/A21/GTADSM02_1/ETH3_TXEN/SPI_RSPCK2/MDAT52/ENCIFOE06/DEE06/HDSL10_LINK | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AJ3 | VCC_IN_5V | |||||||

| AJ4 | VCC_IN_5V | |||||||

| AK1 | ETH_D_(S)(R)(G)MII_RXD1 | SOC.P34_2/A24/GTADSM04_0/GTIOC03_1A/ETH3_RXD1/SPI_SSL20/ENCIFCK07/SCKE07/HDSL10_SEL1 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AK2 | ETH_D_(R)MII_RX_ER | SOC.P35_0/DACK/GTADSM06_1/ETH3_RXER/SPI_MISO3/SI08#/HDSL10_MOSI2 | VDD33 | 3.3 | ETH_IOPWR | 1 | 1 | |

| AK3 | GND | |||||||

| AK4 | VCC_IN_5V | |||||||

| AL1 | ETH_D_(R)(G)MII_RX_DV(_ER) | SOC.P34_5/CS3#/GTADSM05_1/GTIOC03_2B/ETH3_RXDV/ESC_I2CCLK/TXD3/SDA3/MOSI3/IIC_SCL1/SPI_SSL23/ADTRG1#/ENCIFDI07/RXDE07/HDSL10_CLK2 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AL2 | GND | |||||||

| AL3 | RESERVED | |||||||

| AL4 | RESERVED | |||||||

| AM1 | ETH_D_(S)(R)(G)MII_RXD2 | SOC.P34_3/A25/GTADSM04_1/GTIOC03_1B/ETH3_RXD2/SPI_SSL21/SD1_PWEN/ENCIFOE07/DEE07/HDSL10_MISO1 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AM2 | ETH_D_SDP | SOC.P34_6/ETH3_REFCLK/RMII3_REFCLK/CS5#/ETH1_RXER/ESC_I2CDATA/IIC_SDA1/SPI_RSPCK3/ADTRG2#/DUEI08/HDSL10_SEL2 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AM3 | RESERVED | |||||||

| AM4 | RESERVED | |||||||

| AM5 | RESERVED | |||||||

| AM6 | RESERVED | |||||||

| AM7 | RESERVED | |||||||

| AM8 | RESERVED | |||||||

| AM9 | RESERVED | |||||||

| AM10 | RESERVED | |||||||

| AM11 | LVDS_I2C_CLK | |||||||

| AM12 | LVDS_I2C_DAT | |||||||

| AN1 | ETH_D_(S)(R)(G)MII_RXD3 | SOC.P34_4/CS2#/GTADSM05_0/GTIOC03_2A/ETH3_RXD3/RXD3/SCL3/MISO3/SPI_SSL22/SD1_IOVS/ADTRG0#/ENCIFDO07/TXDE07/HDSL10_MOSI1 | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AN2 | RESERVED | |||||||

| AN3 | GND | |||||||

| AN4 | ETH_E_(R)(G)MII_CRS | |||||||

| AN5 | RESERVED | |||||||

| AN6 | GND | |||||||

| AN7 | RESERVED | |||||||

| AN8 | RESERVED | |||||||

| AN9 | GND | |||||||

| AN10 | ETH_E_(R)(G)MII_RX_CLK | SOC.P32_7/GTIOC10_2B/GTIOC01_2B/SPI_SSL11/ENCIFOE11/DEE11/HDSL09_CLK1 | VDD33 | 3.3 | ETH_IOPWR | |||

| AN11 | GND | |||||||

| AN12 | LVDS_A_CLK_N | |||||||

| AP1 | ETH_D_(R)(G)MII_RX_CLK | SOC.P34_0/A22/GTADSM03_0/GTIOC03_0A/ETH3_RXCLK/SPI_MOSI2/ENCIFDO06/TXDE06/HDSL10_SMPL | VDD1833_3 | 1.8 | ETH_IOPWR | 1 | ||

| AP2 | GND | |||||||

| AP3 | ETH_E_(R)(G)MII_TXD2 | |||||||

| AP4 | ETH_E_(R)(G)MII_TXD3 | |||||||

| AP5 | GND | |||||||

| AP6 | ETH_E_(R)(G)MII_TX_EN(_EN) | |||||||

| AP7 | ETH_E_(R)MII_RX_ER | |||||||

| AP8 | GND | |||||||

| AP9 | ETH_E_SDP | |||||||

| AP10 | RESERVED | |||||||

| AP11 | LVDS_A_LANE3_N | |||||||

| AP12 | LVDS_A_LANE3_P | |||||||

| AR2 | ETH_E_(R)(G)MII_COL | SOC.P32_2/GTIOC10_0A/GTIOC01_0A/SPI_SSL03/ENCIFCK10/SCKE10/HDSL08_SEL2 | VDD33 | 3.3 | ETH_IOPWR | 1 | ||

| AR3 | ETH_E_(S)(R)(G)MII_TXD0 | SOC.P35_3/GTADSM08_0/SPI_SSL32/SPI_MOSI1/MCLK91/ADTRG0#/SI09#/HDSL11_CLK1 | VDD33 | 3.3 | ETH_IOPWR | 1 | ||

| AR4 | ETH_E_(S)(R)(G)MII_TXD1 | ETH_IOPWR | ||||||

| AR5 | ETH_E_(R)(G)MII_TX_CLK | ETH_IOPWR | ||||||

| AR6 | ETH_E_(S)(R)(G)MII_RXD0 | ETH_IOPWR | ||||||

| AR7 | ETH_E_(S)(R)(G)MII_RXD1 | ETH_IOPWR | ||||||

| AR8 | ETH_E_(R)(G)MII_RX_DV(_ER) | ETH_IOPWR | ||||||

| AR9 | ETH_E_(S)(R)(G)MII_RXD2 | ETH_IOPWR | ||||||

| AR10 | ETH_E_(S)(R)(G)MII_RXD3 | ETH_IOPWR | ||||||

| AM13 | GND | |||||||

| AM14 | LVDS_B_LANE3_N | SOC.AN200 | 0 – 1.8V | 1 | ||||

| AM15 | LVDS_B_LANE3_P | SOC.AN201 | 0 – 1.8V | 1 | ||||

| AM16 | GND | |||||||

| AM17 | LVDS_B_LANE2_N | SOC.AN103 | 0 – 1.8V | 1 | ||||

| AM18 | LVDS_B_LANE2_P | SOC.AN000 | 0 – 1.8V | 1 | ||||

| AM19 | GND | |||||||

| AM20 | LVDS_B_LANE0_N | SOC.P31_6/A16/TEND/POE11#/GMAC2_PTPTRG0/ETHSW_TDMAOUT0/ESC_LEDRUN/SPI_MISO0/MDAT32/ENCIFCK15/ENCIFCK01/SCKE11/SCKE01/HDSL08_SEL1 | VDD33 | 3.3 | 1 | |||

| AM21 | LVDS_B_LANE0_P | SOC.P31_7/GMAC2_PTPTRG1/SPI_SSL00/ENCIFOE15/ENCIFOE01/DEE11/DEE01/HDSL08_MISO1 | VDD33 | 3.3 | 1 | |||

| AM22 | GND | |||||||

| AM23 | RESERVED | |||||||

| AN13 | LVDS_A_CLK_P | |||||||

| AN14 | LVDS_VDD_EN | SOC.AN203 | 0 – 1.8V | 1 | ||||

| AN15 | GND | |||||||

| AN16 | LVDS_B_CLK_N | SOC.AN101 | 0 – 1.8V | 1 | ||||

| AN17 | LVDS_B_CLK_P | SOC.AN001 | 0 – 1.8V | 1 | ||||

| AN18 | GND | |||||||

| AN19 | LVDS_B_LANE1_N | SOC.P34_7/IRQ14/DREQ/GTADSM06_0/ETH3_TXER/ESC_RESETOUT#/SPI_MOSI3/TST_OUT08/HDSL10_MISO2 | VDD33 | 3.3 | 1 | |||

| AN20 | LVDS_B_LANE1_P | SOC.P35_4/GTADSM08_1/SPI_SSL33/SPI_SSL11/MDAT91/ADTRG1#/DUEI10/HDSL11_SEL1 | VDD33 | 3.3 | 1 | |||

| AN21 | GND | |||||||

| AN22 | LVDS_BL_PWM | SOC.P32_1/SPI_SSL02/ENCIFDI15/ENCIFDI01/RXDE11/RXDE01/HDSL08_CLK2 | VDD33 | 3.3 | 1 | |||

| AN23 | LVDS_BL_EN | SOC.P31_1/IRQ13/GTETRGSB/ETH2_RXER/SPI_SSL31/HDSL07_MISO2 | VDD1833_2 | 1.8 | 1 | |||

| AP13 | GND | |||||||

| AP14 | LVDS_A_LANE2_N | SOC.AN202 | 0 – 1.8V | 1 | ||||

| AP15 | LVDS_A_LANE2_P | SOC.AN102 | 0 – 1.8V | 1 | ||||

| AP16 | GND | |||||||

| AP17 | LVDS_A_LANE0_N | SOC.AN003 | 0 – 1.8V | 1 | ||||

| AP18 | LVDS_A_LANE0_P | SOC.AN002 | 0 – 1.8V | 1 | ||||

| AP19 | GND | |||||||

| AP20 | PCIe_D_HSO0_N | SOC.P31_2/POE0#/ETH2_TXER/SPI_SSL32/MCLK80/MDAT30/HSPI_IO4/ENCIFCK09/SCKE09/HDSL07_MOSI2/POUTA | VDD33 | 3.3 | 1 | |||

| AP21 | PCIe_D_HSO0_P | SOC.P32_0/SPI_SSL01/ENCIFDO15/ENCIFDO01/TXDE11/TXDE01/HDSL08_MOSI1 | VDD33 | 3.3 | 1 | |||

| AP22 | GND | |||||||

| AP23 | PCIe_D_HSO1_N | SOC.P30_7/IRQ14/ETHSW_PHYLINK2/ESC_PHYLINK2/SPI_MISO3/SD1_IOVS/MCLK30/SI07#/HDSL07_CLK2 | VDD1833_2 | 1.8 | 1 | |||

| AR14 | GND | |||||||

| AR15 | LVDS_A_LANE1_N | |||||||

| AR16 | LVDS_A_LANE1_P | SOC.AN100 | 0 – 1.8V | 1 | ||||

| AR17 | GND | |||||||

| AR18 | PCIe_D_HSI0_N | |||||||

| AR19 | PCIe_D_HSI0_P | |||||||

| AR20 | GND | |||||||

| AR21 | PCIe_D_HSI1_N | |||||||

| AR22 | PCIe_D_HSI1_P | |||||||

| AE32 | RESERVED | |||||||

| AE33 | PCIe_C_PERST# | |||||||

| AE34 | GND | |||||||

| AF32 | GPIO_E_0 | SOC.P22_0/IRQ11/HDSL01_SMPL | VDD1833_0 | 1.8 | 1.8 | |||

| AF33 | GPIO_E_1 | SOC.P17_4/A6/DREQ/GTADSM00_0/GTETRGB/CMTW1_TIC0/DE0/CANRX0/SD1_CD/DUEI07/HDSL13_MOSI2 | VDD33 | 3.3 | 1.8 | 1 | ||

| AF34 | PCIe_C_HSO3_P | SOC.P23_0/IRQ10/A17/GTIOC06_0B/ETH1_COL/ETHSW_TDMAOUT3/ESC_LINKACT1/CANTXDP1/SI15#/HDSL01_MOSI2 | VDD33 | 3.3 | 1 | |||

| AF35 | GND | |||||||

| AG32 | GPIO_E_2 | SOC.P26_5/IRQ12/CANTX0/ENCIFCK01/SCKE01/HDSL04_CLK1 | VDD1833_1 | 1.8 | 1.8 | |||

| AG33 | GPIO_E_3 | SOC.P21_6/ETHSW_PHYLINK0/ESC_PHYLINK0/CANRXDP1/HDSL00_MOSI2 | VDD1833_3 | 1.8 | ||||

| AG34 | PCIe_C_HSO3_N | SOC.P24_2/IRQ13/MDAT62/HDSL02_MOSI2 | VDD33 | 3.3 | 1 | |||

| AG35 | PCIe_C_HSI3_P | SOC.P23_1/GTIOC06_1A/ESC_IRQ/DUEI00/HDSL02_LINK | VDD33 | 3.3 | 1 | |||

| AH32 | GPIO_E_4 | SOC.P26_3/ETHSW_PHYLINK1/ESC_PHYLINK1/HDSL04_SMPL | VDD1833_1 | 1.8 | ||||

| AH33 | GPIO_E_5 | SOC.P29_0/CANTXDP0/MDAT72/ENCIFDI08/ENCIFDI00/RXDE08/RXDE00/HDSL06_SMPL | VDD33 | 3.3 | 1.8 | 1 | ||

| AH34 | GND | |||||||

| AH35 | PCIe_C_HSI3_N | SOC.P23_6/ETHSW_LPI0/MDAT60/SI01#/HDSL02_MOSI1 | VDD33 | 3.3 | 1 | |||

| AJ32 | GPIO_E_6 | SOC.P35_5/GTADSM09_0/RXD4/SCL4/MISO4/SPI_RSPCK1/MCLK92/TST_OUT10/HDSL11_MISO1 | VDD33 | 3.3 | 1.8 | 1 | ||

| AJ33 | GPIO_E_7 | SOC.P19_5/GTIOC07_2B/SI10#/HDSL15_CLK2 | VDD33 | 3.3 | 1.8 | 1 | ||

| AJ34 | PCIe_C_HSO2_P | SOC.P23_4/GTIOC06_2B/ESC_I2CDATA/IIC_SDA0/DUEI01/HDSL02_SEL1 | VDD33 | 3.3 | 1 | |||

| AJ35 | GND | |||||||

| AK32 | Vendor Defined | PSU_1V8_PG | ||||||

| AK33 | Vendor Defined | PSU_1V1_PG | ||||||

| AK34 | PCIe_C_HSO2_N | SOC.P23_5/ESC_LINKACT2/MCLK60/TST_OUT01/HDSL02_MISO1 | VDD33 | 3.3 | 1 | |||

| AK35 | PCIe_C_HSI2_P | SOC.P23_2/GTIOC06_1B/ESC_RESETOUT#/TST_OUT00/HDSL02_SMPL | VDD33 | 3.3 | 1 | |||

| AL32 | Vendor Defined | PSU_0V8_PG | ||||||

| AL33 | Vendor Defined | PSU_3V3_PG | ||||||

| AL34 | GND | |||||||

| AL35 | PCIe_C_HSI2_N | SOC.P23_3/GTIOC06_2A/ESC_I2CCLK/IIC_SCL0/SI00#/HDSL02_CLK1 | VDD33 | 3.3 | 1 | |||

| AM24 | RESERVED | |||||||

| AM25 | RESERVED | |||||||

| AM26 | RESERVED | |||||||

| AM27 | RESERVED | |||||||

| AM28 | RESERVED | |||||||

| AM29 | RESERVED | |||||||

| AM30 | RESERVED | |||||||

| AM31 | RESERVED | |||||||

| AM32 | Vendor Defined | SEQ.SCL | ||||||

| AM33 | Vendor Defined | SEQ.SDA | ||||||

| AM34 | PCIe_C_HSO1_P | |||||||

| AM35 | GND | |||||||

| AN24 | RESERVED | |||||||

| AN25 | RESERVED | |||||||

| AN26 | RESERVED | |||||||

| AN27 | RESERVED | |||||||

| AN28 | RESERVED | |||||||

| AN29 | RESERVED | |||||||

| AN30 | RESERVED | |||||||

| AN31 | RESERVED | |||||||

| AN32 | PCIe_D_PERST# | |||||||

| AN33 | GND | |||||||

| AN34 | PCIe_C_HSO1_N | SOC.P28_3/GTIOC08_2A/SPI_SSL11/TST_OUT06/HDSL05_CLK2 | VDD33 | 3.3 | 1 | |||

| AN35 | PCIe_C_HSI1_P | |||||||

| AP24 | PCIe_D_HSO1_P | |||||||

| AP25 | GND | |||||||

| AP26 | PCIe_D_HSI2_N | SOC.P28_7/CANRXDP0/MCLK72/ENCIFDO08/ENCIFDO00/TXDE08/TXDE00/HDSL06_LINK | VDD33 | 3.3 | 1 | |||

| AP27 | PCIe_D_HSI2_P | SOC.P22_7/IRQ9/A18/GTIOC06_0A/ETH1_CRS/ETHSW_TDMAOUT2/ESC_LINKACT0/CANRXDP1/TST_OUT15/HDSL01_MISO2 | VDD33 | 3.3 | 1 | |||

| AP28 | GND | |||||||

| AP29 | PCIe_D_HSI3_N | SOC.P28_0/IRQ5/GTIOC08_0B/ETHSW_TDMAOUT1/SPI_MOSI1/TST_OUT05/HDSL05_SEL1 | VDD33 | 3.3 | 1 | |||

| AP30 | PCIe_D_HSI3_P | SOC.P24_1/IRQ12/MCLK62/SI02#/HDSL02_MISO2 | VDD33 | 3.3 | 1 | |||

| AP31 | GND | |||||||

| AP32 | PCIe_C_HSI0_N | SOC.P27_7/IRQ4/GTIOC08_0A/ETHSW_TDMAOUT0/SPI_RSPCK1/DUEI05/HDSL05_CLK1 | VDD33 | 3.3 | 1 | |||

| AP33 | PCIe_C_HSI0_P | SOC.P22_1/GTETRGA/ETH0_TXER/TXD5/SDA5/MOSI5/CANTX0/HDSL01_CLK1 | VDD33 | 3.3 | 1 | |||

| AP34 | GND | |||||||

| AP35 | PCIe_C_HSI1_N | SOC.P26_6/SEI/CS2#/ETH1_TXER/ESC_RESETOUT#/CANRX0/ENCIFOE01/DEE01/HDSL04_SEL1 | VDD33 | 3.3 | 1 | |||

| AR26 | GND | |||||||

| AR27 | PCIe_D_HSO2_N | SOC.P27_2/IRQ3/GTIOC02_0B/GMAC1_PTPTRG0/ESC_LEDERR/CANTX1/SPI_RSPCK0/HSPI_IO0/HDSL04_SEL2 | VDD33 | 3.3 | 1 | |||

| AR28 | PCIe_D_HSO2_P | SOC.P27_6/MTIOC1B/GTIOC08_4B/GTIOC02_2B/HSPI_CK/ENCIFDI14/RXDE10/HDSL05_SMPL | VDD33 | 3.3 | 1 | |||

| AR29 | GND | |||||||

| AR30 | PCIe_D_HSO3_N | SOC.P27_3/MTIOC2A/GTIOC08_3A/GTIOC02_1A/GMAC1_PTPTRG1/SCK0/CANRXDP1/SPI_MOSI0/HSPI_IO1/ENCIFCK14/SCKE10/HDSL04_MISO2 | VDD33 | 3.3 | 1 | |||

| AR31 | PCIe_D_HSO3_P | SOC.P28_4/GTIOC08_2B/SPI_SSL12/SI06#/HDSL05_SEL2 | VDD33 | 3.3 | 1 | |||

| AR32 | GND | |||||||

| AR33 | PCIe_C_HSO0_N | |||||||

| AR34 | PCIe_C_HSO0_P | |||||||

Note: After a reset, the SoC configures its ports that support the muxing of alternative functions to general I/O in Hi-Z, with the exception of signals JTAG and RSTOUT#.

Note 1: After a reset, the SoC configures the signals P08_1 to P08_5 as JTAG (TMS, TDI, TDO and TCK) and RSTOUT#.

Power and reset[edit | edit source]

Power Supply Unit (PSU) and recommended power-up sequence[edit | edit source]

Implementing a correct power-up sequence for RZ/T2H Renesas processor is not a trivial task because several power rails are involved.

ZERO SOM simplifies this task by embedding all the needed circuitry, according to the OSM standard control signals.

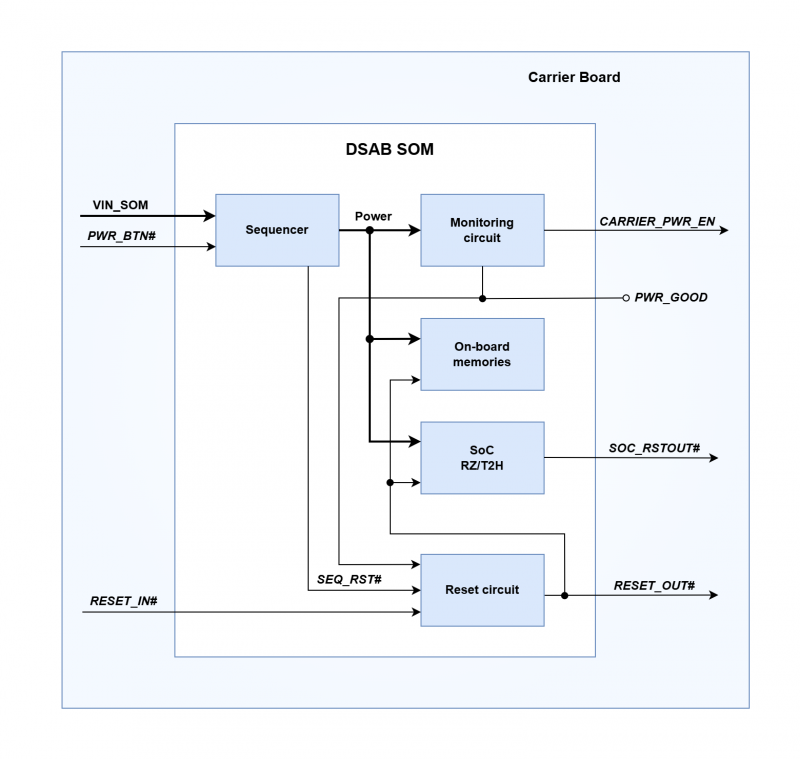

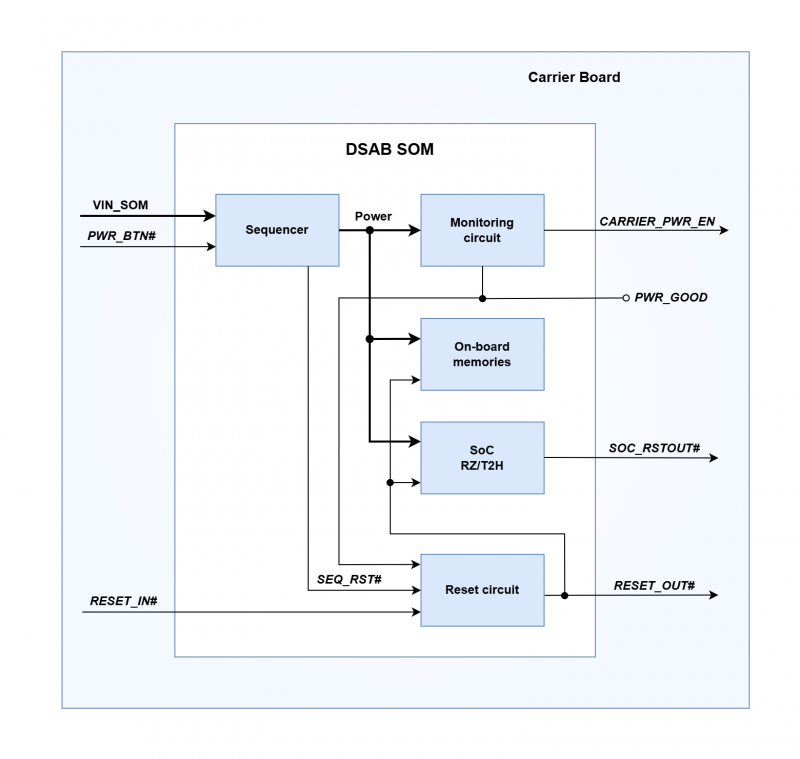

The following picture shows a simplified block diagram of PSU and voltage monitoring circuitry:

The PSU is composed of two main blocks:

- a sequencer, a device that generates the proper power-up/down sequence required by the SOC processor and surrounding memories

- some DC-DCs, that generate the different power rails of the SoM (3.3 V, 1.8 V 1.1 V and 0.8 V)

The monitoring circuit instead:

- monitors the different voltages generated by the DC-DCs

- synchronises the powering up/down of carrier board in order to prevent back power

Power-up sequence[edit | edit source]

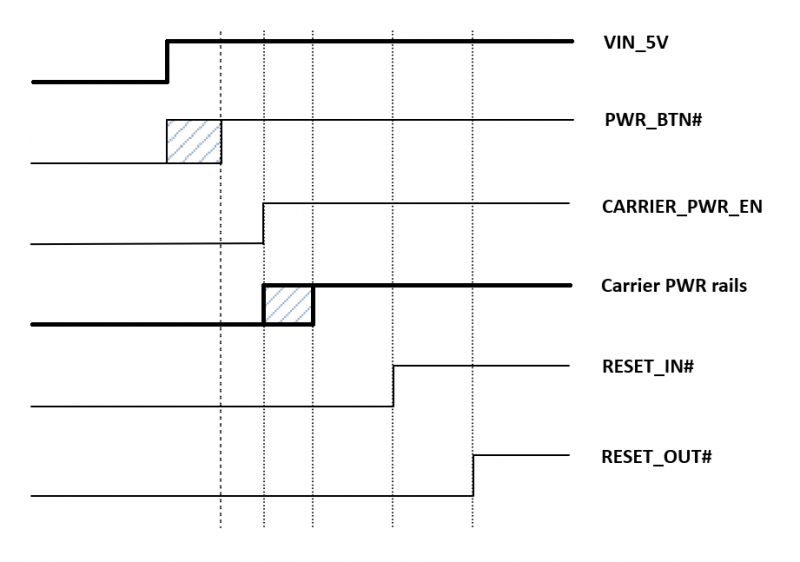

The picture below shows the recommended order to power up an OSM SoM, focuses especially on the control signals of the carrier board.

- The module will start up as soon as the VIN_5V input voltage is applied. However, the device can be power-on when the PWR_BTN# signal rise up.

- When the SoM rails are stable, the SoM monitor circuit raises the CARRIER_PWR_EN signal: use this signal to switch-on the rails on the carrier board.

- Release the RESET_IN# signal only when the rails on the carrier are stable.

- Then the SoM reset circuit releases the RESET_OUT# signal, which is internally propagated to the SoC and memories.Use this signal as a reset for carrier peripherals.

- The SoC generates the RSTOUT# signal when it exits reset: this signal is connected to ball P16 (use it for specific user case or as a monitor).

Additional notes[edit | edit source]

For more details on the reset circuit see Reset_scheme_and_control_signals section.

The OSM CARRIER_STBY# signal has not been implemented since no low-power operation modes have been foreseen for this SoM.

OSM contacts[edit | edit source]

The following table lists the contacts of ZERO SoM relating to the power circuit:

| OSM contact | OSM name | Purpose | Required |

|---|---|---|---|

| AE4, AF4, AG4, AH3,

AH4, AJ3, AJ4, AK4 |

VCC_IN_5V | Power input 5 V ±5 % | Yes |

| AE2, AE34, AF35, AG3, AH2, AH34,

AJ35, AK3, AL2, AL34, AM13, AM16, AM19, AM22, AM35, AN3, AN6, AN9, AN11, AN15, AN18, AN21, AN33, AP2, AP5, AP8, AP13, AP16, AP19, AP22, AP25, AP28, AP31, AP34, AR14, AR17, AR20, AR26, AR29, AR32 |

GND | Power input | Yes |

| AA9 | PWR_BTN# | Input open-drain 5 V, pull-up on SoM | |

| V17 | CARRIER_PWR_EN | Output CMOS 1.8 V | Yes |

| U17 | RESET_IN# | Input open-drain 1.8 V, pull-up on SoM | Yes |

| Y14 | RESET_OUT# | Output CMOS 1.8 V | Yes |

| P16 | SOC_RSTOUT# | Output CMOS 3.3 V | |

| AL33 | Vendor Defined | Output open-drain 5 V, 3.3 V power good | |

| C5 | VCC_6_TEST | Monitor 3.3 V rail | |

| AK32 | Vendor Defined | Output open-drain 5 V, 1.8 V power good | |

| Y16 | VCC_3_TEST | Monitor 1.8 V rail | |

| AK33 | Vendor Defined | Output open-drain 5 V, 1.1 V power good | |

| M19 | VCC_2_TEST | Monitor 1.1 V rail | |

| AL32 | Vendor Defined | Output open-drain 5 V, 0.8 V power good | |

| Y20 | VCC_4_TEST | Monitor 0.8 V rail |

Reset scheme and control signals[edit | edit source]

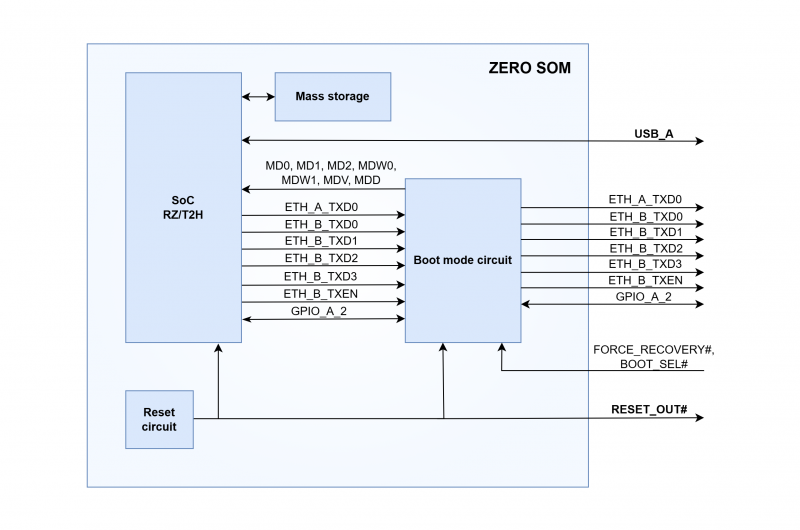

The following picture shows the simplified block diagram of reset scheme and voltage monitoring circuitry:

The reset sources are described below:

- External source:

- PWR_BTN# driven low for at least 150 ms causes a cold reset i.e. turns off all onboard SoM power rails and restarts a power-up sequence.

- RESET_IN# is the first of three warm reset sources: the RESET_OUT# warm reset signal (obtained as an AND of the three warm reset sources) is sent to the SoC, the memories on SoM and the carrier.

- Inside the SoM:

- SEQ_RST#, the second warm reset source, it is released when the power-on sequence is completed, after about 100 ms from the release of PWR_BTN#. This signal is not carried to the SoM contacts.

- PWR_GOOD, the third warm reset source, it is released when all PWR_GOOD of the four DC-DCs on SoM are valid. The signal is output on carrier as a monitor. In particular the SoM ANDs the different PWR_GOODs, condition that ensures all regulators on SoM are active and their output voltages within tolerances. It is possible to externally monitor the four voltage regulators individually: DAVE Embedded Systems' team is available for additional information by contact [[1]].

- Output signals:

- RESET_OUT# is obtained as an AND of the three warm reset sources; use this signal on carrier to reset the peripherals connected to the SoM. The SoM generates this signal, which is also sent internally to the SoC and memories.

- SOC_RSTOUT# is generated by the SoC: it remains low for 450 μs in the event of SoC input reset, software reset or SoC error reset. For more details see RZ/T2H user's manual ch.6.4.9 and ch.6.5.2. This signal is a warm reset because it does not propagate internally to the SoM and therefore does not cause a power cycle. For example, to force a cold reset when a software reset occurs, a circuit must be provided on the carrier board.

CARRIER_PWR_EN signal is used to synchronise the switching of the voltages on the carrier: see Power_Supply_Unit_(PSU)_and_recommended_power-up_sequence section.

I/O ports after reset[edit | edit source]

After a reset, the SoC configures its ports that support the muxing of alternative functions to general I/O as Hi-Z, with the exception of signals P08_1 to P08_5 that are set as JTAG (TMS, TDI, TDO and TCK) and RSTOUT#.

For more details see RZ/T2H user's manual ch.17.

OSM contacts[edit | edit source]

The following table lists the contacts of ZERO SoM relating to the power circuit:

| OSM contact | OSM name | Purpose | Required |

|---|---|---|---|

| AA9 | PWR_BTN# | Input open-drain 5 V, pull-up on SoM | |

| U17 | RESET_IN# | Input open-drain 1.8 V, pull-up on SoM | Yes |

| V17 | CARRIER_PWR_EN | Output CMOS 1.8 V | Yes |

| Y14 | RESET_OUT# | Output CMOS 1.8 V | Yes |

| P16 | SOC_RSTOUT# | Output CMOS 3.3 V | |

| AL33 | Vendor Defined | Output open-drain 5 V, PWR_GOOD (all DC-DCs) | |

| AL33 | Vendor Defined | Output open-drain 5 V, 3.3 V power good (optional) | |

| AK32 | Vendor Defined | Output open-drain 5 V, 1.8 V power good (optional) | |

| AK33 | Vendor Defined | Output open-drain 5 V, 1.1 V power good (optional) | |

| AL32 | Vendor Defined | Output open-drain 5 V, 0.8 V power good (optional) |

System boot[edit | edit source]

The boot process begins at SOM reset, where the hardware reset logic forces the ARM core to begin execution starting from the on-chip boot ROM. The boot ROM:

- determines whether the boot is secure or non-secure

- performs some initialization of the system and clean-ups

- reads the mode pins to determine the primary boot device

- once it is satisfied, it executes the boot code

Boot options[edit | edit source]

By default, ZERO SoM boots from on-board eMMC storage device. However, bringing low FORCE_RECOVERY# ball T17, Zero SOM boots from USB.

Other options are available on-demand, however, allowing implementation of different configurations. DAVE Embedded Systems' team is available for additional information on this matter. If necessary, please contact sales@dave.eu.

Boot modes[edit | edit source]

The OSM standard provides three contacts for configuring boot modes. The following table shows the preconfigured boot modes:

| Contact | OSM name | Contact | OSM name | Contact | OSM name | Boot mode | Peripheral / bus |

|---|---|---|---|---|---|---|---|

| T17 | FORCE_RECOVERY# | U19 | BOOT_SEL0# | R18 | BOOT_SEL1# | ||

| LOW | x | HIGH | USB boot | OSM USB_A | |||

| LOW | eMMC boot mode (3.3V) on SDHI0 | no standard OSM mapping | |||||

| HIGH | HIGH | HIGH | eSD boot mode (3.3V) on SDHI1 | eMMC on SoM | |||

| HIGH | LOW | xSPI0 boot mode (x8 boot serial flash) | no standard OSM mapping | ||||

| LOW | HIGH | xSPI1 boot mode (x1 boot serial flash) | no standard OSM mapping | ||||

| LOW | LOW | xSPI0 boot mode (x1 boot serial flash) | OSM SPI_A | ||||

Electrically these contacts are open drain inputs with 10 kΩ pull-up on SoM referred to 1.8 V.

In any case, the boot process is managed by on-chip boot ROM code which is described in detail in the processor's Reference Manual.

Note on boot signals[edit | edit source]

The boot mode is defined by the values of certain pins (MD0, MD1, MD2, MDW0, MDW1, MDV, MDD), sampled when the reset signal is deactivated.

After reset, the SoC uses these setting pins for other functionality, especially for ETH_A_TXD0, ETH_B_TXD0, ETH_B_TXD1, ETH_B_TXD2, ETH_B_TXD3, ETH_B_TXEN and GPIO_A_2 OSM signals.

To allow proper sampling of the bootstrap pins, the SoM circuitry sets the involved OSM signals into high impedance as long as signal RESET_OUT# (ball Y14) is low.

JTAG[edit | edit source]

JTAG signals are routed to the ZERO SOM contacts according to the OSM v1.2 standard. These signals output at 1.8 V logic, achieved with voltage translators on the SoM.

If needed, the reference voltage of 1.8 V is available at ball Y16 'VCC_3_TEST'.

The RZ SoC supports the boundary scan function: to enable it drive ball C18 'TEST_GENERIC' high.

JTAG signals[edit | edit source]

The following table reports the JTAG's signals available in the ZERO SOM contacts:

| OSM contact | OSM name | Notes |

|---|---|---|

| N17 | JTAG_TCK | Input CMOS 1.8 V |

| N19 | JTAG_TMS | Input CMOS 1.8 V |

| P17 | JTAG_TDI | Input CMOS 1.8 V |

| R17 | JTAG_TDO | Output CMOS 1.8 V |

| R19 | JTAG_nTRST | Input CMOS 1.8 V |

| Y16 | VCC_3_TEST | 1.8 V reference voltage |

Peripherals[edit | edit source]

Peripheral Ethernet[edit | edit source]

The Ethernet interfaces available on ZERO is based on RZ/T2H SoC and the Ethernet subsystem consists of Ethernet MAC (GMAC), Ethernet Switch (ETHSW), EtherCAT Slave Controller (ESC) and RGMII/RMII converters. The MAC-PHY interfaces support RGMII, MII, and RMII.

Description[edit | edit source]

- The Ethernet MAC (GMAC) has the following features

- 3 ports: GMAC0, GMAC1, GMAC2

- 10/100/1000-Mbit/s data transfer (10/100 full duplex or half duplex, 1000 full duplex)

- IEEE802.3, IEEE1588-2008 and IEEE802.3-az-2010 for EEE

- advanced IEEE 1588-2002 & 2008 Ethernet frame time-stamping

- TSN features (IEEE802.1Qbv, IEEE802.1Qbu/802.3br)

- VLAN Filtering, L3 and L4 Filtering

- The Ethernet switch (ETHSW) - IEEE802.3 - has

- 3-port PHY interfaces

- Full and half duplex (1000 Mbps supports full-duplex only)

- Hardware switching, lookup, and filtering

- QoS with frame prioritization

- Priority control based on VLAN Priority (IEEE802.1q)

- Multicasting and broadcasting

- VLAN frame

- IEEE 1588-2008 compatible

- Frame preemption

- Forwarding rule for the TSN-IA profile

- MAC source address filtering

- Independent two timer modules are available for timestamping and time for TDMA

- Ingress filtering and frame header manipulation (active stream identification, flow metering) with Enhanced Frame Parser

- Additional PTP timer pulse generators

- The EtherCAT slave controller (ESC) is based on an EtherCAT Slave Controller IP core (made by Beckhoff Automation GmbH)

- 1 channel (with 3 MII ports)

- MII interface is supported: RMII/RGMII interface is supported by RGMII converter

Important note for the external magnetic connection[edit | edit source]

The Ethernet peripherals require an external magnetic insulator on the carrier board.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral USB[edit | edit source]

The USB 2.0 host controller in the ZERO SOM conforms to Universal Serial Bus Specification Revision 2.0 and it is a dual-role device: host or device.

Description[edit | edit source]

The USB HS host/function module has the following features:

- OTG support

- Transfer rate: High speed (480 Mbps), full speed (12 Mbps), low speed (1.5 Mbps, host only)

- Communications buffer

- 1 KB of RAM for host mode

- 8 KB of RAM for device mode

- two DMAC channels

Peripheral PCIe[edit | edit source]

The PCI Express 3.0 Interface (PCIE) in the ZERO SOM can operate as a root complex or endpoint device.

Description[edit | edit source]

The PCIe module is compliant to the PCI Express Base Specification 3.1 and it has the following features:

- PCI Express Gen1 (2.5 [GT/s]) / Gen2 (5.0 [GT/s]) / Gen3 (8.0 [GT/s])

- Lane/Port: 1 lane × 2 ports (with common or separate reference clock) or 2 lanes × 1 port selectable

- Polarity inversion

- Maximum data payload of 256 bytes, Maximum read request size 512 bytes

- Number of outstanding 1-8

- Dynamic control of speed/width up/down configuration

- Power Management (not support ASPM L1-Substate)

- Error handling/logging (AER Support)

- Replay FIFO with ECC

- Module-stop state support to reduce power consumption

Peripheral SD[edit | edit source]

The SD/MMC host interface (SDHI) provides the features listed below.

Description[edit | edit source]

- SDIO card interface: 1-bit/4-bit

- SD, SDHC, and SDXC SD memory card access supported

- Default, high-speed, UHS-I/SDR12, SDR25, SDR50, SDR104, and DDR50 transfer modes

- Error check function: CRC7 (for command/response), CRC16 (for data)

- Card detect and Write protect supported

- MMC interface (1-/4-/8-bit MMC bus)

- e-MMC device access supported

- Backward-compatible, high-speed (SDR/DDR), and HS200 transfer modes supported

- High-priority interrupt (HPI) supported

Peripheral CAN[edit | edit source]

The CAN-FD module (CANFD) in the ZERO SOM is CAN-FD ISO 11898-1 (2015) compliant.

Description[edit | edit source]

The two CAN-FD channels have the following features:

- Communication speed

- Classical CAN mode: 1 Mbps

- CAN FD mode:

- Nominal bit rate: max. 1 Mbps

- Data bit rate: max. 8 Mbps

- Total 192 message buffers (when frame size is 76 bytes)

- Individual buffers: 64 for TX

- Shared buffers: 128 for TX and RX including FIFO

- Selectable ID type with 11-bit Standard and 18-bit Extended

- Selectable Frame type: Data Frame and Remote Frame

- Up to 256 receive rules

- Error status monitoring

- CAN protocol errors (stuff error, from error, ACK error, CRC error, bit error, ACK delimiter error, and bus dominant lock)

- Defects error status transitions (error warning, error passive, bus-off entry, and bus-off recovery)

- Reads the error counter

- Monitors DLC errors

- 8 interrupt sources

- 10 DMA requests

- clock source 40 or 80 MHz

Peripheral Serial[edit | edit source]

The RZ/T2H SoC provides a Serial Communication Interface (SCI) module in the ZERO SOM as asynchronous or synchronous serial interfaces.

Description[edit | edit source]

The SCI module has the following features:

- 6 channels: 5in NONSAFETY and one in SAFETY

- Asynchronous or 8-bit Clock synchronous

- Simple I2C (master-only)

- Simple SPI

- Smart card interface

- Manchester mode for encoder

- Bit rate specifiable with the on-chip baud rate generator

- Full-duplex and half-duplex communication

- Data length: 7 to 9 bits (Asynchronous mode)

- Bit rate modulation

- Double speed mode (Asynchronous, Clock Synchronous, Simple SPI mode, Manchester mode)

- RS-485 driver control function (Asynchronous mode)

- Loopback function to enable self-diagnosis (Asynchronous, Clock synchronous mode)

Peripheral I2C[edit | edit source]

The I2C Bus Interface (IIC) module in the ZERO SOM conforms and provides a subset of the NXP functionalities.

Description[edit | edit source]

The IIC module has the following features:

- 3 channels: two NONSAFETY and one SAFETY

- Communication formats: I2C bus format or SMBus format

- Master or slave mode selectable

- Supports the multi-master

- Maximum transfer rate: 400 kbps (Standard and Fast modes supported)

- Issuing and detecting conditions, Wait function, Arbitration (multi master), Timeout function

- Noise cancellation (Digital noise filters)

- Module-stop to reduce power consumption

Peripheral SPI[edit | edit source]

The Serial Peripheral Interface (SPI) module in the ZERO SOM provides 4 SPI channels.

Description[edit | edit source]

Each SPI channel has the following features:

- SPI transfer facility

- Using MOSI, MISO, SSL and RSPCK (SPI clock) signals enables SPI serial transfer (four lines) or clock-synchronous operation (three lines) capable of handling serial transfer as a master or slave

- Data formats

- Switching between MSB first and LSB first

- Transfer bit length selectable to 4 - 32 bits

- 32 bits × 4-stage FIFO transmit and receive buffers

- Up to four frames can be transmitted or received in a single transfer operation (with each frame having up to 32 bits)

- RSPCK can be stopped automatically when the reception buffer is full for master reception

Peripheral LCD[edit | edit source]

The LCD controller unit module in the ZERO SOM is provided by the LCD controller in the RZ/T2H SoC.

Description[edit | edit source]

The LCD controller unit has the following features:

- 2 planes blending (can blend 2 different size images)

- Support Image Processing:

- Dither processing (RGB666)

- Clipping

- RGB Gamma Correction LUT

- Input Data Format

- RGB565 / RGB666 / RGB888

- ARGB1555 / ARGB4444 / ARGB8888

- YcbCr444 8-bit / YcbCr422 8-bit / YcbCr420 8-bit

- Parallel Output Data Format: RGB666 / RGB888

- video resolution up to WXGA (1280 × 800) @ 60 fps

● DCLK / HSync / VSync /DE timing signal

Peripheral Timer[edit | edit source]

The RZ/T2H SoC in the ZERO SOM has a on-chip multi-function timer (MTU) pulse unit with a total of 9 channels:

- 8 channels x 16 bits

- 1 channel x 32 bits

Description[edit | edit source]

The MTU has:

- 28 pulse-input/output maximum and 3 pulse-input line

- 10, 11, 12, or 14 counter-input clock signals for each channel (with maximum operating frequency of 250 MHz)

- Input capture function and 39 output compare/input capture registers

- Counter clear operation (synchronous clearing by compare match/input capture)

- Simultaneous writing to multiple timer counters (TCNT)

- Simultaneous register input/output by synchronous counter operation

- Pulse output mode: toggle/PWM/complementary PWM/reset-synchronized PWM

- Complementary PWM output mode

- Outputs non-overlapping waveforms for controlling 3-phase inverters

- Automatic specification of dead times

- PWM duty cycle: Selectable as any value from 0% to 100%

- Delay can be applied to requests for A/D conversion

- Non-generation of interrupt requests at peak or trough values of counters can be selected

- Double buffer configuration

- Reset synchronous PWM mode: six phases of positive and negative PWM waveforms can be output with desired duty cycles

- Phase-counting mode: 16-bit mode (channels 1 and 2), 32-bit mode (channels 1 and 2 in cascade connection)

- Counter functionality for dead-time compensation

- Generation of triggers for A/D converter conversion: A/D converter start triggers can be skipped

- Digital noise filter function for signals on the input capture and external counter clock pins

Peripheral PWM[edit | edit source]

The RZ/T2H SoC in the ZERO SOM has a General PWM timer (GPT) subsystem that is a 32-bit timer with 56 channels divided into four groups with a total of 11 units:

- 5 channels × 9 units

- 7 channels × 1 unit

- 4 channels × 1 unit

Description[edit | edit source]

Each channel has:

- Counting up or down (saw-wave), counting up and down (triangle-wave)

- Select from among four counter-input clock signals

- 2 input/output pins

- 2 output compare/input capture registers

- in output compare operation, laterally asymmetric PWM waveforms can be generated

- Generation of dead times in PWM operation

- through combination of 3 counters, generation of automatic 3-phase PWM waveforms incorporating dead times

- Starting, clearing, stopping, switching, up/down counters, and input capture in response to external or internal triggers or input level comparison

- Generation of triggers for A/D converter conversion

- Digital noise filter function for signals on the input capture and external trigger pins

- Prescaler with 9 dividing clocks

- 9 sources interrupts