ONDA SOM/ONDA Evaluation Kit/pdf

Getting started[edit | edit source]

Kit Identification Codes[edit | edit source]

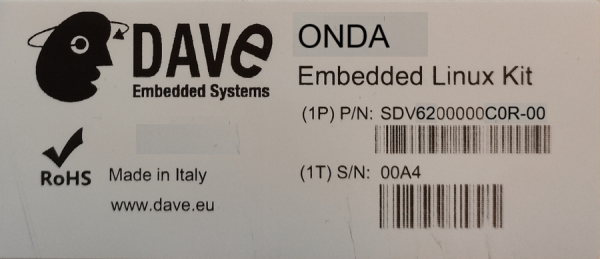

The development kits are identified by a couple of codes:

- P/N Part Number identification code

- S/N Serial Number identification code

These codes are printed on a label stuck to the box containing the kit.

As an example, the following picture shows such label with Serial Number 00A4

These codes are required to complete the registration process of the kit.

Unboxing[edit | edit source]

Once you've received the kit, please open the box and check the kit contents with the packing list included in the box, using the table on this chapter as a reference.

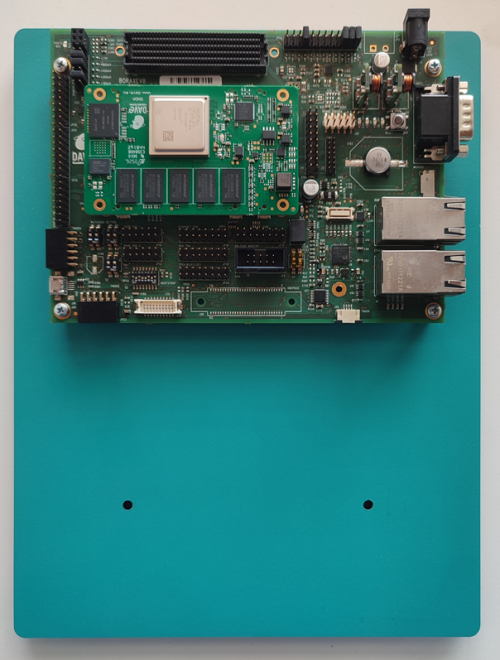

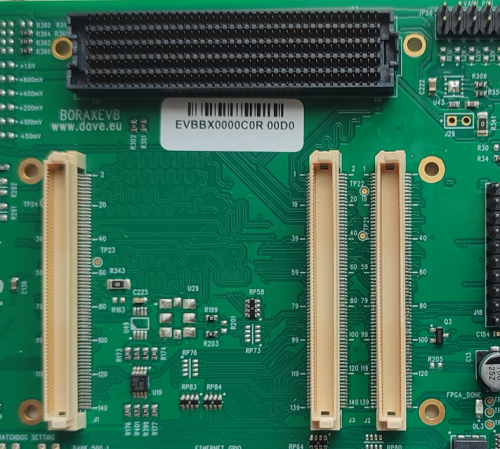

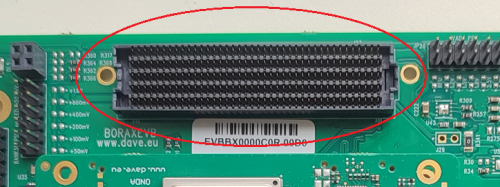

The hardware components (SOM, carrier boards and display) are pre-assembled, as shown in the picture below:

Kit Contents[edit | edit source]

The following table list the kit components:

| Component | Description | Notes |

|---|---|---|

| BORA Xpress carrier board with ONDA SOM | ||

| AC/DC Single Output Wall Mount adapter Output: +12V – 2.0 A |

||

| FTDI USB/RS232 cable adapter |

FTDI code: CHIPI-X10 | |

| D9 Female to D9 Female null modem cable | ||

| MicroSDHC card |

Order codes[edit | edit source]

| Order code | Description |

|---|---|

| SDV6200000C0R-00 | This code refers to the default configuration detailed above including SOM DNDA20000I1R |

microSD Layout[edit | edit source]

The microSD provided with the kit is used to store:

- a bootable partition (mmcblk0p1, vfat) containing:

- binary images (u-boot and kernel images)

- root file system partition (mmcblk0p2, ext4)

Connections[edit | edit source]

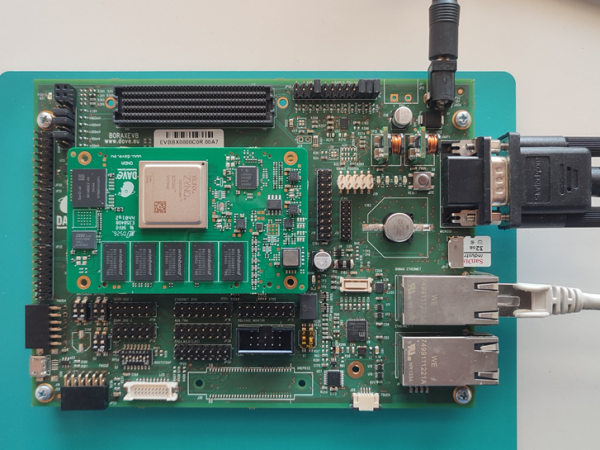

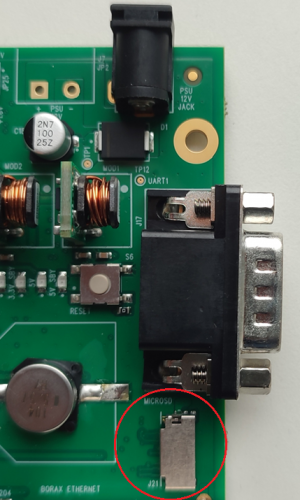

This section describes how to quick start the Evaluation Kit. The picture below shows the ONDA SOM inserted into the Evaluation Kit:

The system is programmed to automatically boot Linux at power up, loading the bootloader, the kernel and device tree image and the root file system from the SD card memory.

To connect to the system:

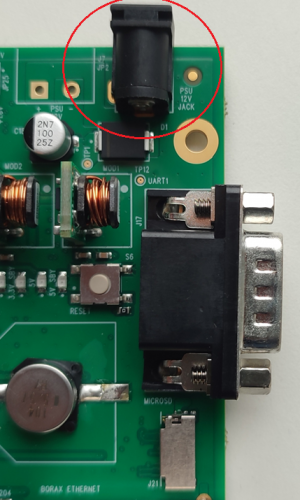

- connect the 12Vcc power supply to JP2 on the board

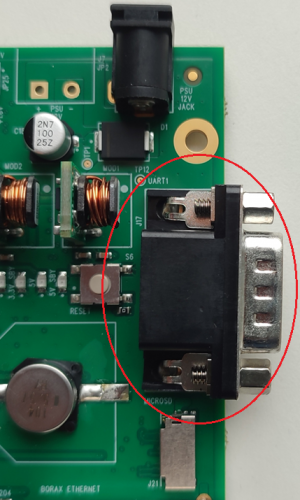

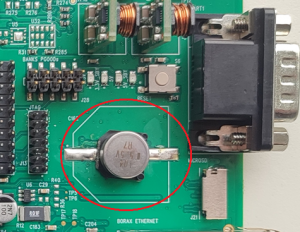

- connect the firts serial DB9 cable side to the J17 connector on the carrier board and connect the second DB9 side to the PC COM port

- start your favorite terminal emulator software on PC (eg: PuTTY, Minicom, ...); communication parameters are 115200,N,8,1

- (optional) connect the ethernet cable from your LAN hub/switch to the J8 RJ45 connector

- start SSH, using the following parameters:

- ip address: 192.168.1.1

- username: root

- empty password

- start SSH, using the following parameters:

First boot[edit | edit source]

Once power has been applied, U-Boot bootloader will be executed and the debug messages will be printed on the serial console. U-Boot automatically runs the autoboot macro, that loads the kernel/dtb and launches it with the options for mounting the root file system from the SD card.

At the end of the boot process, a demo application is launched and you can interact with the system using the touchscreen. The Linux shell is available on the serial console. Moreover, both telnet and ssh services are available to connect to the system through the network.

Serial console[edit | edit source]

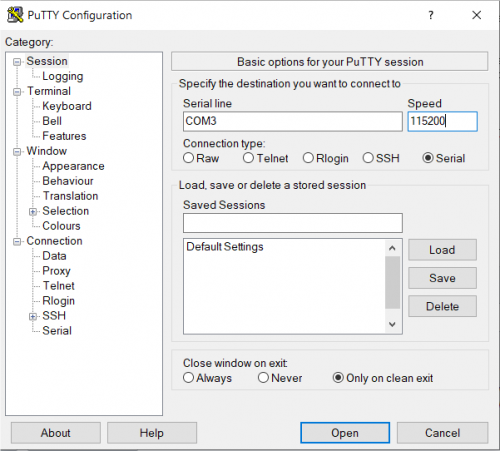

A simple Windows serial and SSH/telnet client and terminal can be downloaded from here.

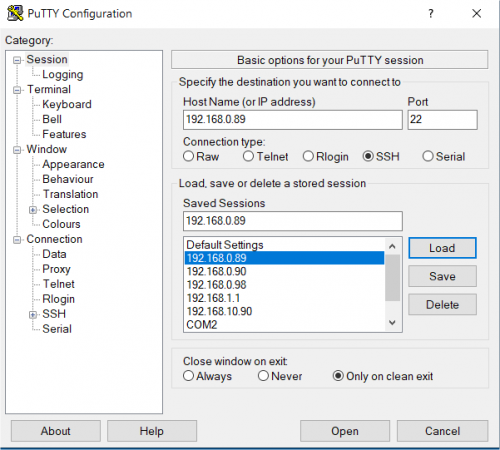

The following picture shows the serial setup for connecting to the EVK:

once selected the COM[x] serial port, click the Open button which starts the terminal. Once powered, the EVK shows the U-boot debug messages printed on the serial console.

Connecting through SSH[edit | edit source]

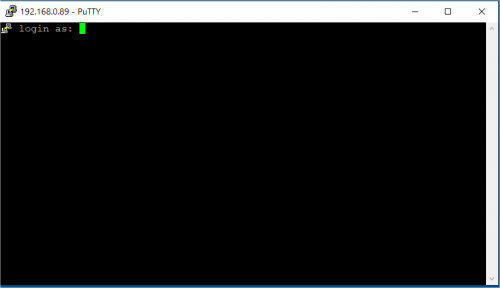

The following picture shows the SSH connection to the EVK:

once selected the IP address, click the Open button which starts the terminal. Once connected, the EVK shows the linux kernel prompt login for inserting the login:

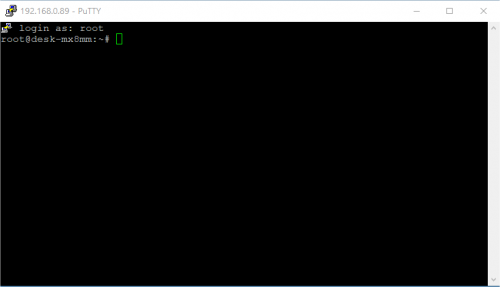

Then use the root login username without password:

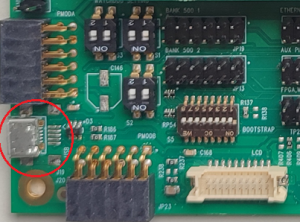

Boot Configurations[edit | edit source]

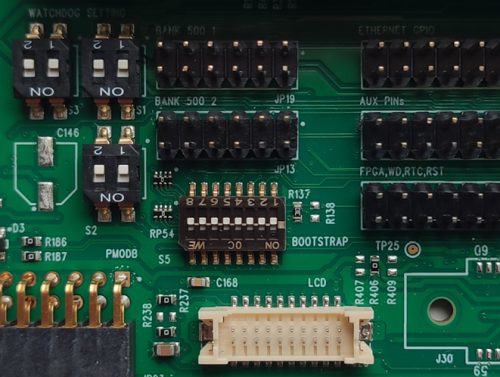

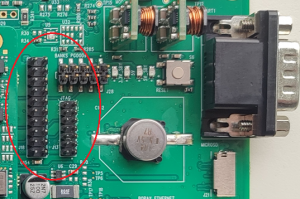

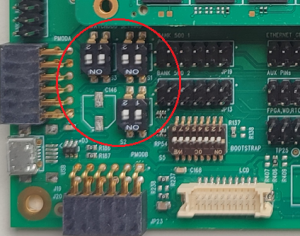

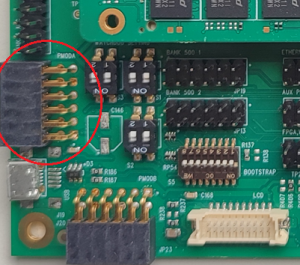

S5 is a dip-switch for the boot mode selection. Each signal can be kept High (dip switch OFF) or forced Low (dip switch ON).

The following table reports the available options and the related configurations:

| Boot peripheral | S5.1 | S5.2 | S5.3 | S5.4 | S5.5 | S5.6 | S5.7 | S5.8 |

|---|---|---|---|---|---|---|---|---|

| QSPI NOR | OFF | OFF | OFF | OFF | ON | OFF | ON | ON |

| SD | OFF | OFF | OFF | OFF | ON | ON | OFF | OFF |

| eMMC | OFF | OFF | OFF | OFF | OFF | ON | ON | OFF |

| JTAG | OFF | OFF | OFF | OFF | ON | ON | ON | ON |

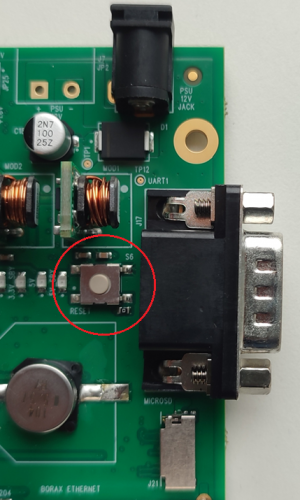

Reset button[edit | edit source]

S6 is the hardware reset button connected to the MRSTn signal (J2.116 SOM connector)

Carrier board Design[edit | edit source]

General Information[edit | edit source]

Product Highlights[edit | edit source]

The ONDA SOM Evaluation platform presented here provides a compact solution for any industry and can be easily interfaced with Digital signal Processing application, Plant Automation Control thanks to IEC-61131 SW language environment.

The following table summarizes the main hardware and software features available with ONDA SOM evaluation board:

Hardware[edit | edit source]

| Subsystem | Characteristics |

|---|---|

| CPU | Zynq Ultrascale+ 64-bit Dual/Quad Core Cortex-A53 with a Dual-core Arm Cortex-R5F and PL FPGA |

| SD | microSD boot device |

| USB | OTG |

| Serial Ports | RS232 CAN interface |

| Ethernet0 | EMAC 10/100/1000Mbps |

| Ethernet1 | EMAC 10/100/1000Mbps (routed through EMIO) |

| Espansion | GPIO connector Digilent Pmod™ Compatible connector |

| FMC | ANSI/VITA 57.1-2008 Mezzanine Card Connector |

| JTAG | JTAG and TRACE ports |

| PSU | 12 to 24V DC |

Software[edit | edit source]

| Subsystem | Options |

|---|---|

| Operating System | Linux |

| Distribution | Yocto, Petalinux |

Block Diagram and features[edit | edit source]

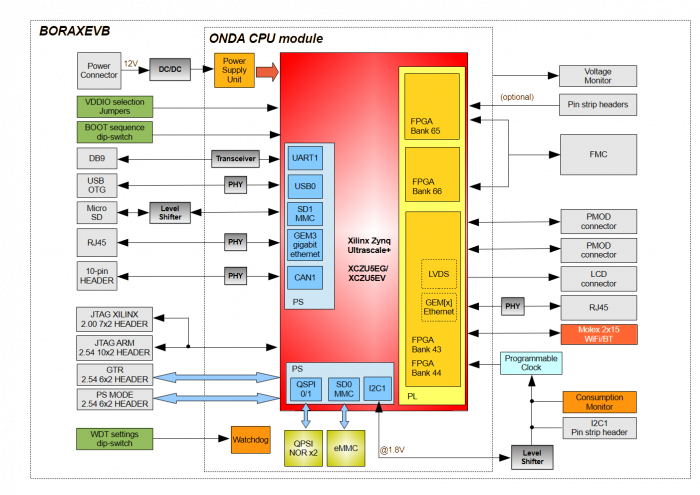

The following picture shows ONDA Evaluation Kit block diagram:

Configurable routing options[edit | edit source]

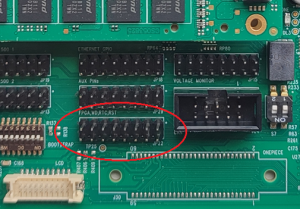

FPGA banks #43, #44, #65 and #66 supports different routing options as shown in the following picture:

For a detailed description of FMC connector routing, please refer to this page.

Features summary[edit | edit source]

- 10/100/1000 Ethernet #0 (PS)

- 10/100/1000 Ethernet #1 (routed through EMIO)

- 1x USB 2.0 OTG (MicroAB connector)

- 1x Serial port (RS232 DB9)

- 1x MicroSD slot

- 1x FPGA Mezzanine Card (FMC) Connector

- JTAG port

- Digilent Pmod™ Compatible expansion connectors

- 2.54mm-pitch pin-strip connectors for ONDA PS and PL configurable peripherals (MIO and EMIO interfaces, GPIOs, custom IPs, ..)

- Jumpers for voltage selection of the PL banks

- +12V power connector

Interfaces and Connectors[edit | edit source]

Power Supply[edit | edit source]

Power is provided through the JP2 connector.

JP2 connector is a standard 2.1mm/5.5mm DC power jack with positive center pin

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | VIN | Power supply | Nominal: +12V |

| 2 , 3 | DGND | Ground | - |

Voltage selections[edit | edit source]

CPU connector[edit | edit source]

The pinout of the J1, J2 and J3 connectors of the ONDA Evaluation Kit are the same of the counterpart connectors on ONDA SOM.

JTAG[edit | edit source]

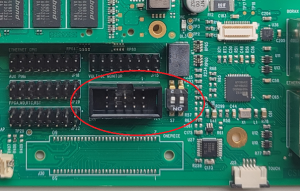

JTAG port is available as two different mechanical connectors:

- 2.00mm-pitch 7x2 header (Xilinx standard)

- 2.54mm-pitch 10x2 header ARM standard

- This port is connected to Zynq's native JTAG signals. Please note that Zynq's internal JTAG chain supports differents configurations, depending on bootstrap signals. In case split mode is selected, CPU JTAG can be routed separately via PL. For more details please refer to Zynq Technical Reference Manual.

- JTAG on ONDA Evaluation Kit is also connected to the FMC connector. For more details on how to connect JTAG on a custom FMC card please refer to ANSI/VITA FPGA Mezzanine Card (FMC) Standard.

JTAG XILINX[edit | edit source]

J13 is a 14-pin 7x2x2 pitch vertical header. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1, 3, 5, 7, 9, 11, 13 | DGND | - | - |

| 2 | 3.3V | - | - |

| 4 | JTAG_TMS | - | - |

| 6 | JTAG_TCK | - | - |

| 8 | JTAG_TDO | - | - |

| 10 | JTAG_TDI | - | - |

| 12 | N.C. | - | - |

| 14 | JTAG_TRSTn | - | - |

JTAG ARM[edit | edit source]

J18 is a 20-pin 10x2x2.54 pitch vertical header. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | 3.3V | - | - |

| 2 | 3.3V | - | - |

| 3, 11, 17, 19 | N.C. | - | - |

| 4, 6 ,8 ,10 ,12, 14, 16, 18, 20 |

DGND | - | - |

| 5 | JTAG_TDI | - | - |

| 7 | JTAG_TMS | - | - |

| 9 | JTAG_TCK | - | - |

| 13 | JTAG_TDO | - | - |

| 15 | JTAG_TRSTn | - | - |

Ethernet[edit | edit source]

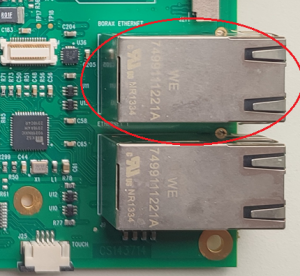

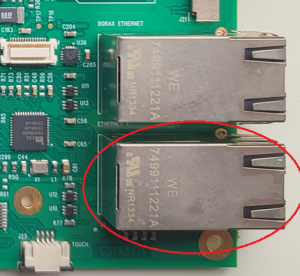

ONDA Evaluation Kit has two ethernet ports.

ETH0[edit | edit source]

J8 is a RJ45 Gigabit Ethernet connector - incorporating magnetics - connected to the ONDA integrated ethernet controller and PHY.

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | CT_TRD3 | center tap TRD3 | - |

| 2 | ETH_TXRX2_M | - | - |

| 3 | ETH_TXRX2_P | - | - |

| 4 | ETH_TXRX1_P | - | - |

| 5 | ETH_TXRX1_M | - | - |

| 6 | CT_TRD2 | center tap TRD2 | - |

| 7 | CT_TRD4 | center tap TRD4 | - |

| 8 | ETH_TXRX3_P | - | - |

| 9 | ETH_TXRX3_M | - | - |

| 10 | ETH_TXRX0_M | - | - |

| 11 | ETH_TXRX0_P | - | - |

| 12 | CT_TRD1 | center tap TRD1 | - |

| 13 | 3.3V_ETH0_LED2 | - | - |

| 15 | 3.3V_ETH0_LED1 | - | - |

| 14, 16 | +3.3V | - | - |

ETH1[edit | edit source]

J9 is a RJ45 Gigabit Ethernet connector - incorporating magnetics - connected to Micrel KSZ9031 PHY (Gigabit Ethernet Transceiver). This, in turn, is connected to PL's bank 13 via RGMII interface. This is an example of EMIO routing showing how to route PS's MAC signals via PL subsystem.

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | CT_TRD3 | center tap TRD3 | - |

| 2 | ETH1_TXRX2_M | - | - |

| 3 | ETH1_TXRX2_P | - | - |

| 4 | ETH1_TXRX1_P | - | - |

| 5 | ETH1_TXRX1_M | - | - |

| 6 | CT_TRD2 | center tap TRD2 | - |

| 7 | CT_TRD4 | center tap TRD4 | - |

| 8 | ETH1_TXRX3_P | - | - |

| 9 | ETH1_TXRX3_M | - | - |

| 10 | ETH1_TXRX0_M | - | - |

| 11 | ETH1_TXRX0_P | - | - |

| 12 | CT_TRD1 | center tap TRD1 | - |

| 13 | 3.3V_ETH1_LED2 | - | - |

| 15 | 3.3V_ETH1_LED1 | - | - |

| 14, 16 | +3.3V | - | - |

Console[edit | edit source]

J17 is a standard DB9 connector that routes the signals coming from the RS232 transceiver that is connected to the PS MIO signals of the UART1 port.

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1, 6, 4, 9 | N.C. | N.C. | |

| 2 | UART_EXT_RX | Receive line | Connected to protection diode array |

| 3 | UART_EXT_TX | Transmit line | Connected to protection diode array |

| 5 | DGND | Ground | |

| 7, 8 | N.C. | N.C. | Connected to protection diode array |

Micro SD[edit | edit source]

J21 is a microSD memory card connector. It is connected to the ONDA SOM through a bidirectional 1.8V/3.3V voltage-level translator mounted on the ONDA Evaluation Kit. Level shifter is required because MIO signals are 1.8V. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | PS_SD0_DAT2 | - | - |

| 2 | PS_SD0_DAT3 | - | - |

| 3 | PS_SD0_CMD | - | - |

| 4 | 3.3V | - | - |

| 5 | PS_SD0_CLK | - | - |

| 6, 9, 10, 11, 12 | DGND | - | - |

| 7 | PS_SD0_DAT0 | - | - |

| 8 | PS_SD0_DAT1 | - | - |

| 3.3V | - | Pull up to 3V3 with 10K Ohm |

USB[edit | edit source]

J19 is a standard USB Micro AB connector. It is connected to the ONDA USB 2.0 OTG peripheral and it works in OTG mode. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | USB_OTG_VBUS | - | - |

| 2 | USBM1 | - | - |

| 3 | USBP1 | - | - |

| 4 | OTG_ID | - | - |

| 5 | USB_OTG_DGND | - | - |

| 6, 7, 8, 9 | USB_OTG_SHIELD | - | - |

CAN[edit | edit source]

J24 is a 10-pin 5x2x2.54mm pitch vertical header directly connected to ONDA SoM's transceiver for the CAN interface. This 2.5mm-pitch header is compatible with commonly available IDC-10/DB9 flat cables.

The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1, 6, 7, 8, 9, 10 |

N.C. | - | - |

| 2, 5 | CAN_SHIELD | - | - |

| 3 | CAN_L | - | - |

| 4 | CAN_H | - | - |

The S7 switch enables the insertion of a 120 ohm CAN termination resistor at the transmitter side.

RTC[edit | edit source]

JP22 is a 16-pin 8x2x2.54 pitch vertical header. The following table reports the RTC signal in the connector:

The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 7, 8 | GND | - | - |

| 2 | RTC_32KHz | - | - |

| 4 | RTC_RST | - | - |

| 6 | RTC_INT/SQW | - | - |

RTC_VBAT signal is connected to a 0.1F supercap for a short period data retention (evaluation purposes):

Watchdog[edit | edit source]

S1, S2 and S3 are dip-switch to override the default watchdog settings (startup delay and timeout) of the ONDA module watchdog.

For more details, please refer to this page.

| WD_SET0 | S1.1 | S1.2 |

|---|---|---|

| SOM default | OFF | OFF |

| '1' | ON | OFF |

| '0' | OFF | ON |

| WD_SET1 | S2.1 | S2.2 |

|---|---|---|

| SOM default | OFF | OFF |

| '1' | ON | OFF |

| '0' | OFF | ON |

| WD_SET2 | S3.1 | S3.2 |

|---|---|---|

| SOM default | OFF | OFF |

| '1' | ON | OFF |

| '0' | OFF | ON |

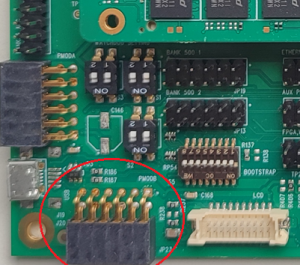

Digilent Pmod™[edit | edit source]

Please note that:

- Digilent Pmod™ Interface Specification - defined by Digilent Inc. - allows to quickly connect several pre-built I/O modules to PL.

- Analog Devices PMOD FPGA modules

PMOD-A[edit | edit source]

JP17 is a 12-pin 6x2x2.54 pitch vertical header. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | PMOD_A0 | - | |

| 2 | PMOD_A4 | - | |

| 3 | PMOD_A1 | - | |

| 4 | PMOD_A5 | - | |

| 5 | PMOD_A2 | - | |

| 6 | PMOD_A6 | - | |

| 7 | PMOD_A3 | - | |

| 8 | PMOD_A7 | - | |

| 9, 10 | DGND | Ground | - |

| 11, 12 | 3.3V | - |

PMOD-B[edit | edit source]

JP23 is a 12-pin 6x2x2.54 pitch vertical header. The following table reports the pinout of the connector:

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| 1 | PMOD_B0 | - | - |

| 2 | PMOD_B4 | - | - |

| 3 | PMOD_B1 | - | - |

| 4 | PMOD_B5 | - | - |

| 5 | PMOD_B2 | - | - |

| 6 | PMOD_B6 | - | - |

| 7 | PMOD_B3 | - | - |

| 8 | PMOD_B7 | - | - |

| 9, 10 | DGND | Ground | - |

| 11, 12 | 3.3V | - | - |

FMC[edit | edit source]

J27 is a 400 pins ANSI/VITA 57.1-2008 FPGA Mezzanine Card Connector that allows to connect to standard I/O mezzanine cards.

Please note that the ONDA Evaluation Kit FMC Connector is:

- fully compliant to FMC LPC

- partially compliant to FMC HPC because HPC side is not fully populated.

The following tables detail how ONDA signals have been routed to FMC connector.

For more information about I/O voltage of single-ended signals available on FMC connector, please refer to this section.

HPC Row A[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| A1 | DGND | GND | |

| A2 | GT_RX1_224_P | DP1_M2C_P | |

| A3 | GT_RX1_224_N | DP1_M2C_N | |

| A4 | DGND | GND | |

| A5 | DGND | GND | |

| A6 | GT_RX2_224_P | DP2_M2C_P | |

| A7 | GT_RX2_224_N | DP2_M2C_N | |

| A8 | DGND | GND | |

| A9 | DGND | GND | |

| A10 | GT_RX3_224_P | DP3_M2C_P | |

| A11 | GT_RX3_224_N | DP3_M2C_N | |

| A12 | DGND | GND | |

| A13 | DGND | GND | |

| A14 | not connected | DP4_M2C_P | |

| A15 | not connected | DP4_M2C_N | |

| A16 | DGND | GND | |

| A17 | DGND | GND | |

| A18 | not connected | DP5_M2C_P | |

| A19 | not connected | DP5_M2C_N | |

| A20 | DGND | GND | |

| A21 | DGND | GND | |

| A22 | GT_TX1_224_P | DP1_C2M_P | |

| A23 | GT_TX1_224_N | DP1_C2M_N | |

| A24 | DGND | GND | |

| A25 | DGND | GND | |

| A26 | GT_TX2_224_P | DP2_C2M_P | |

| A27 | GT_TX2_224_N | DP2_C2M_N | |

| A28 | DGND | GND | |

| A29 | DGND | GND | |

| A30 | GT_TX3_224_P | DP3_C2M_P | |

| A31 | GT_TX3_224_N | DP3_C2M_N | |

| A32 | DGND | GND | |

| A33 | DGND | GND | |

| A34 | not connected | DP4_C2M_P | |

| A35 | not connected | DP4_C2M_N | |

| A36 | DGND | GND | |

| A37 | DGND | GND | |

| A38 | not connected | DP5_C2M_P | |

| A39 | not connected | DP5_C2M_N | |

| A40 | DGND | GND |

HPC Row B[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| B1 | RSVD | RES1 | |

| B2 | DGND | GND | |

| B3 | DGND | GND | |

| B4 | not connected | DP9_M2C_P | |

| B5 | not connected | DP9_M2C_N | |

| B6 | DGND | GND | |

| B7 | DGND | GND | |

| B8 | not connected | DP8_M2C_P | |

| B9 | not connected | DP8_M2C_N | |

| B10 | DGND | GND | |

| B11 | DGND | GND | |

| B12 | not connected | DP7_M2C_P | |

| B13 | not connected | DP7_M2C_N | |

| B14 | DGND | GND | |

| B15 | DGND | GND | |

| B16 | not connected | DP6_M2C_P | |

| B17 | not connected | DP6_M2C_N | |

| B18 | DGND | GND | |

| B19 | DGND | GND | |

| B20 | GT_REFCLK1_224_P | GBTCLK1_M2C_P | |

| B21 | GT_REFCLK1_224_N | GBTCLK1_M2C_N | |

| B22 | DGND | GND | |

| B23 | DGND | GND | |

| B24 | not connected | DP9_C2M_P | |

| B25 | not connected | DP9_C2M_N | |

| B26 | DGND | GND | |

| B27 | DGND | GND | |

| B28 | not connected | DP8_C2M_P | |

| B29 | not connected | DP8_C2M_N | |

| B30 | DGND | GND | |

| B31 | DGND | GND | |

| B32 | not connected | DP7_C2M_P | |

| B33 | not connected | DP7_C2M_N | |

| B34 | DGND | GND | |

| B35 | DGND | GND | |

| B36 | not connected | DP6_C2M_P | |

| B37 | not connected | DP6_C2M_N | |

| B38 | DGND | GND | |

| B39 | DGND | GND | |

| B40 | RSVD | RES0 |

LPC Row C[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| C1 | DGND | GND | |

| C2 | GT_TX0_224_P | DP0_C2M_P | |

| C3 | GT_TX0_224_N | DP0_C2M_N | |

| C4 | DGND | GND | |

| C5 | DGND | GND | |

| C6 | GT_RX0_224_P | DP0_M2C_P | |

| C7 | GT_RX0_224_N | DP0_M2C_N | |

| C8 | DGND | GND | |

| C9 | DGND | GND | |

| C10 | IO_L23P_T3U_N8_66 | LA06_P | |

| C11 | IO_L23N_T3U_N8_66 | LA06_N | |

| C12 | DGND | GND | |

| C13 | DGND | GND | |

| C14 | IO_L2P_T0L_N2_66 | LA10_P | |

| C15 | IO_L2N_T0L_N2_66 | LA10_N | |

| C16 | DGND | GND | |

| C17 | DGND | GND | |

| C18 | IO_L1P_T0L_N0_DBC_66 | LA14_P | |

| C19 | IO_L1N_T0L_N1_DBC_66 | LA14_N | |

| C20 | DGND | GND | |

| C21 | DGND | GND | |

| C22 | IO_L16P_T2U_N6_QBC_AD3P_66 | LA18_P_CC | |

| C23 | IO_L16N_T2U_N7_QBC_AD3N_66 | LA18_N_CC | |

| C24 | DGND | GND | |

| C25 | DGND | GND | |

| C26 | IO_L6P_T0U_N10_AD6P_65 | LA27_P | |

| C27 | IO_L6N_T0U_N11_AD6N_65 | LA27_N | |

| C28 | DGND | GND | |

| C29 | DGND | GND | |

| C30 | I2C0_SCL | SCL | |

| C31 | I2C0_SDA | SDA | |

| C32 | DGND | GND | |

| C33 | DGND | GND | |

| C34 | GA0 | GA0 | |

| C35 | FMC_12P0V | 12P0V | |

| C36 | DGND | GND | |

| C37 | FMC_12P0V | 12P0V | |

| C38 | DGND | GND | |

| C39 | FMC_3P3V | 3P3V | |

| C40 | DGND | GND |

LPC Row D[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| D1 | IO_T1U_N12_66 | PG_C2M | |

| D2 | DGND | GND | |

| D3 | DGND | GND | |

| D4 | MGTREFCLK0P | GBTCLK0_M2C_P | |

| D5 | MGTREFCLK0N | GBTCLK0_M2C_N | |

| D6 | DGND | GND | |

| D7 | DGND | GND | |

| D8 | IO_L14P_T2L_N2_GC_66 | LA01_P_CC | |

| D9 | IO_L14N_T2L_N3_GC_66 | LA01_N_CC | |

| D10 | DGND | GND | |

| D11 | IO_L9P_T1L_N4_AD12P_66 | LA05_P | |

| D12 | IO_L9N_T1L_N5_AD12N_66 | LA05_N | |

| D13 | DGND | GND | |

| D14 | IO_L6P_T0U_N10_AD6P_66 | LA09_P | |

| D15 | IO_L6N_T0U_N11_AD6N_66 | LA09_N | |

| D16 | DGND | GND | |

| D17 | IO_L20P_T3L_N2_AD1P_66 | LA13_P | |

| D18 | IO_L20N_T3L_N3_AD1N_66 | LA13_N | |

| D19 | DGND | GND | |

| D20 | IO_L15P_T2L_N4_AD11P_66 | LA17_P_CC | |

| D21 | IO_L15N_T2L_N5_AD11N_66 | LA17_N_CC | |

| D22 | DGND | GND | |

| D23 | IO_L2P_T0L_N2_65 | LA23_P | |

| D24 | IO_L2N_T0L_N3_65 | LA23_N | |

| D25 | DGND | GND | |

| D26 | IO_L5P_T0U_N8_AD14P_65 | LA26_P | |

| D27 | IO_L5N_T0U_N9_AD14N_65 | LA26_N | |

| D28 | DGND | GND | |

| D29 | JTAG_TCK | TCK | |

| D30 | JTAG_TDI | TDI | |

| D31 | FMC_TDO_ZYNQ_TDI | TDO | |

| D32 | FMC_3P3VAUX | 3P3VAUX | |

| D33 | JTAG_TMS | TMS | |

| D34 | JTAG_TRSTn | TRST_L | |

| D35 | GA0 | GA1 | |

| D36 | FMC_3P3V | 3P3V | |

| D37 | DGND | GND | |

| D38 | FMC_3P3V | 3P3V | |

| D39 | DGND | GND | |

| D40 | FMC_3P3V | 3P3V |

HPC Row E[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| E1 | DGND | GND | |

| E2 | IO_L14P_T2L_N2_GC_65 | HA01_P_CC | |

| E3 | IO_L14N_T2L_N3_GC_65 | HA01_N_CC | |

| E4 | DGND | GND | |

| E5 | DGND | GND | |

| E6 | IO_L20P_T3L_N2_AD1P_65 | HA05_P | |

| E7 | IO_L20N_T3L_N3_AD1N_65 | HA05_N | |

| E8 | DGND | GND | |

| E9 | IO_L24P_T3U_N10_PERSTN1_I2C_SDA_65 | HA09_P | |

| E10 | IO_L24N_T3U_N11_PERSTN0_65 | HA09_N | |

| E11 | DGND | GND | |

| E12 | not connected | HA13_P | |

| E13 | not connected | HA13_N | |

| E14 | DGND | GND | |

| E15 | not connected | HA16_P | |

| E16 | not connected | HA16_N | |

| E17 | DGND | GND | |

| E18 | not connected | HA20_P | |

| E19 | not connected | HA20_N | |

| E20 | DGND | GND | |

| E21 | not connected | HB03_P | |

| E22 | not connected | HB03_N | |

| E23 | DGND | GND | |

| E24 | not connected | HB05_P | |

| E25 | not connected | HB05_N | |

| E26 | DGND | GND | |

| E27 | not connected | HB09_P | |

| E28 | not connected | HB09_N | |

| E29 | DGND | GND | |

| E30 | not connected | HB13_P | |

| E31 | not connected | HB13_N | |

| E32 | DGND | GND | |

| E33 | not connected | HB19_P | |

| E34 | not connected | HB19_N | |

| E35 | DGND | GND | |

| E36 | not connected | HB21_P | |

| E37 | not connected | HB21_N | |

| E38 | DGND | GND | |

| E39 | FMC_VADJ | VADJ | |

| E40 | DGND | GND |

HPC Row F[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| F1 | VREF_65 | PG_M2C | |

| F2 | DGND | GND | |

| F3 | DGND | GND | |

| F4 | IO_L13P_T2L_N0_GC_QBC_65 | HA00_P_CC | |

| F5 | IO_L13N_T2L_N1_GC_QBC_65 | HA00_N_CC | |

| F6 | DGND | GND | |

| F7 | IO_L19P_T3L_N0_DBC_AD9P_65 | HA04_P | |

| F8 | IO_L19N_T3L_N1_DBC_AD9N_65 | HA04_N | |

| F9 | DGND | GND | |

| F10 | IO_L23P_T3U_N8_I2C_SCLK_65 | HA08_P | |

| F11 | IO_L23N_T3U_N9_65 | HA08_N | |

| F12 | DGND | GND | |

| F13 | not connected | HA12_P | |

| F14 | not connected | HA12_N | |

| F15 | DGND | GND | |

| F16 | not connected | HA15_P | |

| F17 | not connected | HA15_N | |

| F18 | DGND | GND | |

| F19 | not connected | HA19_P | |

| F20 | not connected | HA19_N | |

| F21 | DGND | GND | |

| F22 | not connected | HB02_P | |

| F23 | not connected | HB02_N | |

| F24 | DGND | GND | |

| F25 | not connected | HB04_P | |

| F26 | not connected | HB04_N | |

| F27 | DGND | GND | |

| F28 | not connected | HB08_P | |

| F29 | not connected | HB08_N | |

| F30 | DGND | GND | |

| F31 | not connected | HB12_P | |

| F32 | not connected | HB12_N | |

| F33 | DGND | GND | |

| F34 | not connected | HB16_P | |

| F35 | not connected | HB16_N | |

| F36 | DGND | GND | |

| F37 | not connected | HB20_P | |

| F38 | not connected | HB20_N | |

| F39 | DGND | GND | |

| F40 | FMC_VADJ | VADJ |

LPC Row G[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| G1 | DGND | GND | |

| G2 | IO_L11P_T1U_N8_GC_66 | CLK0_C2M_P | |

| G3 | IO_L11N_T1U_N9_GC_66 | CLK0_C2M_N | |

| G4 | DGND | GND | |

| G5 | DGND | GND | |

| G6 | IO_L13P_T2L_N0_GC_QBC_66 | LA00_P_CC | |

| G7 | IO_L13N_T2L_N1_GC_QBC_66 | LA00_N_CC | |

| G8 | DGND | GND | |

| G9 | IO_L4P_T0U_N6_DBC_AD7P_66 | LA03_P | |

| G10 | IO_L4N_T0U_N7_DBC_AD7N_66 | LA03_N | |

| G11 | DGND | GND | |

| G12 | IO_L3P_T0L_N4_AD15P_66 | LA08_P | |

| G13 | IO_L3N_T0L_N5_AD15N_66 | LA08_N | |

| G14 | DGND | GND | |

| G15 | IO_L22P_T3U_N6_DBC_AD0P_66 | LA12_P | |

| G16 | IO_L22N_T3U_N7_DBC_AD0N_66 | LA12_N | |

| G17 | DGND | GND | |

| G18 | IO_L19P_T3L_N0_DBC_AD9P_66 | LA16_P | |

| G19 | IO_L19N_T3L_N1_DBC_AD9N_66 | LA16_N | |

| G20 | DGND | GND | |

| G21 | IO_L17P_T2U_N8_AD10P_66 | LA20_P | |

| G22 | IO_L17N_T2U_N9_AD10N_66 | LA20_N | |

| G23 | DGND | GND | |

| G24 | IO_L1P_T0L_N0_DBC_65 | LA22_P | |

| G25 | IO_L1N_T0L_N1_DBC_65 | LA22_N | |

| G26 | DGND | GND | |

| G27 | IO_L4P_T0U_N6_DBC_AD7P_SMBALERT_65 | LA25_P | |

| G28 | IO_L4N_T0U_N7_DBC_AD7N_65 | LA25_N | |

| G29 | DGND | GND | |

| G30 | IO_L8P_T1L_N2_AD5P_65 | LA29_P | |

| G31 | IO_L8N_T1L_N3_AD5N_65 | LA29_N | |

| G32 | DGND | GND | |

| G33 | IO_L10P_T1U_N6_QBC_AD4P_65 | LA31_P | |

| G34 | IO_L10N_T1U_N7_QBC_AD4N_65 | LA31_N | |

| G35 | DGND | GND | |

| G36 | IO_L16P_T2U_N6_QBC_AD3P_65 | LA33_P | |

| G37 | IO_L16N_T2U_N7_QBC_AD3N_65 | LA33_N | |

| G38 | DGND | GND | |

| G39 | FMC_VADJ | VADJ | |

| G40 | DGND | GND |

LPC Row H[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| H1 | FMC_VREF_A_M2C | VREF_A_M2C | |

| H2 | FMC_PRSNT_M2C_L | PRSNT_M2C_L | |

| H3 | DGND | GND | |

| H4 | IO_L12P_T1U_N10_GC_66 | CLK0_M2C_P | |

| H5 | IO_L12N_T1U_N11_GC_66 | CLK0_M2C_N | |

| H6 | DGND | GND | |

| H7 | IO_L7P_T1L_N0_QBC_AD13P_66 | LA02_P | |

| H8 | IO_L7N_T1L_N1_QBC_AD13N_66 | LA02_N | |

| H9 | DGND | GND | |

| H10 | IO_L5P_T0U_N8_AD14P_66 | LA04_P | |

| H11 | IO_L5N_T0U_N9_AD14N_66 | LA04_N | |

| H12 | DGND | GND | |

| H13 | IO_L8P_T1L_N2_AD5P_66 | LA07_P | |

| H14 | IO_L8N_T1L_N3_AD5N_66 | LA07_N | |

| H15 | DGND | GND | |

| H16 | IO_L21P_T3L_N4_AD8P_66 | LA11_P | |

| H17 | IO_L21N_T3L_N5_AD8N_66 | LA11_N | |

| H18 | DGND | GND | |

| H19 | IO_L18P_T2U_N10_AD2P_66 | LA15_P | |

| H20 | IO_L18N_T2U_N11_AD2N_66 | LA15_N | |

| H21 | DGND | GND | |

| H22 | IO_L24P_T3U_N10_66 | LA19_P | |

| H23 | IO_L24N_T3U_N11_66 | LA19_N | |

| H24 | DGND | GND | |

| H25 | IO_L10P_T1U_N6_QBC_AD4P_66 | LA21_P | |

| H26 | IO_L10N_T1U_N7_QBC_AD4N_66 | LA21_N | |

| H27 | DGND | GND | |

| H28 | IO_L3P_T0L_N4_AD15P_65 | LA24_P | |

| H29 | IO_L3N_T0L_N5_AD15N_65 | LA24_N | |

| H30 | DGND | GND | |

| H31 | IO_L7P_T1L_N0_QBC_AD13P_65 | LA28_P | |

| H32 | IO_L7N_T1L_N1_QBC_AD13N_65 | LA28_N | |

| H33 | DGND | GND | |

| H34 | IO_L9P_T1L_N4_AD12P_65 | LA30_P | |

| H35 | IO_L9N_T1L_N5_AD12N_65 | LA30_N | |

| H36 | DGND | GND | |

| H37 | IO_L15P_T2L_N4_AD11P_65 | LA32_P | |

| H38 | IO_L15N_T2L_N5_AD11N_65 | LA32_N | |

| H39 | DGND | GND | |

| H40 | FMC_VADJ | VADJ |

HPC Row J[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| J1 | DGND | GND | |

| J2 | IO_L11P_T1U_N8_GC_65 | CLK1_C2M_P | |

| J3 | IO_L11N_T1U_N9_GC_65 | CLK1_C2M_N | |

| J4 | DGND | GND | |

| J5 | DGND | GND | |

| J6 | IO_L18P_T2U_N10_AD2P_65 | HA03_P | |

| J7 | IO_L18N_T2U_N11_AD2N_65 | HA03_N | |

| J8 | DGND | GND | |

| J9 | IO_L22P_T3U_N6_DBC_AD0P_65 | HA07_P | |

| J10 | IO_L22N_T3U_N7_DBC_AD0N_65 | HA07_N | |

| J11 | DGND | GND | |

| J12 | not connected | HA11_P | |

| J13 | not connected | HA11_N | |

| J14 | DGND | GND | |

| J15 | not connected | HA14_P | |

| J16 | not connected | HA14_N | |

| J17 | DGND | GND | |

| J18 | not connected | HA18_P | |

| J19 | not connected | HA18_N | |

| J20 | DGND | GND | |

| J21 | not connected | HA22_P | |

| J22 | not connected | HA22_N | |

| J23 | DGND | GND | |

| J24 | not connected | HB01_P | |

| J25 | not connected | HB01_N | |

| J26 | DGND | GND | |

| J27 | not connected | HB07_P | |

| J28 | not connected | HB07_N | |

| J29 | DGND | GND | |

| J30 | not connected | HB11_P | |

| J31 | not connected | HB11_N | |

| J32 | DGND | GND | |

| J33 | not connected | HB15_P | |

| J34 | not connected | HB15_N | |

| J35 | DGND | GND | |

| J36 | not connected | HB18_P | |

| J37 | not connected | HB18_N | |

| J38 | DGND | GND | |

| J39 | not connected | VIO_B_M2C | |

| J40 | DGND | GND |

HPC Row K[edit | edit source]

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| K1 | not connected | VREF_B_M2C | |

| K2 | DGND | GND | |

| K3 | DGND | GND | |

| K4 | IO_L12P_T1U_N10_GC_65 | CLK1_M2C_P | |

| K5 | IO_L12N_T1U_N11_GC_65 | CLK1_M2C_N | |

| K6 | DGND | GND | |

| K7 | IO_L17P_T2U_N8_AD10P_65 | HA02_P | |

| K8 | IO_L17N_T2U_N9_AD10N_65 | HA02_N | |

| K9 | DGND | GND | |

| K10 | IO_L21P_T3L_N4_AD8P_65 | HA06_P | |

| K11 | IO_L21N_T3L_N5_AD8N_65 | HA06_N | |

| K12 | DGND | GND | |

| K13 | IO_T0U_N12_VRP_65 | HA10_P | |

| K14 | not connected | HA10_N | |

| K15 | DGND | GND | |

| K16 | not connected | HA17_P_CC | |

| K17 | not connected | HA17_N_CC | |

| K18 | DGND | GND | |

| K19 | not connected | HA21_P | |

| K20 | not connected | HA21_N | |

| K21 | DGND | GND | |

| K22 | not connected | HA23_P | |

| K23 | not connected | HA23_N | |

| K24 | DGND | GND | |

| K25 | not connected | HB00_P_CC | |

| K26 | not connected | HB00_N_CC | |

| K27 | DGND | GND | |

| K28 | not connected | HB06_P_CC | |

| K29 | not connected | HB06_N_CC | |

| K30 | DGND | GND | |

| K31 | not connected | HB10_P | |

| K32 | not connected | HB10_N | |

| K33 | DGND | GND | |

| K34 | not connected | HB14_P | |

| K35 | not connected | HB14_N | |

| K36 | DGND | GND | |

| K37 | not connected | HB17_P_CC | |

| K38 | not connected | HB17_N_CC | |

| K39 | DGND | GND | |

| K40 | not connected | VIO_B_M2C |

Electrical and Mechanical Documents[edit | edit source]

Schematics[edit | edit source]

BOM[edit | edit source]

- BoraXEVB: BORAXEVB_S.EVBBX0000C0R.1.6.0.CSV.zip

Layout[edit | edit source]

Mechanical specifications[edit | edit source]

This page describes the mechanical characteristics of the ONDA Evaluation Kit carrier board.

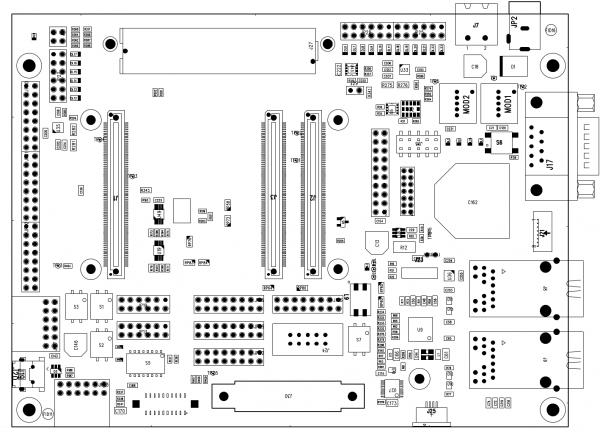

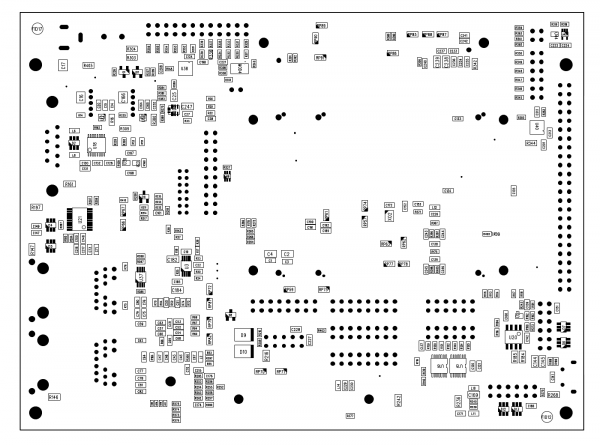

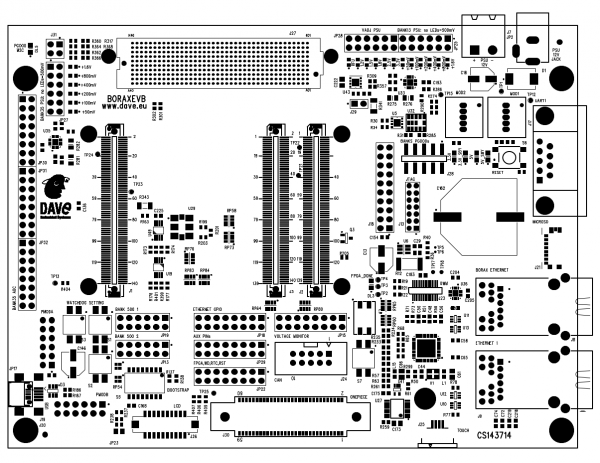

Board layout[edit | edit source]

Layout[edit | edit source]

Mechanical[edit | edit source]

- DXF: boraxevb-2D-CS143714

- STEP (3D): boraxevb_3D_step_cs143714