BORA Xpress SOM/BORA Xpress Hardware/pdf

General Information[edit | edit source]

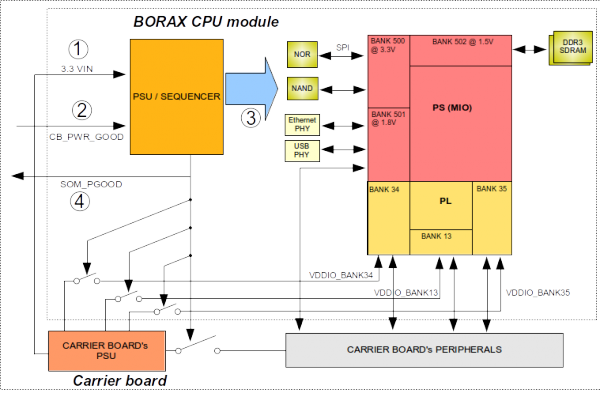

BORA Block Diagram[edit | edit source]

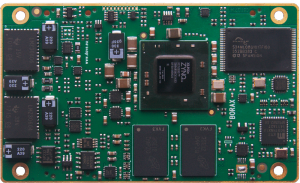

BORA TOP View[edit | edit source]

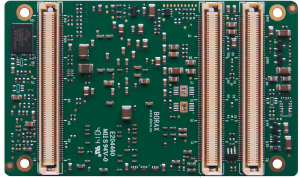

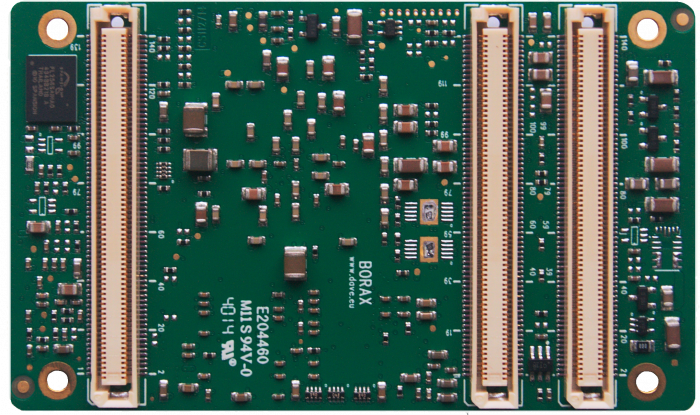

BORA BOTTOM View[edit | edit source]

Processor and memory subsystem[edit | edit source]

The heart of Bora Xpress module is composed of the following components:

- Xilinx Zynq Z-7015 (XC7Z015) / Z-7030 (XC7Z030) SoC

- Power supply unit

- DDR memory banks

- NOR and NAND flash banks

- 3x 140 pin connectors with interfaces signals

This chapter shortly describes the main Bora Xpress components.

Processor Info[edit | edit source]

The Zynq™-7000 family is based on the Xilinx Extensible Processing Platform (EPP) architecture. These products integrate a feature-rich dual-core ARM® Cortex™-A9 based processing system (PS) and 28 nm Xilinx programmable logic (PL) in a single device. The ARM Cortex-A9 CPUs are the heart of the PS and also include on-chip memory, external memory interfaces, and a rich set of peripheral connectivity interfaces. The Zynq-7000 family offers the flexibility and scalability of an FPGA, while providing performance, power, and ease of use typically associated with ASIC and ASSPs. The range of devices in the Zynq-7000 AP SoC family enables designers to target cost-sensitive as well as high-performance applications from a single platform using industry-standard tools. While each device in the Zynq-7000 family contains the same PS, the PL and I/O resources vary between the devices. As a result, the Zynq-7000 AP SoC devices are able to serve a wide range of applications including:

- Automotive driver assistance, driver information, and infotainment

- Broadcast camera

- Industrial motor control, industrial networking, and machine vision

- IP and Smart camera

- LTE radio and baseband

- Medical diagnostics and imaging

- Multifunction printers

- Video and night vision equipment

The processors in the PS always boot first, allowing a software centric approach for PL system boot and PL configuration. The PL can be configured as part of the boot process or configured at some point in the future. Additionally, the PL can be completely reconfigured or used with partial, dynamic reconfiguration (PR). PR allows configuration of a portion of the PL. This enables optional design changes such as updating coefficients or time-multiplexing of the PL resources by swapping in new algorithms as needed.

BORA Xpress can mount two versions of the Zynq processor. The following table shows a comparison between the processor models, highlighting the differences:

| Processor | Programmable logic cells | LUTs | Flip flops | Total Block RAM | DSP slices | Peak DSP performance (Symmetric FIR) | Serial Tranceivers | Peak Serial Transceiver performance |

| XC7Z015 | 74K Logic Cells | 46200 | 92400 | 3.3 Mb | 160 | 200 GMACs | GTP (4 Lanes) | 6.25 Gb/s |

| XC7Z030 | 125K Logic Cells | 78600 | 157200 | 9.3 Mb | 400 | 593 GMACs | GTX (4 Lanes) | 6.6 Gb/s |

RAM memory bank[edit | edit source]

DDR3 SDRAM memory bank is composed by 2x 16-bit width chips resulting in a 32-bit combined width bank. The following table reports the SDRAM specifications:

| CPU connection | SDRAM bus |

| Size min | 512 MB |

| Size max | 1 GB |

| Width | 32 bit |

| Speed | 533 MHz |

NOR flash bank[edit | edit source]

NOR flash is a Serial Peripheral Interface (SPI) device. By default this device is connected to SPI channel 0 and acts as boot memory. The following table reports the NOR flash specifications:

| CPU connection | SPI Channel 0 |

| Size min | 8 MB |

| Size max | 16 MB - The limitation to max 16MB is due to this Errata from Xilinx. The proposed solution by Xilinx has not been approved by DAVE Embedded Systems |

| Chip select | SPI_CS0n |

| Bootable | Yes |

NAND flash bank[edit | edit source]

On board main storage memory is a 8-bit wide NAND flash. By default it is connected to chip select. The following table reports the NAND flash specifications:

| CPU connection | Static memory controller |

| Page size | 512 byte, 2 kbyte or 4 kbyte |

| Size min | 128 MB |

| Size max | 1 GB |

| Width | 8 bit |

| Chip select | NAND_CS0 |

| Bootable | Yes |

Power supply unit[edit | edit source]

Bora Xpress, as the other Ultra Line CPU modules, embeds all the elements required for powering the unit, therefore power sequencing is self-contained and simplified. Nevertheless, power must be provided from carrier board, and therefore users should be aware of the ranges power supply can assume as well as all other parameters. For detailed information, please refer to BORA Xpress power supply unit page.

CPU module connectors[edit | edit source]

All interface signals Bora provides are routed through three 140 pin 0.6mm pitch stacking connectors (named J1, J2 and J3). The dedicated carrier board must mount the mating connectors and connect the desired peripheral interfaces according to BORA Xpress pinout specifications.

Hardware versioning and tracking[edit | edit source]

BORA Xpress SOM implements well established versioning and tracking mechanisms:

- PCB version is copper printed on PCB itself, as shown in Fig. 1

- serial number: it is printed on a white label, as shown in Fig. 2: see also Product serial number page for more details

- ConfigID: it is used by software running on the board for the identification of the product model/hardware configuration. For more details, please refer to this link

- On BORA Xpress SOM ConfigID is stored in these areas of NOR SPI OTP

Part number composition[edit | edit source]

BORA Xpress SOM module part number is identified by the following digit-code table:

| Part number structure | Options | Description |

|---|---|---|

| Family | DBX | Family prefix code |

| SOC |

|

System on chip definition (and FPGA speed grade) |

| NOR SPI |

|

QUAD SPI NOR flash memory size - The limitation to max 16MB is due to this Errata from Xilinx. The proposed solution by Xilinx has not been approved by DAVE Embedded Systems |

| RAM |

|

DDR3 Memory RAM size |

| NAND |

|

Flash memory NAND size |

| Boot/Misc |

|

Boot and Voltage Monitor options |

| Temperature range |

|

|

| PCB revision |

|

PCB release may change for manufacturing purposes (i.e. text fixture adaptation) |

| Manufacturing option |

|

typically connected to production process and quality |

| Software Configuration | -00: standard factory u-boot pre-programmed

-01: MAC address DAVE -XX: custom version |

If customers require custom SW deployed this section should be defined and agreed. Please contact technical support |

Example[edit | edit source]

BORA Xpress SOM code DBXD4110I2R-00

- DBX - BORA Xpress SOM module

- D - XC7Z030 ARM Cortex-A9 866MHz - Speed grade -1

- 4 - 16MB NOR Flash

- 1 - 1GB DDR3

- 1 - 1GB NAND flash

- 0 - NOR boot, FPGA bank 34 fixed PSU, without Voltage monitor

- I - Industrial temperature range

- 2 - PCB revision B

- R- RoHS manufacturing process

- -00 - standard u-boot pre-programmed

Pinout Table[edit | edit source]

Connectors and Pinout Table[edit | edit source]

This chapter contains the pinout description of the BORA Xpress module, grouped in six tables (two – odd and even pins – for each connector) that report the pin mapping of the three 140-pin BORA Xpress connectors.

Connectors description[edit | edit source]

In the following table are described the interface connectors on BORA Xpress SOM:

| Connector name | Connector Type | Notes | Carrier board counterpart |

|---|---|---|---|

| J1, J2, J3 | Hirose FX8C-140S-SV 3x140 pins 0.6mm pitch connectors |

Hirose FX8C-140P-SV<x>

where <x> stays for:

|

The dedicated carrier board must mount the mating connector and connect the desired peripheral interfaces according to BORA pinout specifications. See the images below for reference:

Pinout table naming conventions[edit | edit source]

Each row in the pinout tables contains the following information:

- CPU.<x> : pin connected to CPU (processing system) pad named <x>

- FPGA.<x>: pin connected to FPGA (programmable logic) pad named <x>

- CAN.<x> : pin connected to the CAN transceiver

- LAN.<x> : pin connected to the LAN PHY

- USB.<x> : pin connected to the USB transceiver

- NAND.<x>: pin connected to the flash NAND

- NOR.<x>: pin connected to the flash NOR

- SV.<x>: pin connected to voltage supervisor

- MTR: pin connected to voltage monitors

| Pin | reference to the connector pin |

| Pin Name | Pin (signal) name on the BORA Xpress connectors |

| Internal connections |

Connections to the BORA Xpress components |

| Ball/pin # | Component ball/pin number connected to signal |

| Voltage | I/O voltage levels

|

| Type | Pin type

|

SOM J1 ODD pins (1 to 139) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J1.1 | DGND | DGND | - | - | G | - | Digital ground |

| J1.3 | IO_25_VRP_35 | FPGA.IO_25_35/IO_25_VRP_35 | H5 | Bank 35 | I/O | User defined | Optional on-board pull-down |

| J1.5 | IO_L23P_T3_35 | FPGA.IO_L10P_T1_AD11P_35 | F2 | Bank 35 | I/O | User defined | |

| J1.7 | IO_L23N_T3_35 | FPGA.IO_L23N_T3_35 | F1 | Bank 35 | I/O | User defined | |

| J1.9 | IO_L21P_T3_DQS_AD14P_35 | FPGA.IO_L21P_T3_DQS_AD14P_35 | E4 | Bank 35 | I/O | User defined | |

| J1.11 | IO_L21N_T3_DQS_AD14N_35 | FPGA.IO_L21N_T3_DQS_AD14N_35 | E3 | Bank 35 | I/O | User defined | |

| J1.13 | DGND | DGND | - | - | - | - | Digital ground |

| J1.15 | IO_L19P_T3_35 | FPGA.IO_L19P_T3_35 | H4 | Bank 35 | I/O | User defined | |

| J1.17 | IO_L19N_T3_VREF_35 | FPGA.IO_L19N_T3_VREF_35 | H3 | Bank 35 | I/O | User defined | |

| J1.19 | DGND | DGND | - | - | G | - | Digital ground |

| J1.21 | IO_L17P_T2_AD5P_35 | FPGA.IO_L17P_T2_AD5P_35 | E2 | Bank 35 | I/O | User defined | |

| J1.23 | IO_L17N_T2_AD5N_35 | FPGA.IO_L17N_T2_AD5N_35 | D2 | Bank 35 | I/O | User defined | |

| J1.25 | IO_L15P_T2_DQS_AD12P_35 | FPGA.IO_L15P_T2_DQS_AD12P_35 | A2 | Bank 35 | I/O | User defined | |

| J1.27 | IO_L15N_T2_DQS_AD12N_35 | FPGA.IO_L15N_T2_DQS_AD12N_35 | A1 | Bank 35 | I/O | User defined | |

| J1.29 | DGND | DGND | - | - | G | - | Digital ground |

| J1.31 | IO_L13P_T2_MRCC_35 | FPGA.IO_L13P_T2_MRCC_35 | B4 | Bank 35 | I/O | User defined | |

| J1.33 | IO_L13N_T2_MRCC_35 | FPGA.IO_L13N_T2_MRCC_35 | B3 | Bank 35 | I/O | User defined | |

| J1.35 | DGND | DGND | - | - | G | - | Digital ground |

| J1.37 | IO_L11P_T1_SRCC_35 | FPGA.IO_L11P_T1_SRCC_35 | C6 | Bank 35 | I/O | User defined | |

| J1.39 | IO_L11N_T1_SRCC_35 | FPGA.IO_L11N_T1_SRCC_35 | C5 | Bank 35 | I/O | User defined | |

| J1.41 | IO_L9P_T1_DQS_AD3P_35 | FPGA.IO_L9P_T1_DQS_AD3P_35 | A7 | Bank 35 | I/O | User defined | |

| J1.43 | IO_L9N_T1_DQS_AD3N_35 | FPGA.IO_L9N_T1_DQS_AD3N_35 | A6 | Bank 35 | I/O | User defined | |

| J1.45 | IO_L7P_T1_AD2P_35 | FPGA.IO_L7P_T1_AD2P_35 | C8 | Bank 35 | I/O | User defined | |

| J1.47 | IO_L7N_T1_AD2N_35 | FPGA.IO_L7N_T1_AD2N_35 | B8 | Bank 35 | I/O | User defined | |

| J1.49 | DGND | DGND | - | - | G | - | Digital ground |

| J1.51 | IO_L5P_T0_AD9P_35 | FPGA.IO_L5P_T0_AD9P_35 | F5 | Bank 35 | I/O | User defined | |

| J1.53 | IO_L5N_T0_AD9N_35 | FPGA.IO_L5N_T0_AD9N_35 | E5 | Bank 35 | I/O | User defined | |

| J1.55 | IO_L3P_T0_DQS_AD1P_35 | FPGA.IO_L3P_T0_DQS_AD1P_35 | E8 | Bank 35 | I/O | User defined | |

| J1.57 | IO_L3N_T0_DQS_AD1N_35 | FPGA.IO_L3N_T0_DQS_AD1N_35 | D8 | Bank 35 | I/O | User defined | |

| J1.59 | DGND | DGND | - | - | G | - | Digital ground |

| J1.61 | IO_L1P_T0_AD0P_35 | FPGA.IO_L1P_T0_AD0P_35 | F7 | Bank 35 | I/O | User defined | |

| J1.63 | IO_L1N_T0_AD0N_35 | FPGA.IO_L1N_T0_AD0N_35 | E7 | Bank 35 | I/O | User defined | |

| J1.65 | DGND | DGND | - | - | G | - | Digital ground |

| J1.67 | VDDIO_BANK35 | S | |||||

| J1.69 | XADC_AGND | G | XADC analog ground (internally connected to DGND) | ||||

| J1.71 | XADC_AGND | G | XADC analog ground (internally connected to DGND) | ||||

| J1.73 | PS_MIO45_501 | CPU.PS_MIO45_501 | B14 | Bank 501 | I/O | 1.8V | |

| J1.75 | PS_MIO44_501 | CPU.PS_MIO44_501 | E10 | Bank 501 | I/O | 1.8V | |

| J1.77 | PS_MIO43_501 | CPU.PS_MIO43_501 | B12 | Bank 501 | I/O | 1.8V | |

| J1.79 | PS_MIO42_501 | CPU.PS_MIO42_501 | D15 | Bank 501 | I/O | 1.8V | |

| J1.81 | PS_MIO41_501 | CPU.PS_MIO41_501 | C15 | Bank 501 | I/O | 1.8V | |

| J1.83 | DGND | DGND | - | - | G | - | Digital ground |

| J1.85 | PS_MIO40_501 | CPU.PS_MIO40_501 | E9 | Bank 501 | I/O | 1.8V | |

| J1.87 | ETH_MDIO | CPU.PS_MIO53_501 | C11 | Bank 501 | I/O | 1.8V | 1kOhm pull-up |

| J1.89 | ETH_MDC | CPU.PS_MIO52_501 | D13 | Bank 501 | I/O | 1.8V | |

| J1.91 | ETH_LED1 | LAN.LED1/PME_N1 | 17 | - | 1.8V | 10kOhm pull-up | |

| J1.93 | ETH_LED2 | LAN.LED2 | 15 | - | 1.8V | 10kOhm pull-up | |

| J1.95 | DGND | DGND | - | - | G | - | Digital ground |

| J1.97 | ETH_TXRX1_M | LAN.TXRXM_B | 6 | D | |||

| J1.99 | ETH_TXRX1_P | LAN.TXRXP_B | 5 | D | |||

| J1.101 | DGND | DGND | - | - | G | - | Digital ground |

| J1.103 | ETH_TXRX0_M | LAN.ETH_TXRX0_M | 3 | D | |||

| J1.105 | ETH_TXRX0_P | LAN.ETH_TXRX0_P | 2 | D | |||

| J1.107 | D.N.C | - | Do Not Connect (reserved for internal use) | ||||

| J1.109 | RFU | - | - | - | - | - | Reserved fo future use. Must be left floating. |

| J1.111 | USBOTG_CPEN | USB.CPEN | 7 | 3.3V | |||

| J1.113 | OTG_VBUS | USB.OTG_VBUS | 2 | ||||

| J1.115 | OTG_ID | USB.ID | 1 | ||||

| J1.117 | DGND | DGND | - | - | G | - | Digital ground |

| J1.119 | SPI0_DQ3/MODE0/NAND_IO0 | CPU.PS_MIO5_500 NOR flash NAND flash |

CPU.A20 | Bank 500 | I/O | 3.3V | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. Default configuration: pull-up (BOOT_MODE[0]=1) |

| J1.121 | SPI0_DQ2/MODE2/NAND_IO2 | CPU.PS_MIO4_500 NOR flash NAND flash |

CPU.E19 | Bank 500 | I/O | 3.3V | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (BOOT_MODE[2]=0) |

| J1.123 | SPI0_DQ1/MODE1/NAND_WE_B | CPU.PS_MIO3_500 NOR flash NAND flash |

CPU.F17 | Bank 500 | I/O | 3.3V | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (BOOT_MODE[1]=0) |

| J1.125 | SPI0_DQ0/MODE3/NAND_ALE | CPU.PS_MIO2_500 NOR flash NAND flash |

CPU.A21 | Bank 500 | I/O | 3.3V | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (BOOT_MODE[3]=0) |

| J1.127 | DGND | DGND | - | - | G | - | Digital ground |

| J1.129 | SPI0_SCLK/MODE4/NAND_IO1 | CPU.PS_MIO6_500 NOR flash NAND flash |

CPU.A19 | Bank 500 | I/O | 3.3V | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (BOOT_MODE[4]=0) |

| J1.131 | NAND_BUSY | CPU.PS_MIO14_500 NOR flash NAND flash |

CPU.B17 | Bank 500 | I/O | 3.3V | 10kOhm pull-up |

| J1.133 | PS_MIO15_500 | CPU.PS_MIO15_500 WDT.WDI |

CPU.E17 WDT.1 |

Bank 500 | I/O | 3.3V | See also this page |

| J1.135 | RFU | - | - | - | - | - | Reserved fo future use. Must be left floating. |

| J1.137 | MEM_WPn | NAND.WP NOR.WP/IO2 |

NAND.19 NOR.C4 |

3.3V | |||

| J1.139 | DGND | DGND | - | - | G | - | Digital ground |

SOM J1 EVEN pins (2 to 140) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J1.2 | VDDIO_BANK35 | S | |||||

| J1.4 | DGND | DGND | - | - | - | G | Digital ground |

| J1.6 | IO_L24P_T3_AD15P_35 | FPGA.IO_L24P_T3_AD15P_35 | H1 | Bank 35 | I/O | User defined | |

| J1.8 | IO_L24N_T3_AD15N_35 | FPGA.IO_L24N_T3_AD15N_35 | G1 | Bank 35 | I/O | User defined | |

| J1.10 | IO_L22P_T3_AD7P_35 | FPGA.IO_L22P_T3_AD7P_35 | G3 | Bank 35 | I/O | User defined | |

| J1.12 | IO_L22N_T3_AD7N_35 | FPGA.IO_L22N_T3_AD7N_35 | G2 | Bank 35 | I/O | User defined | |

| J1.14 | DGND | DGND | - | - | - | G | Digital ground |

| J1.16 | IO_L20P_T3_AD6P_35 | FPGA.IO_L20P_T3_AD6P_35 | G4 | Bank 35 | I/O | User defined | |

| J1.18 | IO_L20N_T3_AD6N_35 | FPGA.IO_L20N_T3_AD6N_35 | F4 | Bank 35 | I/O | User defined | |

| J1.20 | IO_L18P_T2_AD13P_35 | FPGA.IO_L20N_T3_AD6N_35 | B2 | Bank 35 | I/O | User defined | |

| J1.22 | IO_L18N_T2_AD13N_35 | FPGA.IO_L18N_T2_AD13N_35 | B1 | Bank 35 | I/O | User defined | |

| J1.24 | DGND | DGND | - | - | - | G | Digital ground |

| J1.26 | IO_L16P_T2_35 | FPGA.IO_L16P_T2_35 | D1 | Bank 35 | I/O | User defined | |

| J1.28 | IO_L16N_T2_35 | FPGA.IO_L16N_T2_35 | C1 | Bank 35 | I/O | User defined | |

| J1.30 | DGND | DGND | - | - | - | G | Digital ground |

| J1.32 | IO_L14P_T2_AD4P_SRCC_35 | FPGA.IO_L14P_T2_AD4P_SRCC_35 | D3 | Bank 35 | I/O | User defined | |

| J1.34 | IO_L14N_T2_AD4N_SRCC_35 | FPGA.IO_L14N_T2_AD4N_SRCC_35 | C3 | Bank 35 | I/O | User defined | |

| J1.36 | IO_L12P_T1_MRCC_35 | FPGA.IO_L12P_T1_MRCC_35 | D5 | Bank 35 | I/O | User defined | |

| J1.38 | DGND | DGND | - | - | - | G | Digital ground |

| J1.40 | IO_L12N_T1_MRCC_35 | FPGA.IO_L12N_T1_MRCC_35 | C4 | Bank 35 | I/O | User defined | |

| J1.42 | IO_L10P_T1_AD11P_35 | FPGA.IO_L10P_T1_AD11P_35 | A5 | Bank 35 | I/O | User defined | |

| J1.44 | IO_L10N_T1_AD11N_35 | FPGA.IO_L10N_T1_AD11N_35 | A4 | Bank 35 | I/O | User defined | |

| J1.46 | IO_L8P_T1_AD10P_35 | FPGA.IO_L8P_T1_AD10P_35 | B7 | Bank 35 | I/O | User defined | |

| J1.48 | DGND | DGND | - | - | - | G | Digital ground |

| J1.50 | IO_L8N_T1_AD10N_35 | FPGA.IO_L8N_T1_AD10N_35 | B6 | Bank 35 | I/O | User defined | |

| J1.52 | IO_L6P_T0_35 | FPGA.IO_L6P_T0_35 | G6 | Bank 35 | I/O | User defined | |

| J1.54 | IO_L6N_T0_VREF_35 | FPGA.IO_L6N_T0_VREF_35 | F6 | Bank 35 | I/O | User defined | |

| J1.56 | IO_L4P_T0_35 | FPGA.IO_L4P_T0_35 | G8 | Bank 35 | I/O | User defined | |

| J1.58 | IO_L4N_T0_35 | FPGA.IO_L4N_T0_35 | G7 | Bank 35 | I/O | User defined | |

| J1.60 | DGND | DGND | - | - | - | G | Digital ground |

| J1.62 | IO_L2P_T0_AD8P_35 | FPGA.IO_L2P_T0_AD8P_35 | D7 | Bank 35 | I/O | User defined | |

| J1.64 | IO_L2N_T0_AD8N_35 | FPGA.IO_L2N_T0_AD8N_35 | D6 | Bank 35 | I/O | User defined | |

| J1.66 | VDDIO_BANK35 | S | |||||

| J1.68 | VDDIO_BANK35 | S | |||||

| J1.70 | XADC_AGND | G | XADC analog ground (internally connected to DGND) | ||||

| J1.72 | XADC_AGND | G | XADC analog ground (internally connected to DGND) | ||||

| J1.74 | IO_0_VRN_35 | FPGA.IO_0_35/IO_0_VRN_35 | H6 | Bank 35 | I/O | User defined | Optional on-board pull-up |

| J1.76 | RFU | - | - | - | - | - | Reserved fo future use. Must be left floating. |

| J1.78 | RFU | - | - | - | - | - | Reserved fo future use. Must be left floating. |

| J1.80 | PS_MIO49_501 | CPU.PS_MIO49_501 | C9 | Bank 501 | I/O | 1.8V | |

| J1.82 | PS_MIO48_501 | CPU.PS_MIO48_501 | D12 | Bank 501 | I/O | 1.8V | |

| J1.84 | PS_MIO47_501 | CPU.PS_MIO47_501 | B13 | Bank 501 | I/O | 1.8V | 10kOhm pull-up

TBD |

| J1.86 | DGND | DGND | - | - | - | G | Digital ground |

| J1.88 | PS_MIO46_501 | CPU.PS_MIO46_501 | D11 | Bank 501 | I/O | 1.8V | 10kOhm pull-up

TBD |

| J1.90 | ETH_INTn | Can be optionally connected to Ethernet PHY's INT_N / PME_N2 | |||||

| J1.92 | DGND | DGND | - | - | - | G | Digital ground |

| J1.94 | ETH_TXRX3_M | LAN.TXRXM_D | 11 | D | |||

| J1.96 | ETH_TXRX3_P | LAN.TXRXP_D | 10 | D | |||

| J1.98 | DGND | DGND | - | - | - | G | Digital ground |

| J1.100 | ETH_TXRX2_M | ||||||

| J1.102 | ETH_TXRX2_P | ||||||

| J1.104 | DGND | DGND | - | - | - | G | Digital ground |

| J1.106 | CLK125_NDO | LAN.CLK125_NDO | 41 | O | 1.8V | 10kOhm pull-up | |

| J1.108 | RFU | - | - | - | - | - | Reserved fo future use. Must be left floating. |

| J1.110 | RFU | - | - | - | - | - | Reserved fo future use. Must be left floating. |

| J1.112 | DGND | DGND | - | - | - | G | Digital ground |

| J1.114 | USBP1 | USB.DP | 6 | D | |||

| J1.116 | USBM1 | USB.DM | 5 | D | |||

| J1.118 | DGND | DGND | - | - | - | G | Digital ground |

| J1.120 | SPI0_CS0n | CPU.PS_MIO1_500 NOR flash |

CPU.A22 | Bank 500 | I/O | 3.3V | |

| J1.122 | NAND_CS0/SPI0_CS1 | CPU.PS_MIO0_500 NAND flash |

CPU.G17 | Bank 500 | I/O | 3.3V | 10kOhm pull-up |

| J1.124 | NAND_IO3 | CPU.PS_MIO13_500 NAND flash |

CPU.A17 | Bank 500 | I/O | 3.3V | |

| J1.126 | NAND_IO4 | CPU.PS_MIO9_500 NAND flash |

CPU.C19 | Bank 500 | I/O | 3.3V | |

| J1.128 | NAND_IO5 | CPU.PS_MIO10_500 NAND flash |

CPU.G16 | Bank 500 | I/O | 3.3V | |

| J1.130 | DGND | DGND | - | - | - | G | Digital ground |

| J1.132 | NAND_IO6 | CPU.PS_MIO11_500 NAND flash |

CPU.B19 | Bank 500 | I/O | 3.3V | |

| J1.134 | NAND_IO7 | CPU.PS_MIO12_500 NAND flash |

CPU.C18 | Bank 500 | I/O | 3.3V | |

| J1.136 | NAND_RE_B/VCFG1 | CPU.PS_MIO8_500 NAND flash |

CPU.E18 | Bank 500 | I/O | 3.3V | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. Default configuration: pull-up (VMODE[1]=1) |

| J1.138 | NAND_CLE/VCFG0 | CPU.PS_MIO7_500 NAND flash |

CPU.D18 | Bank 500 | I/O | 3.3V | This signal is pulled up or down by 20kOhm resistor to select proper bootstrap configuration. Default configuration: pull-down (VMODE[0]=0) |

| J1.140 | DGND | DGND | - | - | - | G | Digital ground |

SOM J2 ODD pins (1 to 139) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J2.1 | DGND | DGND | - | - | G | - | Digital ground |

| J2.3 | DGND | DGND | - | - | G | - | Digital ground |

| J2.5 | IO_L8P_T1_34 | FPGA.IO_L8P_T1_34 | J2 | Bank 34 | I/O | User defined | |

| J2.7 | IO_L8N_T1_34 | FPGA.IO_L8N_T1_34 | J1 | Bank 34 | I/O | User defined | |

| J2.9 | IO_L6P_T0_34 | FPGA.IO_L6P_T0_34 | M8 | Bank 34 | I/O | User defined | CAN_RX |

| J2.11 | IO_L6N_T0_VREF_34 | FPGA.IO_L6N_T0_VREF_34 | M7 | Bank 34 | I/O | User defined | |

| J2.13 | DGND | DGND | - | - | G | - | Digital ground |

| J2.15 | IO_L3P_T0_DQS_PUDC_B_34 | FPGA.IO_L3P_T0_DQS_PUDC_B_34 | K7 | Bank 34 | I/O | User defined | Internally connected to VDDIO_BANK34 via 10K resistor |

| J2.17 | IO_L3N_T0_DQS_34 | FPGA.IO_L3N_T0_DQS_34 | L7 | Bank 34 | I/O | User defined | |

| J2.19 | IO_L2P_T0_34 | FPGA.IO_L2P_T0_34 | J7 | Bank 34 | I/O | User defined | |

| J2.21 | IO_L2N_T0_34 | FPGA.IO_L2N_T0_34 | J6 | Bank 34 | I/O | User defined | |

| J2.23 | DGND | DGND | - | - | G | - | Digital ground |

| J2.25 | IO_L22P_T3_34 | FPGA.IO_L22P_T3_34 | M4 | Bank 34 | I/O | User defined | |

| J2.27 | IO_L22N_T3_34 | FPGA.IO_L22N_T3_34 | M3 | Bank 34 | I/O | User defined | |

| J2.29 | IO_L21P_T3_DQS_34 | FPGA.IO_L21P_T3_DQS_34 | N4 | Bank 34 | I/O | User defined | |

| J2.31 | IO_L21N_T3_DQS_34 | FPGA.IO_L21N_T3_DQS_34 | N3 | Bank 34 | I/O | User defined | |

| J2.33 | DGND | DGND | - | - | G | - | Digital ground |

| J2.35 | IO_L19P_T3_34 | FPGA.IO_L19P_T3_34 | N6 | Bank 34 | I/O | User defined | CAN_TX |

| J2.37 | IO_L19N_T3_VREF_34 | FPGA.IO_L19N_T3_VREF_34 | N5 | Bank 34 | I/O | User defined | |

| J2.39 | IO_L18P_T2_34 | FPGA.IO_L18P_T2_34 | P3 | Bank 34 | I/O | User defined | |

| J2.41 | IO_L18N_T2_34 | FPGA.IO_L18N_T2_34 | P2 | Bank 34 | I/O | User defined | |

| J2.43 | DGND | DGND | - | - | G | - | Digital ground |

| J2.45 | IO_L15P_T2_DQS_34 | FPGA.IO_L15P_T2_DQS_34 | M2 | Bank 34 | I/O | User defined | |

| J2.47 | IO_L15N_T2_DQS_34 | FPGA.IO_L15N_T2_DQS_34 | M1 | Bank 34 | I/O | User defined | |

| J2.49 | DGND | DGND | - | - | G | - | Digital ground |

| J2.51 | IO_L13P_T1_MRCC_34 | FPGA.IO_L13P_T1_MRCC_34 | T2 | Bank 34 | I/O | User defined | |

| J2.53 | IO_L13N_T1_MRCC_34 | FPGA.IO_L13N_T1_MRCC_34 | T1 | Bank 34 | I/O | User defined | |

| J2.55 | DGND | DGND | - | - | G | - | Digital ground |

| J2.57 | IO_L11P_T1_SRCC_34 | FPGA.IO_L11P_T1_SRCC_34 | K4 | Bank 34 | I/O | User defined | |

| J2.59 | IO_L11N_T1_SRCC_34 | FPGA.IO_L11N_T1_SRCC_34 | K3 | Bank 34 | I/O | User defined | |

| J2.61 | DGND | DGND | - | - | G | - | Digital ground |

| J2.63 | IO_L10P_T1_34 | FPGA.IO_L10P_T1_34 | L2 | Bank 34 | I/O | User defined | |

| J2.65 | IO_L10N_T1_34 | FPGA.IO_L10N_T1_34 | L1 | Bank 34 | I/O | User defined | |

| J2.67 | IO_25_VRP_34 | FPGA.IO_25_VRP_34 | R8 | Bank 34 | I/O | User defined | Optional Internal Termination resistors for DCI |

| J2.69 | IO_0_VRN_34 | FPGA.IO_0_VRN_34 | H8 | Bank 34 | I/O | User defined | Optional Internal Termination resistors for DCI |

| J2.71 | DGND | DGND | - | - | G | - | Digital ground |

| J2.73 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.75 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.77 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.79 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.81 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.83 | ETH0_PHY_RST | LAN.RESET_N | 42 | BANK 501 | O | 1.8V | Internally connected to DGND via 10K resistor |

| J2.85 | USB0_PHY_RST | USB.RESETB | 23 | BANK 501 | O | 1.8V | Internally connected to DGND via 10K resistor |

| J2.87 | CAN_3STn | LEVEL_SHIFTER.3ST# | 6 | BANK 34 | I | User defined | TBD Internally connected to VDDIO_BANK34 via 10K resistor |

| J2.89 | EXT_VMON2_V1 | - | - | - | - | Reserved for future use. Must be left floating. | |

| J2.91 | EXT_VMON2_V2 | - | - | - | - | Reserved for future use. Must be left floating. | |

| J2.93 | RTC_32KHZ | RTC.32KHZ | 1 | 3.3V | O | 3.3V | |

| J2.95 | RTC_RST | RTC.~RST | 4 | 3.3V | I/O | 3.3V | |

| J2.97 | XADC_VN_R | FPGA.VN_0 | L12 | Bank 0 | A | ||

| J2.99 | XADC_VP_R | FPGA.VP_0 | M11 | Bank 0 | A | ||

| J2.101 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.103 | CONN_SPI_RSTn | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.105 | CAN_L | CAN.CANL | 6 | - | D | - | |

| J2.107 | CAN_H | CAN.CANH | 7 | - | D | - | |

| J2.109 | DGND | DGND | - | - | G | - | Digital ground |

| J2.111 | RTC_INT/SQW | RTC.RTC_INT/SQW | 3 | 3.3V | I/O | 3.3V | It can be left open if not used. When used, a proper pull-up resistor is required on the carrier board. For further details, please refer to the Maxim Integrated DS3232 datasheet. |

| J2.113 | RTC_VBAT | RTC.VBAT | 6 | - | S | - | TBD |

| J2.115 | VBAT | CPU.VCCBATT_0 | G14 | - | S | - | TBD |

| J2.117 | DGND | DGND | - | - | G | - | Digital ground |

| J2.119 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.121 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.123 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.125 | DGND | DGND | - | - | G | - | Digital ground |

| J2.127 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.129 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.131 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.133 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.135 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.137 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.139 | DGND | DGND | - | - | G | - | Digital ground |

SOM J2 EVEN pins (2 to 140) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J2.2 | DGND | DGND | - | - | G | - | Digital ground |

| J2.4 | IO_L9P_T1_DQS_34 | FPGA.IO_L9P_T1_DQS_34 | J3 | Bank 34 | I/O | User defined | |

| J2.6 | IO_L9N_T1_DQS_34 | FPGA.IO_L9N_T1_DQS_34 | K2 | Bank 34 | I/O | User defined | |

| J2.8 | IO_L7P_T1_34 | FPGA.IO_L7P_T1_34 | J5 | Bank 34 | I/O | User defined | |

| J2.10 | IO_L7N_T1_34 | FPGA.IO_L7N_T1_34 | K5 | Bank 34 | I/O | User defined | |

| J2.12 | DGND | DGND | - | - | G | - | Digital ground |

| J2.14 | IO_L5P_T0_34 | FPGA.IO_L5P_T0_34 | N8 | Bank 34 | I/O | User defined | |

| J2.16 | IO_L5N_T0_34 | FPGA.IO_L5N_T0_34 | P8 | Bank 34 | I/O | User defined | |

| J2.18 | IO_L4P_T0_34 | FPGA.IO_L4P_T0_34 | L6 | Bank 34 | I/O | User defined | |

| J2.20 | IO_L4N_T0_34 | FPGA.IO_L4N_T0_34 | M6 | Bank 34 | I/O | User defined | |

| J2.22 | DGND | DGND | - | - | G | - | Digital ground |

| J2.24 | IO_L24P_T3_34 | FPGA.IO_L24P_T3_34 | P7 | Bank 34 | I/O | User defined | |

| J2.26 | IO_L24N_T3_34 | FPGA.IO_L24N_T3_34 | R7 | Bank 34 | I/O | User defined | |

| J2.28 | IO_L23P_T3_34 | FPGA.IO_L23P_T3_34 | R5 | Bank 34 | I/O | User defined | |

| J2.30 | IO_L23N_T3_34 | FPGA.IO_L23N_T3_34 | R4 | Bank 34 | I/O | User defined | |

| J2.32 | DGND | DGND | - | - | G | - | Digital ground |

| J2.34 | IO_L20P_T3_34 | FPGA.IO_L20P_T3_34 | P6 | Bank 34 | I/O | User defined | |

| J2.36 | IO_L20N_T3_34 | FPGA.IO_L20N_T3_34 | P5 | Bank 34 | I/O | User defined | |

| J2.38 | IO_L1P_T0_34 | FPGA.IO_L1P_T0_34 | J8 | Bank 34 | I/O | User defined | |

| J2.40 | IO_L1N_T0_34 | FPGA.IO_L1N_T0_34 | K8 | Bank 34 | I/O | User defined | |

| J2.42 | DGND | DGND | - | - | G | - | Digital ground |

| J2.44 | IO_L17P_T2_34 | FPGA.IO_L17P_T2_34 | R3 | Bank 34 | I/O | User defined | |

| J2.46 | IO_L17N_T2_34 | FPGA.IO_L17N_T2_34 | R2 | Bank 34 | I/O | User defined | |

| J2.48 | IO_L16P_T2_34 | FPGA.IO_L16P_T2_34 | N1 | Bank 34 | I/O | User defined | |

| J2.50 | IO_L16N_T2_34 | FPGA.IO_L16N_T2_34 | P1 | Bank 34 | I/O | User defined | |

| J2.52 | DGND | DGND | - | - | G | - | Digital ground |

| J2.54 | IO_L14P_T2_SRCC_34 | FPGA.IO_L14P_T2_SRCC_34 | U2 | Bank 34 | I/O | User defined | |

| J2.56 | IO_L14N_T2_SRCC_34 | FPGA.IO_L14N_T2_SRCC_34 | U1 | Bank 34 | I/O | User defined | |

| J2.58 | DGND | DGND | - | - | G | - | Digital ground |

| J2.60 | IO_L12P_T1_MRCC_34 | FPGA.IO_L12P_T1_MRCC_34 | L5 | Bank 34 | I/O | User defined | |

| J2.62 | IO_L12N_T1_MRCC_34 | FPGA.IO_L12N_T1_MRCC_34 | L4 | Bank 34 | I/O | User defined | |

| J2.64 | DGND | DGND | - | - | G | - | Digital ground |

| J2.66 | VDDIO_BANK34 | FPGA.VCCO_34 | K6 H2 L3 N7 P4 R1 |

Bank 34 | S | User defined | Bank34 I/O Power Supply |

| J2.68 | VDDIO_BANK34 | FPGA.VCCO_34 | K6 H2 L3 N7 P4 R1 |

Bank 34 | S | User defined | Bank34 I/O Power Supply |

| J2.70 | VDDIO_BANK34 | FPGA.VCCO_34 | K6 H2 L3 N7 P4 R1 |

Bank 34 | S | User defined | Bank34 I/O Power Supply |

| J2.72 | VDDIO_BANK34 | FPGA.VCCO_34 | K6 H2 L3 N7 P4 R1 |

Bank 34 | S | User defined | Bank34 I/O Power Supply |

| J2.74 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.76 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.78 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J2.80 | JTAG_TDO | CPU.TDO_0 | G9 | BANK 0 | O | 3.3V | |

| J2.82 | JTAG_TDI | CPU.TDI_0 | H9 | BANK 0 | I | 3.3V | |

| J2.84 | JTAG_TMS | CPU.TMS_0 | H10 | BANK 0 | I | 3.3V | |

| J2.86 | JTAG_TCK | CPU.TCK_0 | H11 | BANK 0 | I | 3.3V | |

| J2.88 | DGND | DGND | - | - | G | - | Digital ground |

| J2.90 | FPGA_INIT_B | FPGA.INIT_B_0 | T8 | BANK 0 | I/O | 3.3V | For further details, please refer to PL initialization signals |

| J2.92 | FPGA_PROGRAM_B | FPGA.PROGRAM_B_0 | V10 | BANK 0 | I | 3.3V | For further details, please refer to PL initialization signals

(10 kΩ pull-up resistor is already mounted on BORAX module) |

| J2.94 | FPGA_DONE | FPGA.DONE0 | T10 | BANK 0 | I/O | 3.3V | For further details, please refer to PL initialization signals |

| J2.96 | WD_SET2 | WDT.SET2 | 6 | 3.3V | I | 3.3V | |

| J2.98 | WD_SET1 | WDT.SET1 | 5 | 3.3V | I | 3.3V | |

| J2.100 | WD_SET0 | WDT.SET0 | 4 | 3.3V | I | 3.3V | |

| J2.102 | DGND | DGND | - | - | G | - | Digital ground |

| J2.104 | PS_MIO50_501 | CPU.PS_MIO50_501 USBOTG.RESETB |

D10 22 |

BANK 501 | I/O | 1.8V | For further details, please refer to Resetscheme#PS_MIO50_501 |

| J2.106 | PS_MIO51_501 | CPU.PS_MIO51_501 ETHPHY1GB.RESET_N |

C13 42 |

BANK 501 | I/O | 1.8V | For further details, please refer to Reset scheme#PS_MIO51_501 |

| J2.108 | SOM_PGOOD | SOM_PGOOD_LOGIC.OUT | n.a. | 3.3V | O | 3.3V | Internally connected to DGND via 100K resistor |

| J2.110 | CB_PWR_GOOD | 1.0VREGULATOR.ENABLE SOM_PGOOD_LOGIC.IN |

n.a. | 3.3VIN | I | 3.3V | Internally connected to 3.3VIN via 10K resistor |

| J2.112 | SYS_RSTn | CPU.PS_SRST_B_501 | C14 | BANK 501 | I | 1.8V | Internally connected to 1.8V via 20K resistor |

| J2.114 | PORSTn | CPU.PS_POR_B_500 WD.~WDO NOR.~RESET/RFU |

B18 7 A4 |

BANK 500 | I/O | 3.3V | Internally connected to 3.3VIN via 2.2K resistor. For further details, please refer to Reset_scheme#PORSTn |

| J2.116 | MRSTn | Voltage monitor | 6 | 3.3VIN | I | 3.3V | Internally connected to 3.3VIN via 2.2K resistor

For further details, please refer to Reset scheme |

| J2.118 | DGND | DGND | - | - | G | - | Digital ground |

| J2.120 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.122 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.124 | DGND | DGND | - | - | G | - | Digital ground |

| J2.126 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.128 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.130 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.132 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.134 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.136 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.138 | 3.3VIN | 3.3VIN | - | 3.3VIN | S | SOM Power Supply | |

| J2.140 | DGND | DGND | - | - | G | - | Digital ground |

SOM J3 ODD pins (1 to 139)declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J3.1 | DGND | DGND | - | - | G | - | Digital ground |

| J3.3 | MGTREFCLK0N | FPGA.MGTREFCLK0N_112 | V9 | MGTAVCC | D | ||

| J3.5 | MGTREFCLK0P | FPGA.MGTREFCLK0P_112 | U9 | MGTAVCC | D | ||

| J3.7 | DGND | DGND | - | - | G | - | Digital ground |

| J3.9 | MGTxTXP0 | FPGA.MGTXTXP0_112 | AA3 | MGTAVCC | D | ||

| J3.11 | MGTxTXN0 | FPGA.MGTXTXN0_112 | AB3 | MGTAVCC | D | ||

| J3.13 | DGND | DGND | - | - | G | - | Digital ground |

| J3.15 | MGTxTXP1 | FPGA.MGTXTXP1_112 | W4 | MGTAVCC | D | ||

| J3.17 | MGTxTXN1 | FPGA.MGTXTXN1_112 | Y4 | MGTAVCC | D | ||

| J3.19 | DGND | DGND | - | - | G | - | Digital ground |

| J3.21 | MGTxTXP2 | FPGA.MGTXTXP2_112 | AA5 | MGTAVCC | D | ||

| J3.23 | MGTxTXN2 | FPGA.MGTXTXN2_112 | AB5 | MGTAVCC | D | ||

| J3.25 | DGND | DGND | - | - | G | - | Digital ground |

| J3.27 | MGTxTXP3 | FPGA.MGTXTXP3_112 | W2 | MGTAVCC | D | ||

| J3.29 | MGTxTXN3 | FPGA.MGTXTXN3_112 | Y2 | MGTAVCC | D | ||

| J3.31 | DGND | DGND | - | - | G | - | Digital ground |

| J3.33 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J3.35 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J3.37 | DGND | DGND | - | - | G | - | Digital ground |

| J3.39 | IO_L23P_T3_13 | FPGA.IO_L23P_T3_13 | V16 | Bank 13 | I/O | User defined | |

| J3.41 | IO_L23N_T3_13 | FPGA.IO_L23N_T3_13 | W16 | Bank 13 | I/O | User defined | |

| J3.43 | DGND | DGND | - | - | G | - | Digital ground |

| J3.45 | IO_L9P_T1_DQS_13 | FPGA.IO_L9P_T1_DQS_13 | AB13 | Bank 13 | I/O | User defined | |

| J3.47 | IO_L9N_T1_DQS_13 | FPGA.IO_L9N_T1_DQS_13 | AB14 | Bank 13 | I/O | User defined | |

| J3.49 | DGND | DGND | - | - | G | - | Digital ground |

| J3.51 | IO_L7P_T1_13 | FPGA.IO_L7P_T1_13 | AA11 | Bank 13 | I/O | User defined | |

| J3.53 | IO_L7N_T1_13 | FPGA.IO_L7N_T1_13 | AB11 | Bank 13 | I/O | User defined | |

| J3.55 | DGND | DGND | - | - | G | - | Digital ground |

| J3.57 | IO_L5P_T0_13 | FPGA.IO_L5P_T0_13 | U11 | Bank 13 | I/O | User defined | |

| J3.59 | IO_L5N_T0_13 | FPGA.IO_L5N_T0_13 | U12 | Bank 13 | I/O | User defined | |

| J3.61 | DGND | DGND | - | - | G | - | Digital ground |

| J3.63 | IO_L4P_T0_13 | FPGA.IO_L4P_T0_13 | V11 | Bank 13 | I/O | User defined | |

| J3.65 | IO_L4N_T0_13 | FPGA.IO_L4N_T0_13 | W11 | Bank 13 | I/O | User defined | |

| J3.67 | DGND | DGND | - | - | G | - | Digital ground |

| J3.69 | DGND | DGND | - | - | G | - | Digital ground |

| J3.71 | IO_L3P_T0_DQS_13 | FPGA.IO_L3P_T0_DQS_13 | W12 | Bank 13 | I/O | User defined | |

| J3.73 | IO_L3N_T0_DQS_13 | FPGA.IO_L3N_T0_DQS_13 | W13 | Bank 13 | I/O | User defined | |

| J3.75 | DGND | DGND | - | - | G | - | Digital ground |

| J3.77 | IO_L2P_T0_13 | FPGA.IO_L2P_T0_13 | V15 | Bank 13 | I/O | User defined | |

| J3.79 | IO_L2N_T0_13 | FPGA.IO_L2N_T0_13 | W15 | Bank 13 | I/O | User defined | |

| J3.81 | DGND | DGND | - | - | G | - | Digital ground |

| J3.83 | IO_L1P_T0_13 | FPGA.IO_L1P_T0_13 | V13 | Bank 13 | I/O | User defined | |

| J3.85 | IO_L1N_T0_13 | FPGA.IO_L1N_T0_13 | V14 | Bank 13 | I/O | User defined | |

| J3.87 | DGND | DGND | - | - | G | - | Digital ground |

| J3.89 | IO_25_13 | FPGA.IO_25_13 | U16 | Bank 13 | I/O | User defined | |

| J3.91 | IO_0_13 | FPGA.IO_0_13 | T16 | Bank 13 | I/O | User defined | |

| J3.93 | DGND | DGND | - | - | G | - | Digital ground |

| J3.95 | VDDIO_BANK13 | FPGA.VCCO_13 | AA13 AB20 T18 Y16 W19 V12 U15 |

Bank 13 | S | User defined | Bank13 I/O Power Supply |

| J3.97 | VDDIO_BANK13 | FPGA.VCCO_13 | AA13 AB20 T18 Y16 W19 V12 U15 |

Bank 13 | S | User defined | Bank13 I/O Power Supply |

| J3.99 | VDDIO_BANK13 | FPGA.VCCO_13 | AA13 AB20 T18 Y16 W19 V12 U15 |

Bank 13 | S | User defined | Bank13 I/O Power Supply |

| J3.101 | DGND | DGND | - | - | G | - | Digital ground |

| J3.103 | DGND | DGND | - | - | G | - | Digital ground |

| J3.105 | IO_L21P_T3_DQS_13 | FPGA.IO_L21P_T3_DQS_13 | V18 | Bank 13 | I/O | User defined | |

| J3.107 | IO_L21N_T3_DQS_13 | FPGA.IO_L21N_T3_DQS_13 | W18 | Bank 13 | I/O | User defined | |

| J3.109 | DGND | DGND | - | - | G | - | Digital ground |

| J3.111 | IO_L19P_T3_13 | FPGA.IO_L19P_T3_13 | R17 | Bank 13 | I/O | User defined | |

| J3.113 | IO_L19N_T3_VREF_13 | FPGA.IO_L19N_T3_VREF_13 | T17 | Bank 13 | I/O | User defined | |

| J3.115 | DGND | DGND | - | - | G | - | Digital ground |

| J3.117 | IO_L18P_T2_13 | FPGA.IO_L18P_T2_13 | AA19 | Bank 13 | I/O | User defined | |

| J3.119 | IO_L18N_T2_13 | FPGA.IO_L18N_T2_13 | AA20 | Bank 13 | I/O | User defined | |

| J3.121 | DGND | DGND | - | - | G | - | Digital ground |

| J3.123 | IO_L16P_T2_13 | FPGA.IO_L16P_T2_13 | AB18 | Bank 13 | I/O | User defined | |

| J3.125 | IO_L16N_T2_13 | FPGA.IO_L16N_T2_13 | AB19 | Bank 13 | I/O | User defined | |

| J3.127 | DGND | DGND | - | - | G | - | Digital ground |

| J3.129 | IO_L14P_T2_SRCC_13 | FPGA.IO_L14P_T2_SRCC_13 | AA16 | Bank 13 | I/O | User defined | |

| J3.131 | IO_L14N_T2_SRCC_13 | FPGA.IO_L14N_T2_SRCC_13 | AA17 | Bank 13 | I/O | User defined | |

| J3.133 | DGND | DGND | - | - | G | - | Digital ground |

| J3.135 | IO_L12P_T1_MRCC_13 | FPGA.IO_L12P_T1_MRCC_13 | Y14 | Bank 13 | I/O | User defined | |

| J3.137 | IO_L12N_T1_MRCC_13 | FPGA.IO_L12N_T1_MRCC_13 | Y15 | Bank 13 | I/O | User defined | |

| J3.139 | DGND | DGND | - | - | G | - | Digital ground |

SOM J3 EVEN pins (2 to 140) declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Supply Group | Type | Voltage | Note |

| J3.2 | DGND | DGND | - | - | G | - | Digital ground |

| J3.4 | DGND | DGND | - | - | G | - | Digital ground |

| J3.6 | MGTREFCLK1N | FPGA.MGTREFCLK1N_112 | V5 | MGTAVCC | D | ||

| J3.8 | MGTREFCLK1P | FPGA.MGTREFCLK1P_112 | U5 | MGTAVCC | D | ||

| J3.10 | DGND | DGND | - | - | G | - | Digital ground |

| J3.12 | MGTxRXP0 | FPGA.MGTXRXP0_112 | AA7 | MGTAVCC | D | ||

| J3.14 | MGTxRXN0 | FPGA.MGTXRXN0_112 | AB7 | MGTAVCC | D | ||

| J3.16 | DGND | DGND | - | - | G | - | Digital ground |

| J3.18 | MGTxRXP1 | FPGA.MGTXRXP1_112 | W8 | MGTAVCC | D | ||

| J3.20 | MGTxRXN1 | FPGA.MGTXRXN1_112 | Y8 | MGTAVCC | D | ||

| J3.22 | DGND | DGND | - | - | G | - | Digital ground |

| J3.24 | MGTxRXP2 | FPGA.MGTXRXP2_112 | AA9 | MGTAVCC | D | ||

| J3.26 | MGTxRXN2 | FPGA.MGTXRXN2_112 | AB9 | MGTAVCC | D | ||

| J3.28 | DGND | DGND | - | - | G | - | Digital ground |

| J3.30 | MGTxRXP3 | FPGA.MGTXRXP3_112 | W6 | MGTAVCC | D | ||

| J3.32 | MGTxRXN3 | FPGA.MGTXRXN3_112 | Y6 | MGTAVCC | D | ||

| J3.34 | DGND | DGND | - | - | G | - | Digital ground |

| J3.36 | DGND | DGND | - | - | G | - | Digital ground |

| J3.38 | IO_L24P_T3_13 | FPGA.IO_L24P_T3_13 | W17 | Bank 13 | I/O | User defined | |

| J3.40 | IO_L24N_T3_13 | FPGA.IO_L24N_T3_13 | Y17 | Bank 13 | I/O | User defined | |

| J3.42 | DGND | DGND | - | - | G | - | Digital ground |

| J3.44 | IO_L10P_T1_13 | FPGA.IO_L10P_T1_13 | Y12 | Bank 13 | I/O | User defined | |

| J3.46 | IO_L10N_T1_13 | FPGA.IO_L10N_T1_13 | Y13 | Bank 13 | I/O | User defined | |

| J3.48 | DGND | DGND | - | - | G | - | Digital ground |

| J3.50 | IO_L8P_T1_13 | FPGA.IO_L8P_T1_13 | AA12 | Bank 13 | I/O | User defined | |

| J3.52 | IO_L8N_T1_13 | FPGA.IO_L8N_T1_13 | AB12 | Bank 13 | I/O | User defined | |

| J3.54 | DGND | DGND | - | - | G | - | Digital ground |

| J3.56 | IO_L6P_T0_13 | FPGA.IO_L6P_T0_13 | U13 | Bank 13 | I/O | User defined | |

| J3.58 | IO_L6N_T0_VREF_13 | FPGA.IO_L6N_T0_VREF_13 | U14 | Bank 13 | I/O | User defined | |

| J3.60 | DGND | DGND | - | - | G | - | Digital ground |

| J3.62 | MON_MGTAVCC | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.64 | MON_MGTAVCCAUX | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.66 | MON_MGTAVTT | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.68 | DGND | DGND | - | - | G | - | Digital ground |

| J3.70 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J3.72 | MON_VCCPLL | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.74 | MON_XADC_VCC | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.76 | MON_FPGA_VDDIO_BANK35 | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.78 | MON_FPGA_VDDIO_BANK34 | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.80 | MON_FPGA_VDDIO_BANK13 | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.82 | MON_1.8V_IO | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.84 | MON_3.3V | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.86 | MON_1V2_ETH | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.88 | MON_VDDQ_1V5 | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.90 | MON_1.8V | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.92 | MON_1.0V | A | By default this pin must not be connected. Optionally it can route power voltage generated by BoraXpress PSU. This option is meant to allow monitoring such voltage by carrier board circuitry. It is not meant to power carrier board devices. For more information please contact technical support. | ||||

| J3.94 | DGND | DGND | - | - | G | - | Digital ground |

| J3.96 | VDDIO_BANK13 | FPGA.VCCO_13 | AA13 AB20 T18 Y16 W19 V12 U15 |

Bank 13 | S | User defined | Bank13 I/O Power Supply |

| J3.98 | VDDIO_BANK13 | FPGA.VCCO_13 | AA13 AB20 T18 Y16 W19 V12 U15 |

Bank 13 | S | User defined | Bank13 I/O Power Supply |

| J3.100 | RFU | - | - | - | - | - | Reserved for future use. Must be left floating. |

| J3.102 | DGND | DGND | - | - | G | - | Digital ground |

| J3.104 | IO_L22P_T3_13 | FPGA.IO_L22P_T3_13 | U17 | Bank 13 | I/O | User defined | |

| J3.106 | IO_L22N_T3_13 | FPGA.IO_L22N_T3_13 | U18 | Bank 13 | I/O | User defined | |

| J3.108 | DGND | DGND | - | - | G | - | Digital ground |

| J3.110 | IO_L20P_T3_13 | FPGA.IO_L20P_T3_13 | U19 | Bank 13 | I/O | User defined | |

| J3.112 | IO_L20N_T3_13 | FPGA.IO_L20N_T3_13 | V19 | Bank 13 | I/O | User defined | |

| J3.114 | DGND | DGND | - | - | G | - | Digital ground |

| J3.116 | IO_L17P_T2_13 | FPGA.IO_L17P_T2_13 | AB16 | Bank 13 | I/O | User defined | |

| J3.118 | IO_L17N_T2_13 | FPGA.IO_L17N_T2_13 | AB17 | Bank 13 | I/O | User defined | |

| J3.120 | DGND | DGND | - | - | G | - | Digital ground |

| J3.122 | IO_L15P_T2_DQS_13 | FPGA.IO_L15P_T2_DQS_13 | AB21 | Bank 13 | I/O | User defined | |

| J3.124 | IO_L15N_T2_DQS_13 | FPGA.IO_L15N_T2_DQS_13 | AB22 | Bank 13 | I/O | User defined | |

| J3.126 | DGND | DGND | - | - | G | - | Digital ground |

| J3.128 | IO_L13P_T2_MRCC_13 | FPGA.IO_L13P_T2_MRCC_13 | Y18 | Bank 13 | I/O | User defined | |

| J3.130 | IO_L13N_T2_MRCC_13 | FPGA.IO_L13N_T2_MRCC_13 | Y19 | Bank 13 | I/O | User defined | |

| J3.132 | DGND | DGND | - | - | G | - | Digital ground |

| J3.134 | IO_L11P_T1_SRCC_13 | FPGA.IO_L11P_T1_SRCC_13 | AA14 | Bank 13 | I/O | User defined | |

| J3.136 | IO_L11N_T1_SRCC_13 | FPGA.IO_L11N_T1_SRCC_13 | AA15 | Bank 13 | I/O | User defined | |

| J3.138 | DGND | DGND | - | - | G | - | Digital ground |

| J3.140 | DGND | DGND | - | - | G | - | Digital ground |

Power and reset[edit | edit source]

Power Supply Unit (PSU) and recommended power-up sequence[edit | edit source]

Implementing correct power-up sequence for Zynq-based system is not a trivial task because several power rails are involved. Bora Xpress SOM simplifies this task and embeds all the needed circuitry. The following picture shows a simplified block diagram of power supply subsystem.

The recommended power-up sequence is:

- main power supply rail (3.3VIN) ramps up

- carrier board circuitry raises CB_PWR_GOOD; this indicates 3.3VIN rail is stable (1)

- Bora Xpress's PSU enables and sequences DC/DC regulators to turn circuitry on

- SOM_PGOOD signal is raised; this active-high signal indicates that SoM's I/O is powered. This signal can be used to manage carrier board power up sequence in order to prevent back powering (from SoM to carrier board or vice versa).

Please note that FPGA Bank 13, FPGA Bank 34 and FPGA Bank 35 of the PL must be powered by carrier board even if they are not used to implement any function. Three dedicated power rails are available for this purpose (VDDIO_BANK34, VDDIO_BANK35 and VDDIO_BANK13), offering the system designer the freedom to select the I/O voltage of these three banks. The power rails of these banks are enabled by the SOM_PGOOD signal and are connected to the I/O power supply rail provided by the carrier board.

Bora Xpress's PSU is designed to be robust against misbehaving power rails. However, the recommended power-on ramp for core and I/O supplies ranges from 1 to 6 V/ms.

N.B.: Regarding power off, it is recommended that I/O supply is turned off before core supply.

(1) This step is not mandatory and CB_PWR_GOOD can be left floating. CB_PWR_GOOD is provided to prevent, if necessary, Bora Xpress's PSU to turn on during ramp of carrier board 3.3VIN rail. Depending on carrier board's PSU design, this may lead to undesired glitches during ramp-up.

XCN15034 and power-off sequence[edit | edit source]

On 29th September 2015 Xilinx released a Product Change Notice indicating new power on/off requirements about Zynq components. A specific analysis has been undertaken with the help of Xilinx technical support to verify the compliance of Bora Xpress with respect to the new requirements. This activity has led to the following recommendation: in order to prevent situations that might not fulfill such requirements, 3.3VIN off ramp speed must not exceed 47V/s.

For more details about this matter, please refer to AR #65240[1] and XCN15034[2].

Reset scheme and voltage monitoring[edit | edit source]

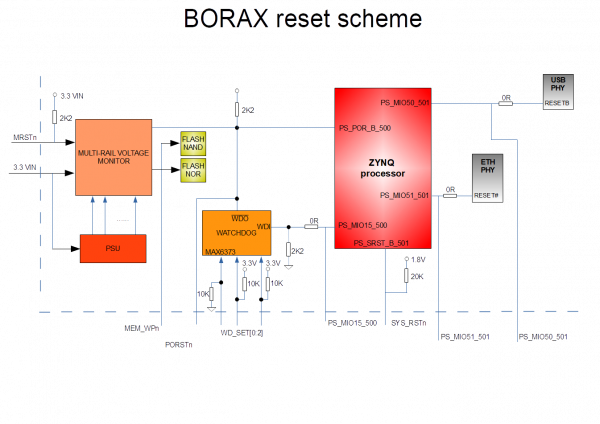

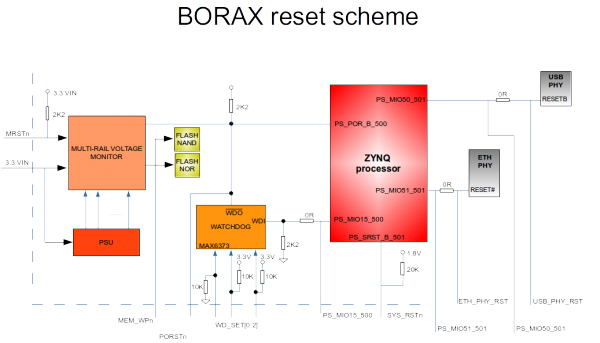

The following picture shows the simplified block diagram of reset scheme and voltage monitoring.

Reset signals[edit | edit source]

The available reset signals are described in detail in the following sections.

MRSTn (J2.116)[edit | edit source]

MRSTn is a de-bounced input for manual reset (for example to connect a push-button). This signal connected to the voltage monitor and is pulled-up to 3.3VIN through a 2.2kOhm resistor.

PORSTn (J2.114)[edit | edit source]

This is a bidirectonal open-drain signal that is connected to Zynq's PS_SRST_B and can be asserted by the following devices:

- a multi-rail voltage monitor that monitors 3.3VIN power rails and all of the rails generated by Bora Xpress's PSU. This monitor

- in case of a power glitch, asserts MEM_WPn signal in order to prevent any spurious write operation on flash memories too. MEM_WPn is 3.3V, push-pull, active low.

- has a timeout (set through an on-board capacitor) of about 200 ms.

- provides MRSTn debounced input for manual reset (for example to connect a push-button). This signal is pulled-up to 3.3VIN through a 2.2kOhm resistor.

- a watchdog timer (Maxim MAX6373). For more details please refer to Watchdog section.

PORSTn is pulled-up to 3.3VIN through a 2.2kOhm resistor.

SYS_RSTn (J2.112)[edit | edit source]

This signal is connected to Zynq's PS_SRST_B and is pulled-up to 1.8V through a 20kOhm resistor.

PS_MIO51_501 (Ethernet PHY reset)[edit | edit source]

By default, this signal is connected to the on-board Ethernet PHY reset input as depicted in the above figure. This scheme allows complete software control of the PHY hardware reset regardless of the PL status.

For example, this is how the reset signal is handled in BELK 4.1.5:

- U-Boot

board_initroutine generates a hardware reset pulse. This initializes the component to its default register values, which are partly determined by the PHY's strapping pins. - Upon boot up, the Linux kernel issues a software reset via the BCMR register. If a hardware reset is required instead, the

macbkernel driver and/or the related device tree properties have to be modified for enabling this feature.

PS_MIO50_501 (USB PHY reset)[edit | edit source]

By default, this signal is connected to the on-board USB PHY reset input as depicted in the above figure. This scheme allows complete software control of the PHY hardware reset regardless of the PL status.

For example, this is how the reset signal is handled in BELK 4.1.5:

- U-Boot

board_initroutine generates a hardware reset pulse. This initializes the component to its default register values. - Linux kernel does not issue any further hardware reset. If a hardware reset is required upon Linux boot up, the

phy-ulpikernel driver and/or the according device tree properties have to be modified for enabling this feature.

Clock scheme[edit | edit source]

Bora is equipped with three independent active oscillators:

- processor (33.3 MHz)

- ethernet PHY (25 MHz)

- USB PHY (26 MHz)

Generally speaking, no clocks have to be provided by the carrier board.

PL initialization signals[edit | edit source]

This page provides information about the Programmable Logic (PL) initialization signals: PROGRAM_B, INIT_B, and DONE.

Please refer to Zynq Technical Reference Manual UG-585 for more information about usage and configuration of initialization circuit and signals.

As described in Table 6-24: PL Initialization Signals of Zynq-7000 SoC Technical Reference Manual (UG585), the user can initialize the PL using these signals.

BORA, BORAX, and BORALite SOM are configured in the following way:

- PROGRAM_B has an internal 10kΩ pull-up to VCCO_0 as indicated on Xilinx AR#56272

- INIT_B has no pull-up/down

- DONE has no pull-up/down. It does not require any external pull-up or pull-down but can be used for connecting a user led for a configuration completed indication (see for example BoraXEVB schematics).

External pull-ups[edit | edit source]

- PROGRAM_B: UG-585 indicates to use a 4.7kΩ pull-up resistor for this signal. This value was not known when the Xilinx Zynq 7000 family was released. Nevertheless, to date, no issues have been reported although this pull-up is a little bit weaker. In any case, an external pull-up to a 3.3V controlled power domain can be put in parallel with the internal 10kΩ resistor to get a stronger pull-up. For more details, please contact the technical support.

- INIT_B: for using this signal as PL initializing signal Low-to-High transition, place an external pull-up to a 3.3V controlled power domain.

System boot[edit | edit source]

The boot process begins at Power On Reset (POR) where the hardware reset logic forces the ARM core to begin execution starting from the on-chip boot ROM. The boot process is multi-stage and minimally includes the Boot ROM and the first-stage boot loader (FSBL). The Zynq-7000 AP SoC includes a factory-programmed Boot ROM that is not useraccessible. The boot ROM:

- determines whether the boot is secure or non-secure

- performs some initialization of the system and cleanups

- reads the mode pins to determine the primary boot device

- once it is satisfied, it executes the FSBL

After a system reset, the system automatically sequences to initialize the system and process the first stage boot loader from the selected external boot device. The process enables the user to configure the AP SoC platform as needed, including the PS and the PL. Optionally, the JTAG interface can be enabled to give the design engineer access to the PS and the PL for test and debug purposes.

Boot options[edit | edit source]

The boot ROM supports configuration from four different slave interfaces:

- Quad-SPI

- NAND

- NOR flash (not available on BORA, BORA Xpress, BORA Lite)

- SD card

Boot mode is selectable via five mode pins (BOOT_MODE[4:0]), and two voltage mode signals, (VMODE[1:0]). The BOOT_MODE pins are MIO[6:2] and the VMODE pins are MIO[8:7]. The pins are used as follows:

| Function | Boot signals | Available options |

|---|---|---|

| JTAG mode | BOOT_MODE[3] MIO[2] |

0: Cascaded JTAG 1: Independent JTAG |

| Boot mode | BOOT_MODE[0-2-1] MIO[5:3] |

000: JTAG 010: NAND 100: Quad-SPI 110: SD card |

| PLLs enable | BOOT_MODE[4] MIO[6] |

0: PLL used 1: PLL bypassed |

| MIO Bank 0 Voltage | VMODE[0] MIO[7] |

0: 2.5 V, 3.3 V 1: 1.8 V |

| MIO Bank 0 Voltage | VMODE[1] MIO[8] |

0: 2.5 V, 3.3 V 1: 1.8 V |

In order to fully understand how boot works on BORA platform, please refer to chapter 6 ("Boot and configuration") of the Zynq7000 Technical Reference Manual.

Default boot configuration[edit | edit source]

Default configuration for BORA module is:

- Mode[0..3] = 1000: Quad-SPI mode

- Mode[4] = 0: PLL not bypassed

- VCFG[0] = 0: 2.5V, 3.3V operations for bank 0

- VCFG[1] = 1: 1.8 operations for bank 1

Assuming that:

- default configuration is not changed,

- there's a valid boot code programmed in SPI flash memory the actual boot sequence performed by ARM core will be:

- Bootrom is executed from internal ROM code memory

- FSBL is copied from on-board NOR flash memory connected to SPI0 port to on-chip SRAM by bootrom

- FSBL is executed from on-chip SRAM

- U-Boot bootloader (2nd stage) is copied by FSBL from NOR flash memory connected to Quad-SPI port to SDRAM

- U-boot (2nd stage) is executed from SDRAM

If no boot code is available in SPI NOR flash, the bootrom tries JTAG peripheral booting.

Boot sequence customization[edit | edit source]

BOOT_MODE[4:0] are routed to the J1 connector, enabling for the customization of the boot sequence through a simple resistor network that can be implemented on carrier board hosting BORA module.

| Mode signal | J1 pin | Pin name |

|---|---|---|

| BOOT_MODE[4] | J1.129 | SPI0_SCLK/MODE4/NAND_IO1 |

| BOOT_MODE[3] | J1.125 | SPI0_DQ0/MODE3/NAND_ALE |

| BOOT_MODE[2] | J1.121 | SPI0_DQ2/MODE2/NAND_IO2 |

| BOOT_MODE[1] | J1.123 | SPI0_DQ1/MODE1/NAND_WE |

| BOOT_MODE[0] | J1.119 | SPI0_DQ3/MODE0/NAND_IO0 |

On board JTAG connector[edit | edit source]

The Zynq-7000 family of AP SoC devices provides debug access via a standard JTAG (IEEE 1149.1) debug interface. This JTAG port grants access to the device chain composed of both the CPU core and the FPGA part.

JTAG signals are connected to the pinout connector (J2) on BORA.

| Pin# | Pin name | Function | Notes |

|---|---|---|---|

| J2.86 | JTAG_TCK | - | - |

| J2.84 | JTAG_TMS | - | - |

| J2.80 | JTAG_TDO | - | - |

| J2.82 | JTAG_TDI | - | - |

| J2.90 | FPGA_INIT_B | - | For further details, please refer to PL initialization signals |

| J2.92 | FPGA_PROGRAM_B | - | For further details, please refer to PL initialization signals

(10 kΩ pull-up resistor is already mounted on BORA module) |

| J2.94 | FPGA_DONE | - | For further details, please refer to PL initialization signals |

Peripherals[edit | edit source]

Programmable logic[edit | edit source]

The following paragraphs describe in detail the available PL I/O signals and how they are routed to the BORA Xpress connectors. The Zynq-7000 AP SoC is split into I/O banks to allow for flexibility in the choice of I/O standards, thus each table reports one bank configuration. Moreover, BORA Xpress design allows carrier board to power all three PL banks in order to achieve complete flexibility in terms of I/O voltage levels too. For more details about PCB design considerations, please refer to the Advanced routing and carrier board design guidelines article.

The following table reports the I/O banks characteristics:

| FPGA Bank | XC7Z015 | XC7Z030 | Bank power supply pins | I/O | Differentials Pairs |

|---|---|---|---|---|---|

| Bank 13 | HR | HR | J3.95 J3.96 J3.97 J3.98 J3.99 |

50 | 24 |

| Bank 34 | HR | HP | J2.66 J2.68 J2.70 J2.72 |

50 | 24 |

| Bank 35 | HR | HP | J1.2 J1.66 J1.67 J1.68 |

50 | 24 |

FPGA I/O Bank definitions:

- HR = High Range I/O with support for I/O voltage from 1.2V to 3.3V

- HP = High Performance I/O with support for I/O voltage from 1.2V to 1.8V

Each user I/O is labeled IO_LXXY_Tn_ZZZ_ADi_#, where:

- IO indicates a user I/O pin.

- L indicates a differential pair, with XX a unique pair in the bank and Y = [P|N] for the positive/negative sides of the differential pair.

- Tn indicates the memory byte group [0-3]

- ZZZ indicates a MRCC, SRCC or DQS pin

- ADi indicates a XADC (analog-to-digital converter) differential auxiliary analog input [0–15].

- # indicates the bank number.

Here is a list of FPGA I/O actually used inside BORA Xpress SOM:

- IO_L6P_T0_34 : CAN_RX

- IO_L19P_T3_34 : CAN_TX

Routing Information[edit | edit source]

Routing implemented on Bora Xpress SoM allows the use of MGT serial tranceivers differential pairs ans FPGA's signals as differential pairs as well as single-ended.

This spreadsheet details routing rules applied to Bora Xpress's signals. Signals are grouped by bank number. The table details also the routing rules of the Bora Xpress SOM combined with Bora Xpress EVB highlighting routing to the FPGA Mezzanine Card (FMC) connector on Bora Xpress EVB.

Processing System[edit | edit source]

The 54 pins of the MIO module are assigned as reported in the following table:

| MIO Pins | Function |

|---|---|

| MIO[0:14] | Quad-SPI and NAND flash |

| MIO[15] | EX_WDT_REARM (watchdog WDI) Optionally, it can act as SWDT reset out |

| MIO[16:27] | Gigabit Ethernet |

| MIO[28:39] | USB On-The-Go |

| MIO[40:45] | SD/SDIO/MMC |

| MIO[46:47] | I²C0 |

| MIO[48:49] | UART1 |

| MIO[50] | USB PHY reset |

| MIO[51] | ETH0 PHY reset |

| MIO[52] | Ethernet Management Data Clock input |

| MIO[53] | Ethernet Management Data Input/Output |

Gigabit Ethernet[edit | edit source]

On-board Ethernet PHY (Micrel KSZ9031RNX) provides interface signals required to implement the 10/100/1000 Mbps Ethernet port. The transceiver is connected to the Gigabit Ethernet Controller (GEM) through RGMII interface on MIO bank 1, pins PS_MIO[16:27]. For further details (eg: connection and selection of the magnetics), please refer to the Micrel KSZ9031RNX datasheet. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| ETH_TXRX0_P | J1.105 | Media Dependent Interface[0], positive pin | - |

| ETH_TXRX0_M | J1.103 | Media Dependent Interface[0], negative pin | - |

| ETH_TXRX1_P | J1.99 | Media Dependent Interface[1], positive pin | - |

| ETH_TXRX1_M | J1.97 | Media Dependent Interface[1], negative pin | - |

| ETH_TXRX2_P | J1.102 | Media Dependent Interface[2], positive pin | - |

| ETH_TXRX2_M | J1.100 | Media Dependent Interface[2], negative pin | - |

| ETH_TXRX3_P | J1.96 | Media Dependent Interface[3], positive pin | - |

| ETH_TXRX3_M | J1.94 | Media Dependent Interface[3], negative pin | - |

| ETH_MDIO | J1.87 | Management Data Input/Output | - |

| ETH_MDC | J1.89 | Management Data Clock input | - |

| ETH_LED1 | J1.91 | Activity LED | - |

| ETH_LED2 | J1.93 | Link LED | - |

| DVDDH | J1.107 | 1.8V digital VDD_I/O of Ethernet PHY | - |

SD/SDIO[edit | edit source]

The SD/SDIO controller controller is compatible with the standard SD Host Controller Specification Version 2.0 Part A2. The core also supports up to seven functions in SD1, SD4, but does not support SPI mode. It does support SD high-speed (SDHS) and SD High Capacity (SDHC) card standards. The SD/SDIO controller also supports MMC3.31.

The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_SD0_CLOCK | J1.85 | SD/SDIO/MMC clock | - |

| PS_SD0_CMD | J1.81 | SD/SDIO/MMC command | - |

| PS_SD0_DAT0 | J1.79 | SD/SDIO/MMC data 0 | - |

| PS_SD0_DAT1 | J1.77 | SD/SDIO/MMC data 1 | - |

| PS_SD0_DAT2 | J1.75 | SD/SDIO/MMC data 2 | - |

| PS_SD0_DAT3 | J1.73 | SD/SDIO/MMC data 3 | - |

QUAD SPI[edit | edit source]

Quad-SPI is used to access multi-bit serial flash memory devices for high throughput and low pin count applications. The controller operates in one of three modes: I/O mode, linear addressing mode, and legacy SPI mode. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| SPI0_CS0 | J1.120 | Chip select 0 | MIO bank 0, pin 1 |

| SPI0_CS1 | J1.122 | Chip select 1 | MIO bank 0, pin 0 |

| SPI0_DQ0 | J1.125 | 1-bit: Master Output 2-bit: I/O0 4-bit: I/O0 |

MIO bank 0, pin 2 |

| SPI0_DQ1 | J1.123 | 1-bit: Master Input 2-bit: I/O1 4-bit: I/O1 |

MIO bank 0, pin 3 |

| SPI0_DQ2 | J1.121 | 1-bit: Write protect 2-bit: Write protect 4-bit: I/O0 |

MIO bank 0, pin 4 |

| SPI0_DQ3 | J1.119 | 1-bit: Hold 2-bit: Hold 4-bit: I/O3 |

MIO bank 0, pin 5 |

| SPI0_SCLK | J1.129 | Serial clock | MIO bank 0, pin 6 |

Static memory controller (NAND)[edit | edit source]

Static memory controller (SMC) signals are routed to the connectors to connect an external flash NAND memory chip. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| NAND_CS0 | J1.122 | NAND flash chip select | MIO bank 0, pin 0 |

| NAND_IO0 | J1.119 | NAND I/O 0 | MIO bank 0, pin 5 |

| NAND_IO1 | J1.129 | NAND I/O 1 | MIO bank 0, pin 6 |

| NAND_IO2 | J1.121 | NAND I/O 2 | MIO bank 0, pin 4 |

| NAND_IO3 | J1.124 | NAND I/O 3 | MIO bank 0, pin 13 |

| NAND_IO4 | J1.126 | NAND I/O 4 | MIO bank 0, pin 9 |

| NAND_IO5 | J1.128 | NAND I/O 5 | MIO bank 0, pin 10 |

| NAND_IO6 | J1.132 | NAND I/O 6 | MIO bank 0, pin 11 |

| NAND_IO7 | J1.134 | NAND I/O 7 | MIO bank 0, pin 12 |

| NAND_WE | J1.123 | NAND write enable | MIO bank 0, pin 3 |

| NAND_ALE | J1.125 | NAND address latch | MIO bank 0, pin 2 |

| NAND_BUSY | J1.131 | NAND Busy | MIO bank 0, pin 14 |

| NAND_RE | J1.136 | NAND read enable | MIO bank 0, pin 8 |

| NAND_CLE | J1.138 | NAND command latch enable | MIO bank 0, pin 7 |

CAN[edit | edit source]

CAN port is connected to on-board transceiver (TI SN65HVD232) which converts the single-ended CAN signals of the controller to the differential signals of the physical layer. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| CAN_H | J2.107 | High bus output | - |

| CAN_L | J2.105 | Low bus output | - |

Optionally, the on-board PHY can be excluded (for example, to use an external PHY on the carrier board) and the single-ended CAN signals are routed to the connectors. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| CAN_RX | J2.35 | Receive data pin | Routed to EMIO (pin IO_L19P_T3_34) |

| CAN_TX | J2.9 | Transmit data pin | Routed to EMIO (pin IO_L6P_T0_34) |

Please contact our Sales Department for more information about this hardware option.

I^2C0[edit | edit source]

This I²C module is a bus controller that can function as a master or a slave in a multi-master design. It supports an extremely wide clock frequency range up to 400 Kb/s. I²C0 is internally connected to the following devices:

- Thermal IC: Texas Instruments TMP421 (Address: 0x4F)

- RTC: Maxim Integrated DS3232 (Address: 0x68)

The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_I2C0_CK | J1.88 | I2C clock | - |

| PS_I2C0_DAT | J1.84 | I2C data | - |

UART 1[edit | edit source]

The UART controller is a full-duplex asynchronous receiver and transmitter that supports a wide range of programmable baud rates and I/O signal formats. UART1 port is routed to the SOM connectors as a 2-wire interface. The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| PS_UART1_RX | J1.80 | UART Receive line | - |

| PS_UART1_TX | J1.82 | UART Transmit line | - |

USB[edit | edit source]

Bora provides one USB 2.0 (Full Speed, up to 480 Mbps) port with on-board PHY (SMSC USB3317) and support to the On-The-Go (OTG) specifications. The transceiver is connected to the USB1 controller (MIO bank 1, pins PS_MIO[28:39]). The following table describes the interface signals:

| Pin name | Conn. pin | Function | Notes |

|---|---|---|---|

| USBP1 | J1.114 | D+ pin of the USB cable | - |

| USBM1 | J1.116 | D- pin of the USB cable | - |

| USBOTG_CPEN | J1.111 | External 5 volt supply enable | This pin is used to enable the external Vbus power supply |

| OTG_VBUS | J1.113 | VBUS pin of the USB cable | - |

| OTG_ID | J1.115 | ID pin of the USB cable | For non-OTG applications this pin can be floated. For an A-device ID is grounded. For a B-device ID is floated. |

Real Time Clock[edit | edit source]

An on-board Maxim Integrated DS3232 device provides a very accurate, temperature-compensated real-time clock (RTC) resource with:

- Temperature-compensated crystal oscillator

- Date, time and calendar

- Alarm capability

- Backup power from external battery

- ±3.5ppm accuracy from -40°C to +85°C

- 236 Bytes of Battery-Backed SRAM

- I²C Interface

Backup power is provided through the RTC_VBAT (J2.113) signal. If not used, RTC_VBAT must be externally connected to GND. For a detailed description of RTC characteristics, please refer to the DS3232 datasheet.

Watchdog[edit | edit source]

An external watchdog timer (WDT), Maxim MAX6373[3]), is connected to the PORSTn signal. During normal operation, the microprocessor should repeatedly toggle the watchdog input WDI before the selected watchdog timeout period elapses to demonstrate that the system is processing code properly. If the μP does not provide a valid watchdog input transition before the timeout period expires, the supervisor asserts a watchdog (WDO) output to signal that the system is not executing the desired instructions within the expected time frame. The watchdog output pulse is used to reset the μP.

Default configuration[edit | edit source]

Default mounting option is depicted in the following figure.

WDI is connected to Zynq's PS_MIO15_500 I/O. This signal is available on Bora Xpress connectors as PS_MIO15_500 (J1.133).

MAX6373 timeout is pin-selectable. It can be configured through the WD_SET0 (J2.100), WD_SET1 (J2.98) and WD_SET2 (J2.96) signals. By default, they are configured as follows:

- WD_SET2 = 1

- WD_SET1 = 1

- WD_SET0 = 0

This set selects the option (the exhaustive list of configurations options is descripted in table 1 of reference [3]):

- tDELAY = first edge

- tWD = 10s.

In other words, WDT is started when the first transition on WDI input is detected. Once started, its timeout period is 10s. The first transition of WDI input is under software control.

When the watchdog is started, the software (bootloader/operating system) must take care of toggling the watchdog trigger pin (WDI) before the timeout expiration.

Selecting different configurations[edit | edit source]

Since WD_SETx signals are routed externally, WDT configuration can be changed by optional circuitry implemented on the carrier board. Different solutions can be implemented on the carrier board, depending on system requirements. The easiest circuit consists of additional stronger pull-up/down resistors connected to WD_SETx pins in order to overrule default configuration. As MAX6373 allows to change the configuration during operation, more complex solutions can be implemented as well.

Please note that on the BORA Xpress evaluation board, by default WDT is disabled via S1, S2 and S3 dip switches (WD_SET2=0, WD_SET1=1, WD_SET0=1).

It is also worth mentioning that Zynq integrates a System Watchdog Timer (SWDT) that can optionally generates a reset pulse on PS_MIO15_500 pad if this is configured as SWDT reset. In case such a configuration is of interest, on request MAX6373 may not be populated. For more details about this option, please contact Sales Department.

Thermal IC[edit | edit source]

An on-board thermal IC (Texas Instruments TMP421) connected to the I²C0 interface can work as a local temperature sensor, providing the measurement of its internal temperature, but also as a remote temperature sensor, since it is connected to the XADC_DXP/XADC_DXN of the Zynq processor, providing the measurement of the Zynq internal temperature.

For a detailed description of the thermal IC characteristics, please refer to the TMP421 datasheet.

Electrical, Thermal and Mechanical Features[edit | edit source]

Operational characteristics[edit | edit source]

Maximum ratings[edit | edit source]

| Parameter | Min | Typ | Max | Unit |

|---|---|---|---|---|

| Main power supply voltage | 3.14 | 3.3 | 3.46 | V |

Recommended ratings[edit | edit source]

| Parameter | Min | Typ | Max | Unit |

|---|---|---|---|---|

| Main power supply voltage | 3.3 | V |

Power consumption[edit | edit source]

Providing theoretical maximum power consumption value would be useless for the majority of system designers building their application upon BORA Xpress SOM because, in most cases, this would lead to an over-sized power supply unit.

Please note that BORA Xpress platform is so flexible that it is virtually impossible to test for all possible configurations and applications on the market.

Generally speaking, application specific requirements have to be taken into consideration in order to size power supply unit and to implement thermal management properly.

Thermal management[edit | edit source]

BORA Xpress product is designed to support the maximum available temperature range declared by the manufacturer. The customer shall define and conduct a reasonable number of tests and verification in order to qualify the DUT capabilities to manage the heat dissipation.

Any heatsink, fan etc shall be defined case by case depending on the various use conditions like: air cooling (forced or not), enclosure dimensions, mechanical/thermal coupling with heatsink. A proper thermal analysis must be investigated on the real use scenario which depends on FPGA design, frequency configurations, working signals, etc.

DAVE Embedded Systems' team is available for any additional information, please contact sales@dave.eu.

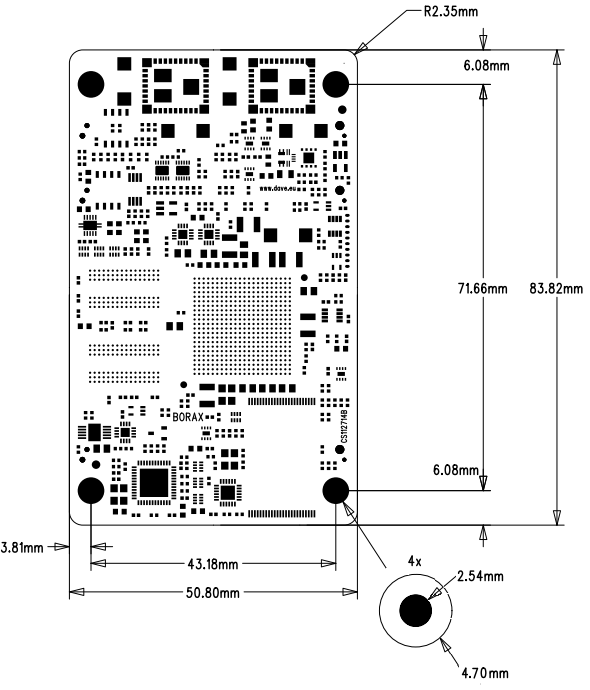

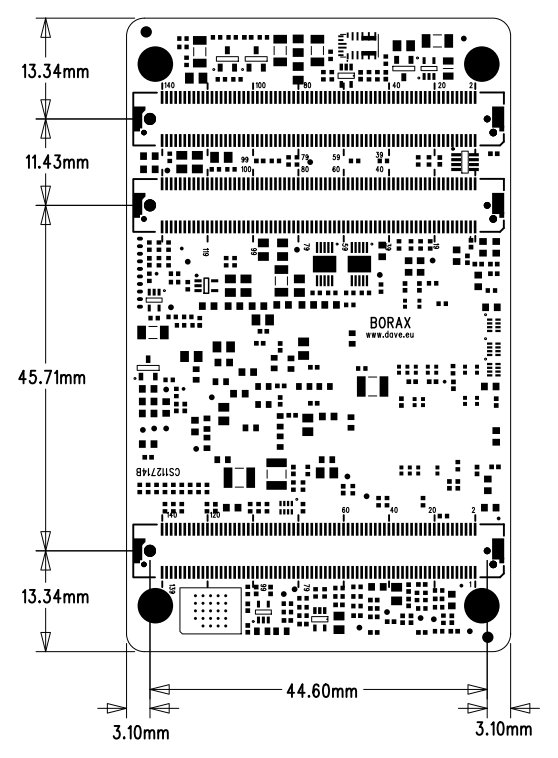

Mechanical specifications[edit | edit source]

This chapter describes the mechanical characteristics of the BORA Xpress module.

Board Layout[edit | edit source]

The following figure shows the physical dimensions (expressed in mm) of the BORA Xpress module:

The following figure highlights the maximum components' heights (expressed in mm) on BORA Xpress module:

Connectors[edit | edit source]

The following figure shows the BORA Xpress connector layout:

CAD drawings[edit | edit source]

- DXF (2D): BORA-Xpress-dxf.zip

- IDF (3D): BORA-Xpress-idf.zip

- STEP (3D): BORA-Xpress-stp.zip