MITO 8M SOM/MITO 8M Hardware/pdf

General Information[edit | edit source]

MITO 8M SOM Block Diagram[edit | edit source]

[[File:Mito-bd-1.0.0-300dpi.png|thumb|MITO 8M Block diagram|none]]

MITO 8M SOM TOP View[edit | edit source]

[[File:DMI-Mito-top.png|thumb|MITO 8M TOP View|none]]

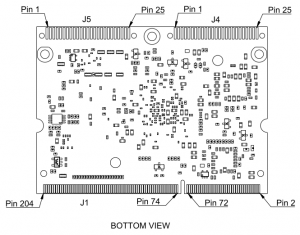

MITO 8M SOM BOTTOM View[edit | edit source]

[[File:DMI-Mito-bottom-300dpi.png|thumb|MITO 8M BOTTOM View|none]] {{#lst:MITO 8M SOM/MITO 8M Hardware/General Information/Processor and memory subsystem|Body}} {{#lst:MITO 8M SOM/MITO 8M Hardware/General Information/Hardware versioning and tracking|Body}} {{#lst:{{{nome-som}}} SOM/{{{nome-som}}} Hardware/SOM P/N composition|Body}}

Pinout Table[edit | edit source]

{{#lst:MITO 8M SOM/MITO 8M Hardware/Pinout Table |Body}}

Power and reset[edit | edit source]

{{#lst:MITO 8M SOM/MITO 8M Hardware/Power and Reset/Power Supply Unit (PSU) and recommended power-up sequence|Body}} {{#lst:MITO 8M SOM/MITO 8M Hardware/Power and Reset/Reset scheme and control signals|Body}} {{#lst:MITO 8M SOM/MITO 8M Hardware/Power and Reset/System boot|Body}} {{#lst:MITO 8M SOM/MITO 8M Hardware/Power and Reset/JTAG|Body}}

Peripherals[edit | edit source]

Peripheral Audio[edit | edit source]

The Audio interface available on MITO 8M is based on iMX8M SoC which provides the following audio subsystems:

- Synchronous Audio Interface (SAI)

- 6x I2S/SAI (20+ channels, each 32-bits @384 kHz)

- Highest levels of pro audio fidelity with more than 20 audio channels each @384KHz

- Sony/Philips Digital Interface (SPDIF)

- S/PDIF Tx/Rx

Description[edit | edit source]

The I2S (or I2S) module provides a synchronous audio interface (SAI) that supports full- duplex serial interfaces with frame synchronization such as I2S, AC97, TDM, and codec/DSP interfaces. It supports the following standards and features:

- Transmitter and receiver with independent bit clock and frame sync supporting 8 data lines

- Each data line can support a maximum Frame size of 32 words

- Asynchronous 128 x 32-bit FIFO for each transmit and receive data line

- Supports packing of 8-bit and 16-bit data into each 32-bit FIFO word

- Supports combining multiple data line FIFOs into single data line FIFO

The Sony/Philips Digital Interface (SPDIF) audio block is a stereo transceiver that allows the processor to receive and transmit digital audio.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral Ethernet[edit | edit source]

Description[edit | edit source]

The 10/100/1000-Mbit/s Ethernet interface available on MITO 8M is based on iMX8M SoC.

The SOC is directly interfaced with an ETH PHY chip (MICROCHIP KSZ9031RNX) that has the following features:

- Auto-Negotiation to Automatically Select the Highest Link-Up Speed (10/100/1000 Mbps) and Duplex (Half/Full)

- On-Chip Termination Resistors for the Differential Pairs

- Energy Detect Power-Down Mode for Reduced Power Consumption When the Cable is Not Attached

Important note for the external magnetic connection[edit | edit source]

The Ethernet peripheral requires an external insulator magnetic on the carrier board.

The four transformer center tap pins on the PHY side should not be connected to any power supply source on the board; rather, the center tap pins should be separated from one another and connected through separate 0.1 µF common-mode capacitors to ground. Separation is required because the common-mode voltage could be different between the four differential pairs, depending on the connected speed mode.

See KSZ9031RNX datasheet for more details.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral HDMI[edit | edit source]

HDMI (High-Definition Multimedia Interface) is a compact audio/video interface for transmitting uncompressed digital video data and uncompressed/compressed digital audio data.

HDMI connects digital audio/video sources-such as set-top boxes, Blu-ray Disc players, personal computers (PCs), video game consoles, and AV receivers to compatible digital audio devices, computer monitors, and digital televisions.

Description[edit | edit source]

The HDMI interface available on MITO 8M is based on iMX8M SoC.

The HDMI port supports the following standards and features:

- High-Definition Multimedia Interface Specification, Version up to 2.0a

- Compliant with HDCP2.2 (and back compatible with HDCP1.3/HDCP1.4)

- Variety of video resolutions and formats

- Supports up to 4k2k at 60Hz resolution

- Supports 8, 10, 12, and 16bpp

- Supports RGB, YCbCr422 formats

- Variety of audio formats – PCM and compressed, over I2S interface

- I2S PCM samples are converted to comply with IEC60958 sub-frames

- Supporting I2S-TDM

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral LVDS[edit | edit source]

The LVDS interface available on MITO 8M is based on a MIPI® DSI To FLATLINK™ LVDS bridge IC.

It is directly connected to the MIPI® DSI output port of iMX8M SOC.

This support covers all aspects of these activities:

- Connectivity to relevant devices - Displays with LVDS receivers

- Arranging the data as required by the external display receiver and by LVDS display standards

- Synchronization and control capabilities

Description[edit | edit source]

The LVDS port supports the following standards and features:

- Suitable for 60-fps WUXGA 1920 × 1200 Resolution at 18-bpp and 24-bpp Color, 60 fps 1366 × 768 at 18 bpp and 24 bpp

- Output Configurable for Single-Link or Dual-Link LVDS

- LVDS Output Clock Range of 25 MHz to 154 MHz in Dual-Link or Single-Link Modes

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral MIPI[edit | edit source]

The MIPI interfaces available on iMX8M SoC are following described:

- The Camera Serial Interface (CSI) is a specification of the Mobile Industry Processor Interface (MIPI) Alliance. It defines an interface between a camera and a host processor.

- The Display Serial Interface (DSI) is a specification by the Mobile Industry Processor Interface (MIPI) Alliance aimed at reducing the cost of display controllers in a mobile device. It is commonly targeted at LCD and similar display technologies.

The two CSI interface on MITO 8M SOM:

- CSI1 is avaiable on SODIMM connector pinout

- CSI2 is avaiable on ONE PIECE expansion connector J5

The DSI interface is internally used on MITO 8M SOM to generate an LVDS output interface. More details on LVDS section.

Description[edit | edit source]

The MIPI CSI port supports the following standards and features:

- Configurable interface logic to support most commonly available CMOS sensors.

- Scalable data lane support, 1 to 4 Data Lanes

- Support for CCIR656 video interface as well as traditional sensor interface.

- 8-bit / 16-bit / 24-bit data port for YCbCr, YUV, or RGB data input.

- 8-bit / 10-bit / 16-bit data port for Bayer data input.

- Implements all three CSI-2 MIPI layers (Pixel to byte packing, low level protocol, Lane management)

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral SDIOs[edit | edit source]

The Ultra Secured Digital Host Controller (uSDHC) provides the interface between the host system and the SD/SDIO/MMC cards or devices.

MITO 8M SOM provides up to two SDIO interface available for an external memory device connection.

The availability of this interface is related to the SOM mounting option:

- on NAND on board version, the NAND interface is internally connected, and the SD1 interface is routed externally the SOM

- on eMMC on board version, the SD1 interface is internally connected, and the NAND interface is routed externally the SOM

See Pin mapping tables for connection details.

Description[edit | edit source]

The SDIOs interface available on MITO 8M is based on iMX8M SoC.

The SDIOs port supports the following standards and features:

- Conforms to the SD Host Controller Standard Specification version 2.0/3.0

- Compatible with the MMC System Specification version 4.2/4.3/4.4/4.41/5.0/5.1

- Compatible with the SD Memory Card Specification version 3.0 and supports the Extended Capacity SD Memory Card

- Compatible with the SDIO Card Specification version 2.0/3.0

- Supports 1-bit/4-bit SD and SDIO modes, and 1-bit/4-bit/8-bit MMC modes

- Card bus clock frequency up to 208 MHz

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral UARTs[edit | edit source]

Description[edit | edit source]

The Universal Asynchronous Receiver/Transmitter (UART) interface available on MITO 8M is based on iMX8M SoC.

UARTs provides serial communication capability with external devices and support NRZ encoding format, RS485 compatible 9 bit data format and IrDA-compatible infrared slow data rate (SIR) format.

The UART port supports the following standards and features:

- High-speed TIA/EIA-232-F compatible, up to Mbit/s

- Serial IR interface low-speed, IrDA-compatible (up to 115.2 Kbit/s)

- 9-bit or Multidrop mode (RS-485) support (automatic slave address detection)

- 7 or 8 data bits for RS-232 characters, or 9 bit RS-485 format

- 1 or 2 stop bits

- Programmable parity (even, odd, and no parity)

- Hardware flow control support for request to send (RTS_B) and clear to send (CTS_B) signals

- Two independent, 32-entry FIFOs for transmit and receive

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral USB[edit | edit source]

Universal Serial Bus (USB) is an industry standard that establishes specifications for cables and connectors and protocols for connection, communication and power supply (interfacing) between computers, peripherals and other computers.

Description[edit | edit source]

The two USB interface available on MITO 8M are based on iMX8M SoC.

Each USB 3.0-compliant serial interface port supports the following standards and features:

- USB dual-role operation and can be configured as host or device

- Super-speed (5 Gbit/s), high-speed (480 Mbit/s), full-speed (12 Mbit/s), and low-speed (1.5 Mbit/s) operations.

- OTG (on-the-go) 2.0 compliant, which includes both device and host capability. Super-speed operation is not supported when OTG is enabled.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral PCI Express[edit | edit source]

PCI Express (Peripheral Component Interconnect Express) is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards.

The two PCI Express interface on MITO 8M SOM:

- PCIe1 is avaiable on SODIMM connector pinout

- PCIe2 is avaiable on ONE PIECE expansion connector J5

Description[edit | edit source]

The PCI Express interfaces available on MITO 8M is based on iMX8M SoC.

The PCI Express interfaces supports the following standards and features:

- two PCIe PHY ports (1-lines each)

- up to 6.0 Gbps data rate

- complies to PCI Express base specification 2.1.

- 8B/10B Encoding / Decoding

- Supports Spread Spectrum Clocking in Transmitter and Receiver

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Peripheral GPIOs[edit | edit source]

The GPIO general-purpose input/output peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs.

Description[edit | edit source]

When configured as an output, it is possible to write to an internal register to control the state driven on the output pin. When configured as an input, it is possible to detect the state of the input by reading the state of an internal register. In addition, the GPIO peripheral can produce CORE interrupts.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Real Time Clock[edit | edit source]

This chapter describes the technical specifications and features for the RTC component on the MITO 8M module.

The Real Time Clock available on MITO 8M is based on iMX8M SoC.

Features[edit | edit source]

The MITO 8M module uses a 32.768kHz dedicated crystal in order to obtain an accurate time base for the RTC.

Important note for RTC during power-off[edit | edit source]

On the MITO 8M module the SNVS voltage rails are obtained by the main supply of the SOM.

For this reason, there is no possibility to keep operative the CPU RTC when the SOM is not connected to the 3.3VIN power rail.

Use an external RTC with battery backup functionality if required.

Peripheral Watchdog[edit | edit source]

The Watchdog Timer (WDOG) protects against system failures by providing a method by which to escape from unexpected events or programming errors.

Description[edit | edit source]

By default, the Watchdog Timer of iMX8M SOC is internally used on MITO 8M for the CPU-initiated software reset function.

For more details see the reset scheme and control signals section.

Pin mapping[edit | edit source]

The Pin mapping is described in the Pinout table section

Electrical, Thermal and Mechanical Features[edit | edit source]

Operational characteristics[edit | edit source]

Maximum ratings[edit | edit source]

| Parameter | Min | Typ | Max | Unit |

|---|---|---|---|---|

| Main power supply voltage | 0 | 3.3 | 3.6 | V |

Recommended ratings[edit | edit source]

| Parameter | Min | Typ | Max | Unit |

|---|---|---|---|---|

| Main power supply voltage | 3.135 | 3.3 | 3.465 | V |

Power consumption[edit | edit source]

Providing theoretical maximum power consumption value would be useless for the majority of system designers building their application upon MITO 8M module. Practically speaking, these figures would be of no help when it comes to size power supply unit or to perform thermal design of real systems.

Instead, several configurations have been tested in order to provide figures that are measured on real-world use cases.

Please note that MITO 8M platform is so flexible that it is virtually impossible to test for all possible configurations and applications on the market. The use cases here presented should cover most of real-world scenarios. However actual customer's application might require more power than values reported here or customer's use case may be differ significantly with respect to the ones here considered.

Therefore, application-specific requirements have always to be taken into consideration in order to size power supply unit and to implement thermal management properly.

Use cases results[edit | edit source]

Measurements have been performed on the MITO 8M SOM under test is equipped with:

| Section not completed yet |

| Checkpoint | Power (mW) |

|---|---|

| U-boot prompt | xxxx |

| Linux prompt | xxxx |

| Stress App test (*) | xxxx |

(*) Stressful Application Test: https://github.com/stressapptest/stressapptest

Thermal management[edit | edit source]

The MITO 8M SOM is designed to support the maximum available temperature range declared by the manufacturer.

The customer shall define and conduct a reasonable number of tests and verification in order to qualify the DUT capabilities to manage the heat dissipation.

Any heatsink, fan etc shall be defined case by case.

DAVE Embedded Systems' team is available for any additional information, please contact sales@dave.eu.

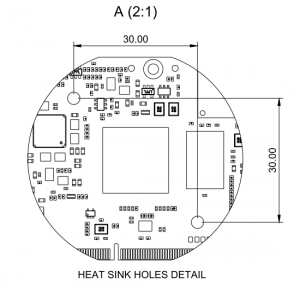

Heatsink suggestion[edit | edit source]

The MITO 8M SOM is designed with two holes that allow to mount a heatsink directly on the CPU IC.

Suggested part are ATS Push Pin Heat Sinks CPX0250250xx or FPX0250250xx part numbers.

See ATS website for more details [1].

Software thermal protection[edit | edit source]

In DESK-MX8-L, two software thermal protection mechanisms are implemented. Both are based on the processor's temperature sensor. It is worth remembering that maximum junction temperature (also denoted as Tj in the rest of the document) is:

- 95°C for Consumer parts

- 105°C for Industrial parts

| Section not completed yet |

U-Boot[edit | edit source]

At U-Boot level, automatic boot procedure is halted until Tj is smaller than (following temperatures might seem excessively low but they take into account the intrinsic poor precision of the temperature sensor to provide a reasonable safe margin):

- TBD for Consumer parts

- 95°C for Industrial parts

Linux kernel[edit | edit source]

At Linux level, a more sophisticated protection mechanism is implemented. Please refer to the following sections for more details.

The default temperature thresholds depend on the silicon grade, as follows:

- for Consumer parts

- passive threshold: TBD

- critical threshold: TBD

- for Industrial parts

- passive threshold: 85°C

- critical threshold: 95°C

Practically speaking, for DESK-MX8-L this mechanism makes use of two different thresholds, denoted as trip_point0 (also known as passive threshold) and trip_point1 (also known as critical threshold).

When Tj reaches trip_point0, Linux kernel scales down processor frequency.

If Tj reaches trip_point1, a complete shutdown is triggered:

thermal thermal_zone0: critical temperature reached(95 C),shutting down

By default, temperature thresholds are set up as follows:

trip_point0: 85°Ctrip_point1: 95°C.

Trip point thresholds can be accessed via sysfs interface from user space. The following example shows how to read the values of the trip points:

root@mito:~# cat /sys/devices/virtual/thermal/thermal_zone0/trip_point_0_temp 85000 root@mito:~# cat /sys/devices/virtual/thermal/thermal_zone0/trip_point_1_temp 950000

This example shows how to set trip points 0 and 1 to 95°C and 100°C respectively:

echo 95000 > /sys/class/thermal/thermal_zone0/trip_point_0_temp echo 100000 > /sys/class/thermal/thermal_zone0/trip_point_1_temp

Please note that:

- it is possible to set up trip points greater than the maximum junction temperature indicated by manufacturer datasheet;

- exceeding maximum junction temperature indicated by manufacturer datasheet may cause permanent damage.

To read current processor temperature please issue this command (reported temperature is 36.676°C in the example):

root@mito:~# cat /sys/class/thermal/thermal_zone0/temp 36676

For more details about this functionality, please refer to Documentation/thermal/sysfs-api.txt in the kernel sources.

Mechanical specifications[edit | edit source]

This chapter describes the mechanical characteristics of the MITO 8M module.

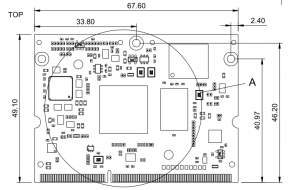

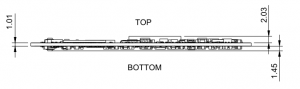

Board Layout[edit | edit source]

The following figure shows the physical dimensions of the MITO 8M module:

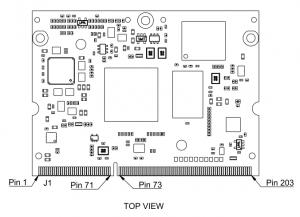

Connectors[edit | edit source]

The following figure shows the MITO 8M connector layout:

CAD drawings[edit | edit source]

- DXF (2D): CS031518.dxf

- STEP (3D): CS031518