MITO 8M Nano SOM/MITO 8M Nano Hardware/pdf

General Information[edit | edit source]

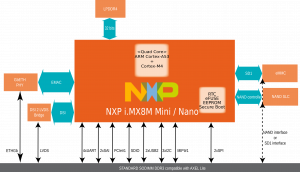

MITO 8M Nano Block Diagram[edit | edit source]

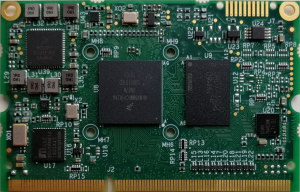

MITO 8M Nano TOP View[edit | edit source]

MITO 8M Nano BOTTOM View[edit | edit source]

Processor and memory subsystem[edit | edit source]

The heart of MITO 8M Nano module is composed by the following components:

- i.MX8M Nano SoC application processor

- Power supply unit

- LPDDR4 memory bank

- eMMC or NAND flash banks

- Connectors:

- 1 x 204 pins SO-DIMM edge connector with interfaces signals

- partially compatible with AXEL Lite SOM

- 1 x 204 pins SO-DIMM edge connector with interfaces signals

This chapter shortly describes the main MITO 8M Nano components.

Processor Info[edit | edit source]

| Processor | i.MX8M Nano Solo | i.MX8M Nano Dual | i.MX8M Nano Quad |

| # Cores | 1x Arm® Cortex®-A53

1x Arm® Cortex®-M7 |

2x Arm® Cortex®-A53

1x Arm® Cortex®-M7 |

4x Arm® Cortex®-A53

1x Arm® Cortex®-M7 |

| Clock | 1.4 GHz (Industrial) 1.5 GHz (Commercial) | ||

| L2

Cache |

1 MB | ||

| LPDDR4 | 16 bit @ 1600 MHz

(LPDDR4-3200) | ||

| GPU | Vivante GC 7000UL (2 Shader)

OpenGL ES 3.1 | ||

| Display

Controller |

Dual Independent LVDS channel

Display Support up to 1080p60 | ||

| Video

Output |

1x MIPI-DSI (with MIPI to LVDS bridge) | ||

| Camera

Input |

1x MIPI CSI (4-lanes) | ||

| USB | 2x USB 2.0 OTG | ||

RAM memory bank[edit | edit source]

LPDD4 SDRAM memory bank is composed by 1x 16-bit width chip. The following table reports the SDRAM specifications:

| CPU connection | Multi-mode DDR controller (MMDC) |

| Size max | 4 GB |

| Width | 16 bit |

| Speed | 1600 MHz |

eMMC flash bank[edit | edit source]

On board main storage memory eMMC is connected to the SDIO1 interface and it can act as boot peripheral. The following table reports the eMMC flash specifications:

| CPU connection | SDIO1 |

| Size min | 4 GB |

| Size max | 64 GB |

| Bootable | Yes |

NAND flash bank[edit | edit source]

| Not available yet |

Alternative option for main storage memory can be a 8-bit wide NAND flash connected to the CPU's Raw NAND flash controller. It can act as boot peripheral. The following table reports the NAND flash specifications:

| CPU connection | Raw NAND flash controller |

| Page size | 512 byte, 2 kbyte or 4 kbyte |

| Size min | 512MB |

| Size max | 2GB |

| Width | 8 bit |

| Chip select | NANC_CE0 |

| Bootable | Yes |

Memory map[edit | edit source]

For detailed information, please refer to chapter 2 “Memory Maps” of the i.MX8M Nano Applications Processor Reference Manual

Power supply unit[edit | edit source]

MITO 8M Nano embeds all the elements required for powering the unit, therefore power sequencing is self-contained and simplified. Nevertheless, power must be provided from carrier board, and therefore users should be aware of the ranges power supply can assume as well as all other parameters.

Part number composition[edit | edit source]

MITO 8M Nano SOM module part number is identified by the following digit-code table:

| Part number structure | Options | Description |

|---|---|---|

| Family | DMN | Family prefix code |

| SOC |

|

Other versions can be available, please contact technical support |

| RAM Flash |

|

|

| Storage |

|

NAND SLC and eMMC are possible alternatives not available together. Other sizes can be available, please contact technical support |

| Boot options |

|

These options depend on storage version selected. Other versions can be available, please contact technical support |

| VIN Range |

|

|

| RFU | Reserved for Future Use | |

| Temperature range |

|

For the DAVE Embedded Systems' product Temperature Range classification, please find more information at the page Products Classification |

| PCB revision |

|

PCB release may change for manufacturing purposes (i.e. text fixture adaptation) |

| Manufacturing option |

|

|

| Software Configuration |

|

If customers require custom SW deployed this section should be defined and agreed. please contact technical support |

Example[edit | edit source]

MITO 8M Nano SOM code DMNA22000C0R-00

- DMN - MITO 8M Nano

- A - NXP i.MX8M Nano Quad Industrial grade (Tj: -40/105°C) @ 1.4GHz

- 2 - 2GB DDR4

- 2 - 4GB eMMC

- 0 - Boot from on board eMMC

- 0 - 3.3V fixed

- 0 - RFU

- C - Commercial grade: for 0-70°C

- 0 - first version

- R - RoHS

- -00 - standard factory u-boot pre-programmed

Pinout Table[edit | edit source]

Connectors and Pinout Table description[edit | edit source]

Connectors description[edit | edit source]

In the following table are described all available connectors integrated on MITO 8M Nano SOM:

| Connector name | Connector Type | Notes | Carrier board counterpart |

|---|---|---|---|

| J1 | SODIMM edge connector 204 pin | partially compatible with AXEL Lite SOM | TE Connectivity 2-2013289-1 |

The dedicated carrier board must mount the mating connector and connect the desired peripheral interfaces according to MITO 8M Nano pinout specifications. See the images below for reference:

Below a detailed description of the pinout, grouped in the following tables:

- two tables (ODD and EVEN pins) that report the pin mapping of the 204-pin SO-DIMM edge

Pinout Table description[edit | edit source]

Each row in the pinout tables contains the following information:

| Pin | Reference to the connector pin |

| Pin Name | Pin (signal) name on the MITO 8M Nano connectors |

| Internal connections |

Connections to the components

|

| Ball/pin # | Component ball/pin number connected to signal |

| Voltage | I/O voltage levels |

| Type | Pin type:

|

| Notes | Remarks on special pin characteristics |

| Pin MUX alternative functions | Muxes:

|

SODIMM J1 ODD pins declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Voltage domain | Type | Notes | Alternative Functions | |

|---|---|---|---|---|---|---|---|---|

| J1.1 | DGND | DGND | - | - | G | |||

| J1.3 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.5 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.7 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.9 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.11 | DGND | DGND | - | - | G | |||

| J1.13 | ETH0_LED1 | LAN.LED1/PME_N1 | 17 | NVCC_1V8 | I/O | Must be level translated if used @ 3V3

Internally pulled-up to 1.8V during bootstrap |

||

| J1.15 | ETH0_LED2 | LAN.LED2 | 15 | NVCC_1V8 | I/O | Must be level translated if used @ 3V3

Internally pulled-up to 1.8V during bootstrap |

||

| J1.17 | DGND | DGND | - | - | G | |||

| J1.19 | ETH0_TXRX0_P | LAN.TXRXP_A | 2 | - | D | |||

| J1.21 | ETH0_TXRX0_M | LAN.TXRXM_A | 3 | - | D | |||

| J1.23 | ETH0_TXRX1_P | LAN.TXRXP_B | 5 | - | D | |||

| J1.25 | ETH0_TXRX1_M | LAN.TXRXM_B | 6 | - | D | |||

| J1.27 | ETH0_TXRX2_P | LAN.TXRXP_C | 7 | - | D | |||

| J1.29 | ETH0_TXRX2_M | LAN.TXRXM_C | 8 | - | D | |||

| J1.31 | ETH0_TXRX3_P | LAN.TXRXP_D | 10 | - | D | |||

| J1.33 | ETH0_TXRX3_M | LAN.TXRXM_D | 11 | - | D | |||

| J1.35 | DGND | DGND | - | - | G | |||

| J1.37 | GPIO1_IO00 | CPU.GPIO1_IO00 | AG14 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO00 | |

| ALT1 | CCM_ENET_PHY_REF_CLK_ROOT | |||||||

| ALT5 | CCM_REF_CLK_32K | |||||||

| ALT6 | CCM_EXT_CLK1 | |||||||

| J1.39 | GPIO1_IO01 | CPU.GPIO1_IO01 | AF14 | NVCC_3V3 | I/O | Internally used for ETH PHY reset, do not connect | ALT0 | GPIO1_IO01 |

| ALT1 | PWM1_OUT | |||||||

| ALT5 | CCM_REF_CLK_24M | |||||||

| ALT6 | CCM_EXT_CLK2 | |||||||

| J1.41 | SPDIF_EXT_CLK | CPU.SPDIF_EXT_CLK | AF8 | NVCC_3V3 | I/O | ALT0 | SPDIF1_EXT_CLK | |

| ALT1 | PWM1_OUT | |||||||

| ALT5 | GPIO5_IO05 | |||||||

| J1.43 | GPIO1_IO13 | CPU.GPIO1_IO13 | AD9 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO13 | |

| ALT1 | USB1_OTG_OC | |||||||

| ALT5 | PWM2_OUT | |||||||

| J1.45 | GPIO1_IO11 | CPU.GPIO1_IO11 | AC10 | NVCC_3V3 | I/O | Internally used for ETH CLK enable, do not connect | ALT0 | GPIO1_IO11 |

| ALT1 | USB1_OTG_ID | |||||||

| J1.47 | ECSPI2_SCLK | CPU.ECSPI2_SCLK | E6 | NVCC_3V3 | I/O | ALT0 | ECSPI2_SCLK | |

| ALT1 | UART4_RX | |||||||

| ALT5 | GPIO5_IO10 | |||||||

| J1.49 | ECSPI2_MOSI | CPU.ECSPI2_MOSI | B8 | NVCC_3V3 | I/O | ALT0 | ECSPI2_MOSI | |

| ALT1 | UART4_TX | |||||||

| ALT5 | GPIO5_IO11 | |||||||

| J1.51 | GPIO1_IO08 | CPU.GPIO1_IO08 | AG10 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO08 | |

| ALT1 | ENET1_1588_EVENT0_IN | |||||||

| ALT5 | USDHC2_RESET_B | |||||||

| J1.53 | GPIO1_IO09 | CPU.GPIO1_IO09 | AF10 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO09 | |

| ALT1 | ENET1_1588_EVENT0_OUT | |||||||

| ALT4 | USDHC3_RESET_B | |||||||

| ALT5 | SDMA2_EXT_EVENT0 | |||||||

| J1.55 | ECSPI2_MISO | CPU.ECSPI2_MISO | A8 | NVCC_3V3 | I/O | ALT0 | ECSPI2_MISO | |

| ALT1 | UART4_CTS_B | |||||||

| ALT5 | GPIO5_IO12 | |||||||

| J1.57 | DGND | DGND | - | - | G | |||

| J1.59 | ECSPI2_SS0 | CPU.ECSPI2_SS0 | A6 | NVCC_3V3 | I/O | ALT0 | ECSPI2_SS0 | |

| ALT1 | UART4_RTS_B

(Configure register IOMUXC_UART4_RTS_B_SELECT_INPUT for mode ALT1) | |||||||

| ALT5 | GPIO5_IO13 | |||||||

| J1.61 | GPIO1_IO05 | CPU.GPIO1_IO05 | AF12 | NVCC_3V3 | I/O | Internally used for MIPI-to-LVDS interrupt, do not connect

Pulled-up to NVCC_3V3 |

ALT0 | GPIO1_IO05 |

| ALT1 | M4_NMI | |||||||

| ALT5 | CCM_PMIC_READY | |||||||

| J1.63 | SAI5_RXD0 | CPU.SAI5_RXD0 | AD18 | NVCC_3V3 | I/O | ALT0 | SAI5_RX_DATA0

( Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_0 for mode ALT0) | |

| ALT1 | SAI1_TX_DATA2 | |||||||

| ALT4 | PDM_BIT_STREAM0

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_0 for mode ALT4) | |||||||

| ALT5 | GPIO3_IO21 | |||||||

| J1.65 | SAI5_RXD1 | CPU.SAI5_RXD1 | AC14 | NVCC_3V3 | I/O | ALT0 | SAI5_RX_DATA1

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_1 for mode ALT0) | |

| ALT1 | SAI1_TX_DATA3 | |||||||

| ALT2 | SAI1_TX_SYNC

(Configure register IOMUXC_SAI1_TX_SYNC_SELECT_INPUT for mode ALT2) | |||||||

| ALT3 | SAI5_TX_SYNC

(Configure register IOMUXC_SAI5_TX_SYNC_SELECT_INPUT for mode ALT3) | |||||||

| ALT4 | PDM_BIT_STREAM1

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_1 for mode ALT4) | |||||||

| ALT5 | GPIO3_IO22 | |||||||

| J1.67 | GPIO1_IO06 | CPU.GPIO1_IO06 | AG11 | NVCC_3V3 | I/O | Internally used for MIPI-to-LVDS enable, do not connect | ALT0 | GPIO1_IO06 |

| ALT1 | ENET1_MDC | |||||||

| ALT5 | USDHC1_CD_B | |||||||

| ALT6 | CCM_EXT_CLK3 | |||||||

| J1.69 | SAI2_RXC | CPU.SAI2_RXC | AB22 | NVCC_3V3 | I/O | ALT0 | SAI2_RX_BCLK | |

| ALT1 | SAI5_TX_BCLK

(Configure register IOMUXC_SAI5_TX_BCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT4 | UART1_RX | |||||||

| ALT5 | GPIO4_IO22 | |||||||

| J1.71 | SAI2_RXFS | CPU.SAI2_RXFS | AC19 | NVCC_3V3 | I/O | ALT0 | SAI2_RX_SYNC | |

| ALT1 | SAI5_TX_SYNC

(Configure register IOMUXC_SAI5_TX_SYNC_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | SAI5_TX_DATA1 | |||||||

| ALT3 | SAI2_RX_DATA1 | |||||||

| ALT4 | UART1_TX | |||||||

| ALT5 | GPIO4_IO21 | |||||||

| J1.73 | DGND | DGND | - | - | G | |||

| J1.75 | SD2_DATA0 | CPU.SD2_DATA0 | AB23 | NVCC_3V3 | I/O | ALT0 | USDHC2_DATA0 | |

| ALT5 | GPIO2_IO15 | |||||||

| J1.77 | SD2_DATA1 | CPU.SD2_DATA1 | AB24 | NVCC_3V3 | I/O | ALT0 | USDHC2_DATA1 | |

| ALT5 | GPIO2_IO16 | |||||||

| J1.79 | SD2_DATA2 | CPU.SD2_DATA2 | V24 | NVCC_3V3 | I/O | ALT0 | USDHC2_DATA2 | |

| ALT5 | GPIO2_IO17 | |||||||

| J1.81 | SD2_DATA3 | CPU.SD2_DATA03 | V23 | NVCC_3V3 | I/O | ALT0 | USDHC2_DATA3 | |

| ALT5 | GPIO2_IO18 | |||||||

| J1.83 | SD2_CMD | CPU.SD2_CMD | W24 | NVCC_3V3 | I/O | ALT0 | USDHC2_CMD | |

| ALT5 | GPIO2_IO14 | |||||||

| J1.85 | SD2_CLK | CPU.SD2_CLK | W23 | NVCC_3V3 | I/O | ALT0 | USDHC2_CLK | |

| ALT5 | GPIO2_IO13 | |||||||

| J1.87 | DGND | DGND | - | - | G | |||

| J1.89 | UART3_TXD | CPU.UART3_TXD | D18 | NVCC_3V3 | I/O | Internally pulled-up to NVCC_3V3 | ALT0 | UART3_TX |

| ALT1 | UART1_RTS_B

(Configure register IOMUXC_UART1_RTS_B_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | USDHC3_VSELECT | |||||||

| ALT5 | GPIO5_IO27 | |||||||

| J1.91 | UART3_RXD | CPU.UART3_RXD | E18 | NVCC_3V3 | I/O | ALT0 | UART3_RX | |

| ALT1 | UART1_CTS_B | |||||||

| ALT2 | USDHC3_RESET_B | |||||||

| ALT5 | GPIO5_IO26 | |||||||

| J1.93 | UART1_TXD | CPU.UART1_TXD | F13 | NVCC_3V3 | I/O | ALT0 | UART1_TX | |

| ALT1 | ECSPI3_MOSI | |||||||

| ALT5 | GPIO5_IO23 | |||||||

| J1.95 | UART1_RXD | CPU.UART1_RXD | E14 | NVCC_3V3 | I/O | ALT0 | UART1_RX | |

| ALT1 | ECSPI3_SCLK | |||||||

| ALT5 | GPIO5_IO22 | |||||||

| J1.97 | SD2_WP | CPU.SD2_WP | AA27 | NVCC_3V3 | I/O | ALT0 | USDHC2_WP | |

| ALT5 | GPIO2_IO20 | |||||||

| J1.99 | SD2_RST_B | CPU.SD2_RESET_B | AB26 | NVCC_3V3 | I/O | ALT0 | USDHC2_RESET_B | |

| ALT5 | GPIO2_IO19 | |||||||

| J1.101 | I2C2_SCL | CPU.I2C2_SCL | D10 | NVCC_3V3 | I/O | ALT0 | I2C2_SCL | |

| ALT1 | ENET1_1588_EVENT1_IN | |||||||

| ALT2 | USDHC3_CD_B

(Configure register IOMUXC_USDHC3_CD_B_SELECT_INPUT for mode ALT2) | |||||||

| ALT5 | GPIO5_IO16 | |||||||

| J1.103 | I2C2_SDA | CPU.I2C2_SDA | D9 | NVCC_3V3 | I/O | ALT0 | I2C2_SDA | |

| ALT1 | ENET1_1588_EVENT1_OUT | |||||||

| ALT2 | USDHC3_WP

(Configure register IOMUXC_USDHC3_WP_SELECT_INPUT for mode ALT2) | |||||||

| ALT5 | GPIO5_IO17 | |||||||

| J1.105 | SAI1_RXD3 | CPU.SAI1_RXD3 | AF17 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA3 |

| ALT1 | SAI5_RX_DATA3

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_3 for mode ALT1) | |||||||

| ALT3 | PDM_BIT_STREAM3

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_3 for mode ALT3) | |||||||

| ALT4 | CORESIGHT_TRACE3 | |||||||

| ALT5 | GPIO4_IO05 | |||||||

| ALT6 | SRC_BOOT_CFG3 | |||||||

| J1.107 | SAI1_TXD3 | CPU.SAI1_TXD3 | AF21 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA3 |

| ALT1 | SAI5_TX_DATA3 | |||||||

| ALT4 | CORESIGHT_TRACE11 | |||||||

| ALT5 | GPIO4_IO15 | |||||||

| ALT6 | SRC_BOOT_CFG11 | |||||||

| J1.109 | DGND | DGND | - | - | G | |||

| J1.111 | SAI1_TXFS | CPU.SAI1_TXFS | AB19 | NVCC_3V3 | I/O | ALT0 | SAI1_TX_SYNC

(Configure register IOMUXC_SAI1_TX_SYNC_SELECT_INPUT for mode ALT0) | |

| ALT1 | SAI5_TX_SYNC

(Configure register IOMUXC_SAI5_TX_SYNC_SELECT_INPUT for mode ALT1) | |||||||

| ALT4 | CORESIGHT_EVENTO | |||||||

| ALT5 | GPIO4_IO10 | |||||||

| J1.113 | SAI1_TXC | CPU.SAI1_TXC | AC18 | NVCC_3V3 | I/O | ALT0 | SAI1_TX_BCLK

(Configure register IOMUXC_SAI1_TX_BCLK_SELECT_INPUT for mode ALT0) | |

| ALT1 | SAI5_TX_BCLK

(Configure register IOMUXC_SAI5_TX_BCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT4 | CORESIGHT_EVENTI | |||||||

| ALT5 | GPIO4_IO11 | |||||||

| J1.115 | SAI1_TXD0 | CPU.SAI1_TXD0 | AG20 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA0 |

| ALT1 | SAI5_TX_DATA0 | |||||||

| ALT4 | CORESIGHT_TRACE8 | |||||||

| ALT5 | GPIO4_IO12 | |||||||

| ALT6 | SRC_BOOT_CFG8 | |||||||

| J1.117 | SAI1_TXD1 | CPU.SAI1_TXD1 | AF20 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA1 |

| ALT1 | SAI5_TX_DATA1 | |||||||

| ALT4 | CORESIGHT_TRACE9 | |||||||

| ALT5 | GPIO4_IO13 | |||||||

| ALT6 | SRC_BOOT_CFG9 | |||||||

| J1.119 | SAI1_TXD2 | CPU.SAI1_TXD2 | AG21 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA2 |

| ALT1 | SAI5_TX_DATA2 | |||||||

| ALT4 | CORESIGHT_TRACE10 | |||||||

| ALT5 | GPIO4_IO14 | |||||||

| ALT6 | SRC_BOOT_CFG10 | |||||||

| J1.121 | SAI1_RXFS | CPU.SAI1_RXFS | AG16 | NVCC_3V3 | I/O | ALT0 | SAI1_RX_SYNC

(Configure register IOMUXC_SAI1_RX_SYNC_SELECT_INPUT for mode ALT0) | |

| ALT1 | SAI5_RX_SYNC

(Configure register IOMUXC_SAI5_RX_SYNC_SELECT_INPUT for mode ALT1) | |||||||

| ALT4 | CORESIGHT_TRACE_CLK | |||||||

| ALT5 | GPIO4_IO00 | |||||||

| J1.123 | SAI1_RXC | CPU.SAI1_RXC | AF16 | NVCC_3V3 | I/O | ALT0 | SAI1_RX_BCLK | |

| ALT1 | SAI5_RX_BCLK

(Configure register IOMUXC_SAI5_RX_BCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT4 | CORESIGHT_TRACE_CTL | |||||||

| ALT5 | GPIO4_IO01 | |||||||

| J1.125 | SAI1_RXD0 | CPU.SAI1_RXD0 | AG15 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA0 |

| ALT1 | SAI5_RX_DATA0

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_0 for mode ALT1) | |||||||

| ALT2 | SAI1_TX_DATA1 | |||||||

| ALT3 | PDM_BIT_STREAM0

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_0 for mode ALT3) | |||||||

| ALT4 | CORESIGHT_TRACE0 | |||||||

| ALT5 | GPIO4_IO02 | |||||||

| ALT6 | SRC_BOOT_CFG0 | |||||||

| J1.127 | SAI1_RXD1 | CPU.SAI1_RXD1 | AF15 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA1 |

| ALT1 | SAI5_RX_DATA1

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_1 for mode ALT1) | |||||||

| ALT3 | PDM_BIT_STREAM1

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_1 for mode ALT3) | |||||||

| ALT4 | CORESIGHT_TRACE1 | |||||||

| ALT5 | GPIO4_IO03 | |||||||

| ALT6 | SRC_BOOT_CFG1 | |||||||

| J1.129 | SAI1_RXD2 | CPU.SAI1_RXD2 | AG17 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA2 |

| ALT1 | SAI5_RX_DATA2

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_2 for mode ALT1) | |||||||

| ALT3 | PDM_BIT_STREAM2

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_2 for mode ALT3) | |||||||

| ALT4 | CORESIGHT_TRACE2 | |||||||

| ALT5 | GPIO4_IO04 | |||||||

| ALT6 | SRC_BOOT_CFG2 | |||||||

| J1.131 | DGND | DGND | - | - | G | |||

| J1.133 | LVDS0_CLK_N | BRIDGE.A_CLKN | F9 | - | D

[Depending on MITO 8M Nano SOM P/N composition |

|||

| J1.133 | DSI_CLK_N | CPU.MIPI_DSI_CLK_N | A11 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.135 | LVDS0_CLK_P | BRIDGE.A_CLKP | F8 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.135 | DSI_CLK_P | CPU.MIPI_ | B11 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.137 | LVDS0_TX0_N | BRIDGE.A_Y0N | C9 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.137 | DSI_D0_N | CPU.MIPI_DSI_D0_N | A9 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.139 | LVDS0_TX0_P | BRIDGE.A_Y0P | C8 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.139 | DSI_D0_P | CPU.MIPI_DSI_D0_P | B9 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.141 | LVDS0_TX1_N | BRIDGE.A_Y1N | D9 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.141 | DSI_D1_N | CPU.MIPI_DSI_D1_N | A10 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.143 | LVDS0_TX1_P | BRIDGE.A_Y1P | D8 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.143 | DSI_D1_P | CPU.MIPI_DSI_D1_P | B10 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.145 | LVDS0_TX2_N | BRIDGE.A_Y2N | E9 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.145 | DSI_D2_N | CPU.MIPI_DSI_D2_N | A12 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.147 | LVDS0_TX2_P | BRIDGE.A_Y2P | E8 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.147 | DSI_D2_P | CPU.MIPI_DSI_D2_P | B12 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.149 | LVDS0_TX3_N | BRIDGE.A_Y3N | G9 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.149 | DSI_D3_N | CPU.MIPI_DSI_D3_N | A13 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.151 | LVDS0_TX3_P | BRIDGE.A_Y3P | G8 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.151 | DSI_D3_P | CPU.MIPI_DSI_D3_P | B13 | - | D | Depending on MITO 8M Nano SOM P/N composition | ||

| J1.153 | DGND | DGND | - | - | G | |||

| J1.155 | LVDS1_CLK_N | BRIDGE.B_CLKN | A6 | - | D | |||

| J1.157 | LVDS1_CLK_P | BRIDGE.B_CLKP | B6 | - | D | |||

| J1.159 | LVDS1_TX0_N | BRIDGE.B_Y0N | A3 | - | D | |||

| J1.161 | LVDS1_TX0_P | BRIDGE.B_Y0P | B3 | - | D | |||

| J1.163 | LVDS1_TX1_N | BRIDGE.B_Y1N | A4 | - | D | |||

| J1.165 | LVDS1_TX1_P | BRIDGE.B_Y1P | B4 | - | D | |||

| J1.167 | LVDS1_TX2_N | BRIDGE.B_Y2N | A5 | - | D | |||

| J1.169 | LVDS1_TX2_P | BRIDGE.B_Y2P | B5 | - | D | |||

| J1.171 | LVDS1_TX3_N | BRIDGE.B_Y3N | A7 | - | D | |||

| J1.173 | LVDS1_TX3_P | BRIDGE.B_Y3P | B7 | - | D | |||

| J1.175 | DGND | DGND | - | - | G | |||

| J1.177 | SD2_CD_B | CPU.SD2_CD_B | AA26 | NVCC_3V3 | I/O | ALT0 | USDHC2_CD_B | |

| ALT5 | GPIO2_IO12 | |||||||

| J1.179 | ECSPI1_SS0 | CPU.ECSPI1_SS0 | B6 | NVCC_3V3 | I/O | ALT0 | ECSPI1_SS0 | |

| ALT1 | UART3_RTS_B

(Configure register IOMUXC_UART3_RTS_B_SELECT_INPUT for mode ALT1) | |||||||

| ALT5 | GPIO5_IO09 | |||||||

| J1.181 | ECSPI1_SCLK | CPU.ECSPI1_SCLK | D6 | NVCC_3V3 | I/O | ALT0 | ECSPI1_SCLK | |

| ALT1 | UART3_RX | |||||||

| ALT5 | GPIO5_IO06 | |||||||

| J1.183 | ECSPI1_MISO | CPU.ECSPI1_MISO | A7 | NVCC_3V3 | I/O | ALT0 | ECSPI1_MISO | |

| ALT1 | UART3_CTS_B | |||||||

| ALT5 | GPIO5_IO08 | |||||||

| J1.185 | GPIO1_IO03 | CPU.GPIO1_IO03 | AF13 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO03 | |

| ALT1 | USDHC1_VSELECT | |||||||

| ALT5 | SDMA1_EXT_EVENT0 | |||||||

| J1.187 | UART2_TXD | CPU.UART2_TXD | E15 | NVCC_3V3 | I/O | used as default Linux console | ALT0 | UART2_TX |

| ALT1 | ECSPI3_SS0 | |||||||

| ALT5 | GPIO5_IO25 | |||||||

| J1.189 | UART2_RXD | CPU.UART2_RXD | F15 | NVCC_3V3 | I/O | used as default Linux console | ALT0 | UART2_RXD |

| ALT1 | ECSPI3_MISO | |||||||

| ALT5 | GPIO5_IO24 | |||||||

| J1.191 | UART4_TXD | CPU.UART4_TXD | F18 | NVCC_3V3 | I/O | ALT0 | UART4_TX | |

| ALT1 | UART2_RTS_B

(Configure register IOMUXC_UART2_RTS_B_SELECT_INPUT for mode ALT1) | |||||||

| ALT5 | GPIO5_IO29 | |||||||

| J1.193 | UART4_RXD | CPU.UART4_RXD | F19 | NVCC_3V3 | I/O | ALT0 | UART4_RX | |

| ALT1 | UART2_CTS_B | |||||||

| ALT5 | GPIO5_IO28 | |||||||

| J1.195 | ECSPI1_MOSI | CPU.ECSPI1_MOSI | B7 | NVCC_3V3 | I/O | ALT0 | ECSPI1_MOSI | |

| ALT1 | UART3_TX | |||||||

| ALT5 | GPIO5_IO07 | |||||||

| J1.197 | GPIO1_IO14 | CPU.GPIO1_IO14 | AC9 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO14 | |

| ALT1 | USB2_OTG_PWR | |||||||

| ALT4 | USDHC3_CD_B

(Configure register IOMUXC_USDHC3_CD_B_SELECT_INPUT for mode ALT4) | |||||||

| ALT5 | PWM3_OUT | |||||||

| ALT6 | CCM_CLKO1 | |||||||

| J1.199 | GPIO1_IO04 | CPU.GPIO1_IO04 | AG12 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO04 | |

| ALT1 | USDHC2_VSELECT | |||||||

| ALT5 | SDMA1_EXT_EVENT1 | |||||||

| J1.201 | GPIO1_IO12 | CPU.GPIO1_IO12 | AB10 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO12 | |

| ALT1 | USB1_OTG_PWR | |||||||

| ALT5 | SDMA2_EXT_EVENT1 | |||||||

| J1.203 | DGND | DGND | - | - | G | |||

SODIMM J1 EVEN pins declaration[edit | edit source]

| Pin | Pin Name | Internal Connections | Ball/pin # | Voltage domain | Type | Notes | Alternative Functions | |

|---|---|---|---|---|---|---|---|---|

| J1.2 | DGND | DGND | - | - | G | |||

| J1.4 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.6 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.8 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.10 | 3.3VIN | INPUT VOLTAGE | - | 3.3VIN | S | |||

| J1.12 | DGND | DGND | - | - | G | |||

| J1.14 | PMIC_LICELL | PMIC.LICELL | 46 | - | S | |||

| J1.16 | CPU_ONOFF | CPU.ONOFF | A25 | NVCC_SNVS_1V8 | I | internal pull-up 100k to NVCC_SNVS_1V8 | ||

| J1.18 | BOARD_PGOOD | - | - | NVCC_3V3 | O | |||

| J1.20 | BOOT_MODE_SEL | BOOT MODE SELECTION | - | NVCC_3V3 | I | internal pull-up to NVCC_3V3 | ||

| J1.22 | CPU_PORn | CPU.POR_B

PMIC.RESET_MCU |

B24

21 |

NVCC_SNVS_1V8 | I/O | internal pull-up 100k to NVCC_SNVS_1V8 | ||

| J1.24 | PMIC_PWRON | PMIC.PWRON | 22 | - | I | internal pull-up 100k to VIN | ||

| J1.26 | SAI3_RXC | CPU.SAI3_RXC | AG7 | NVCC_3V3 | I/O | ALT0 | SAI3_RX_BCLK | |

| ALT1 | GPT1_CLK | |||||||

| ALT2 | SAI5_RX_BCLK

(Configure register IOMUXC_SAI5_RX_BCLK_SELECT_INPUT for mode ALT2) | |||||||

| ALT4 | UART2_CTS_B | |||||||

| ALT5 | GPIO4_IO29 | |||||||

| J1.28 | GPIO1_IO02 | CPU.GPIO1_IO02 | AG13 | NVCC_3V3 | I/O | Internally used for PMIC WDI, do not connect | ALT0 | GPIO1_IO02 |

| ALT1 | WDOG1_WDOG_B | |||||||

| ALT5 | WDOG1_WDOG_ANY | |||||||

| ALT7 | SJC_DE_B | |||||||

| J1.30 | DGND | DGND | - | - | G | |||

| J1.32 | SAI3_RXD | CPU.SAI3_RXD | AF7 | NVCC_3V3 | I/O | ALT0 | SAI3_RX_DATA0 | |

| ALT1 | GPT1_COMPARE1 | |||||||

| ALT2 | SAI5_RX_DATA0

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_0 for mode ALT2) | |||||||

| ALT4 | UART2_RTS_B

(Configure register IOMUXC_UART2_RTS_B_SELECT_INPUT for mode ALT4) | |||||||

| ALT5 | GPIO4_IO30 | |||||||

| J1.34 | SAI2_MCLK | CPU.SAI2_MCLK | AD19 | NVCC_3V3 | I/O | ALT0 | SAI2_MCLK | |

| ALT1 | SAI5_MCLK

(Configure register IOMUXC_SAI5_MCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT5 | GPIO4_IO27 | |||||||

| J1.36 | SAI3_RXFS | CPU.SAI3_RXFS | AG8 | NVCC_3V3 | I/O | ALT0 | SAI3_RX_SYNC | |

| ALT1 | GPT1_CAPTURE1 | |||||||

| ALT2 | SAI5_RX_SYNC

(Configure register IOMUXC_SAI5_RX_SYNC_SELECT_INPUT for mode ALT2) | |||||||

| ALT3 | SAI3_RX_DATA1 | |||||||

| ALT5 | GPIO4_IO28 | |||||||

| J1.38 | I2C3_SCL | CPU.I2C3_SCL | E10 | NVCC_3V3 | I/O | ALT0 | I2C3_SCL | |

| ALT1 | PWM4_OUT | |||||||

| ALT2 | GPT2_CLK | |||||||

| ALT5 | GPIO5_IO18 | |||||||

| J1.40 | SAI3_TXFS | CPU.SAI3_TXFS | AC6 | NVCC_3V3 | I/O | ALT0 | SAI3_TX_SYNC | |

| ALT1 | GPT1_CAPTURE2 | |||||||

| ALT2 | SAI5_RX_DATA1

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_1 for mode ALT2) | |||||||

| ALT3 | SAI3_TX_DATA1 | |||||||

| ALT4 | UART2_RX | |||||||

| ALT5 | GPIO4_IO31 | |||||||

| J1.42 | SPDIF_RX | CPU.SPDIF_RX | AG9 | NVCC_3V3 | I/O | ALT0 | SPDIF1_IN | |

| ALT1 | PWM2_OUT | |||||||

| ALT5 | GPIO5_IO04 | |||||||

| J1.44 | SPDIF_TX | CPU.SPDIF_TX | AF9 | NVCC_3V3 | I/O | ALT0 | SPDIF1_OUT | |

| ALT1 | PWM3_OUT | |||||||

| ALT5 | GPIO5_IO03 | |||||||

| J1.46 | SAI3_MCLK | CPU.SAI3_MCLK | AD6 | NVCC_3V3 | I/O | ALT0 | SAI3_MCLK | |

| ALT1 | PWM4_OUT | |||||||

| ALT2 | SAI5_MCLK

(Configure register IOMUXC_SAI5_MCLK_SELECT_INPUT for mode ALT2) | |||||||

| ALT5 | GPIO5_IO02 | |||||||

| J1.48 | I2C3_SDA | CPU.I2C3_SDA | F10 | NVCC_3V3 | I/O | ALT0 | I2C3_SDA | |

| ALT1 | PWM3_OUT | |||||||

| ALT2 | GPT3_CLK | |||||||

| ALT5 | GPIO5_IO19 | |||||||

| J1.50 | SAI3_TXC | CPU.SAI3_TXC | AG6 | NVCC_3V3 | I/O | ALT0 | SAI3_TX_BCLK | |

| ALT1 | GPT1_COMPARE2 | |||||||

| ALT2 | SAI5_RX_DATA2

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_2 for mode ALT2) | |||||||

| ALT4 | UART2_TX | |||||||

| ALT5 | GPIO5_IO00 | |||||||

| J1.52 | SAI3_TXD | CPU.SAI3_TXD | AF6 | NVCC_3V3 | I/O | ALT0 | SAI3_TX_DATA0 | |

| ALT1 | GPT1_COMPARE3 | |||||||

| ALT2 | SAI5_RX_DATA3

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_3 for mode ALT2) | |||||||

| ALT5 | GPIO5_IO01 | |||||||

| J1.54 | SAI1_MCLK | CPU.SAI1_MCLK | AB18 | NVCC_3V3 | I/O | ALT0 | SAI1_MCLK | |

| ALT1 | SAI5_MCLK

(Configure register IOMUXC_SAI5_MCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | SAI1_TX_BCLK

(Configure register IOMUXC_SAI1_TX_BCLK_SELECT_INPUT for mode ALT2) | |||||||

| ALT3 | PDM_CLK | |||||||

| ALT5 | GPIO4_IO20 | |||||||

| J1.56 | DGND | DGND | - | - | G | |||

| J1.58 | SAI5_MCLK | CPU.SAI5_MCLK | AD15 | NVCC_3V3 | I/O | ALT0 | SAI5_MCLK

(Configure register IOMUXC_SAI5_MCLK_SELECT_INPUT for mode ALT0) | |

| ALT1 | SAI1_TX_BCLK

(Configure register IOMUXC_SAI1_TX_BCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT5 | GPIO3_IO25 | |||||||

| J1.60 | GPIO1_IO10 | CPU.GPIO1_IO10 | AD10 | NVCC_3V3 | I/O | Internally used for ETH PHY interrupt, do not connect | ALT0 | GPIO1_IO10 |

| ALT1 | USB1_OTG_ID | |||||||

| J1.62 | SAI5_RXFS | CPU.SAI5_RXFS | AB15 | NVCC_3V3 | I/O | ALT0 | SAI5_RX_SYNC

(Configure register IOMUXC_SAI5_RX_SYNC_SELECT_INPUT for mode ALT0) | |

| ALT1 | SAI1_TX_DATA0 | |||||||

| ALT5 | GPIO3_IO19 | |||||||

| J1.64 | SAI5_RXC | CPU.SAI5_RXC | AC15 | NVCC_3V3 | I/O | ALT0 | SAI5_RX_BCLK

(Configure register IOMUXC_SAI5_RX_BCLK_SELECT_INPUT for mode ALT0) | |

| ALT1 | SAI1_TX_DATA1 | |||||||

| ALT4 | PDM_CLK | |||||||

| ALT5 | GPIO3_IO20 | |||||||

| J1.66 | SAI2_TXC | CPU.SAI2_TXC | AD22 | NVCC_3V3 | I/O | ALT0 | SAI2_TX_BCLK | |

| ALT1 | SAI5_TX_DATA2 | |||||||

| ALT5 | GPIO4_IO25 | |||||||

| J1.68 | SAI2_TXD0 | CPU.SAI2_TXD0 | AC22 | NVCC_3V3 | I/O | ALT0 | SAI2_TX_DATA0 | |

| ALT1 | SAI5_TX_DATA3 | |||||||

| ALT5 | GPIO4_IO26 | |||||||

| J1.70 | SAI2_TXFS | CPU.SAI2_TXFS | AD23 | NVCC_3V3 | I/O | ALT0 | SAI2_TX_SYNC | |

| ALT1 | SAI5_TX_DATA1 | |||||||

| ALT3 | SAI2_TX_DATA1 | |||||||

| ALT4 | UART1_CTS_B | |||||||

| ALT5 | GPIO4_IO24 | |||||||

| J1.72 | SAI2_RXD0 | CPU.SAI2_RXD0 | AC24 | NVCC_3V3 | I/O | ALT0 | SAI2_RX_DATA0 | |

| ALT1 | SAI5_TX_DATA0 | |||||||

| ALT4 | UART1_RTS_B

(Configure register IOMUXC_UART1_RTS_B_SELECT_INPUT for mode ALT4) | |||||||

| ALT5 | GPIO4_IO23 | |||||||

| J1.74 | I2C4_SDA | CPU.I2C4_SDA | E13 | NVCC_3V3 | I/O | ALT0 | I2C4_SDA | |

| ALT1 | PWM1_OUT | |||||||

| ALT5 | GPIO5_IO21 | |||||||

| J1.76 | I2C4_SCL | CPU.I2C4_SCL | D13 | NVCC_3V3 | I/O | ALT0 | I2C4_SCL | |

| ALT1 | PWM2_OUT | |||||||

| ALT5 | GPIO5_IO20 | |||||||

| J1.78 | SAI5_RXD2 | CPU.SAI5_RXD2 | AD13 | NVCC_3V3 | I/O | ALT0 | SAI5_RX_DATA2

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_2 for mode ALT0) | |

| ALT1 | SAI1_TX_DATA4 | |||||||

| ALT2 | SAI1_TX_SYNC

(Configure register IOMUXC_SAI1_TX_SYNC_SELECT_INPUT for mode ALT2) | |||||||

| ALT3 | SAI5_TX_BCLK

(Configure register IOMUXC_SAI5_TX_BCLK_SELECT_INPUT for mode ALT3) | |||||||

| ALT4 | PDM_BIT_STREAM2

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_2 for mode ALT4) | |||||||

| ALT5 | GPIO3_IO23 | |||||||

| J1.80 | SAI5_RXD3 | CPU.SAI5_RXD3 | AC13 | NVCC_3V3 | I/O | ALT0 | SAI5_RX_DATA3

(Configure register IOMUXC_SAI5_RX_DATA_SELECT_INPUT_3 for mode ALT0) | |

| ALT1 | SAI1_TX_DATA5 | |||||||

| ALT2 | SAI1_TX_SYNC

(Configure register IOMUXC_SAI1_TX_SYNC_SELECT_INPUT for mode ALT2) | |||||||

| ALT3 | SAI5_TX_DATA0 | |||||||

| ALT4 | PDM_BIT_STREAM3

(Configure register IOMUXC_PDM_BIT_STREAM_SELECT_INPUT_3 for mode ALT4) | |||||||

| ALT5 | GPIO3_IO24 | |||||||

| J1.82 | DGND | DGND | - | - | G | |||

| J1.84 | ||||||||

| J1.86 | ||||||||

| J1.88 | CLKIN1 | CPU.CLKIN1 | H27 | NVCC_3V3 | I | |||

| J1.90 | CLKIN2 | CPU.CLKIN2 | J27 | NVCC_3V3 | I | |||

| J1.92 | ||||||||

| J1.94 | ||||||||

| J1.96 | ||||||||

| J1.98 | ||||||||

| J1.100 | DGND | DGND | - | - | G | |||

| J1.102 | CSI_P1_CKN | CPU.MIPI_CSI_CLK_N | A16 | - | D | |||

| J1.104 | CSI_P1_CKP | CPU.MIPI_CSI_CLK_P | B16 | - | D | |||

| J1.106 | CSI_P1_DN0 | CPU.MIPI_CSI_D0_N | A14 | - | D | |||

| J1.108 | CSI_P1_DP0 | CPU.MIPI_CSI_D0_P | B14 | - | D | |||

| J1.110 | CSI_P1_DN1 | CPU.MIPI_CSI_D1_N | A15 | - | D | |||

| J1.112 | CSI_P1_DP1 | CPU.MIPI_CSI_D1_P | B15 | - | D | |||

| J1.114 | CSI_P1_DN2 | CPU.MIPI_CSI_D2_N | A17 | - | D | |||

| J1.116 | CSI_P1_DP2 | CPU.MIPI_CSI_D2_P | B17 | - | D | |||

| J1.118 | CSI_P1_DN3 | CPU.MIPI_CSI_D3_N | A18 | - | D | |||

| J1.120 | CSI_P1_DP3 | CPU.MIPI_CSI_D3_P | B18 | - | D | |||

| J1.122 | DGND | DGND | - | - | G | |||

| J1.124

(NAND on board) |

NAND_DQS | CPU.NAND_DQS | R22 | NVCC_3V3 | I/O | Internally used for NAND, do not connect | ||

| J1.124

(eMMC on board) |

NAND_DQS | CPU.NAND_DQS | R22 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DQS | |

| ALT1 | QSPI_A_DQS | |||||||

| ALT5 | GPIO3_IO14 | |||||||

| J1.126

(NAND on board) |

NAND_ALE | CPU.NAND_ALE | N22 | NVCC_3V3 | I/O | Internally used for NAND, do not connect | ||

| J1.126

(eMMC on board) |

NAND_ALE | CPU.NAND_ALE | N22 | NVCC_3V3 | I/O | ALT0 | RAWNAND_ALE | |

| ALT1 | QSPI_A_SCLK | |||||||

| ALT5 | GPIO3_IO00 | |||||||

| J1.128

(NAND on board) |

SD1_CLK | CPU.SD1_CLK | V26 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_CLK | |

| ALT5 | GPIO2_IO00 | |||||||

| J1.128

(eMMC on board) |

NAND_CE0_B | CPU.NAND_CE0_B | N24 | NVCC_3V3 | I/O | ALT0 | RAWNAND_CE0_B | |

| ALT1 | QSPI_A_SS0_B | |||||||

| ALT5 | GPIO3_IO01 | |||||||

| J1.130

(NAND on board) |

SD1_CMD | CPU.SD1_CMD | V27 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_CMD | |

| ALT5 | GPIO2_IO01 | |||||||

| J1.130

(eMMC on board) |

NAND_CE1_B | CPU.NAND_CE1_B | P27 | NVCC_3V3 | I/O | ALT0 | RAWNAND_CE1_B | |

| ALT1 | QSPI_A_SS1_B | |||||||

| ALT2 | USDHC3_STROBE | |||||||

| ALT5 | GPIO3_IO02 | |||||||

| J1.132

(NAND on board) |

SD1_RST_B | CPU.SD1_RST_B | R23 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_RESET_B | |

| ALT5 | GPIO2_IO10 | |||||||

| J1.132

(eMMC on board) |

NAND_CE2_B | CPU.NAND_CE2_B | M27 | NVCC_3V3 | I/O | ALT0 | RAWNAND_CE2_B | |

| ALT1 | QSPI_B_SS0_B | |||||||

| ALT2 | USDHC3_DATA5 | |||||||

| ALT5 | GPIO3_IO03 | |||||||

| J1.134

(NAND on board) |

SD1_STROBE | CPU.SD1_STROBE | R24 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_STROBE | |

| ALT5 | GPIO2_IO11 | |||||||

| J1.134

(eMMC on board) |

NAND_CE3_B | CPU.NAND_CE3_B | L27 | NVCC_3V3 | I/O | ALT0 | RAWNAND_CE3_B | |

| ALT1 | QSPI_B_SS1_B | |||||||

| ALT2 | USDHC3_DATA6 | |||||||

| ALT5 | GPIO3_IO034 | |||||||

| J1.136

(NAND on board) |

NAND_CLE | CPU.NAND_CLE | K27 | NVCC_3V3 | I/O | Internally used for NAND, do not connect | ||

| J1.136

(eMMC on board) |

NAND_CLE | CPU.NAND_CLE | K27 | NVCC_3V3 | I/O | ALT0 | RAWNAND_CLE | |

| ALT1 | QSPI_B_SCLK | |||||||

| ALT2 | USDHC3_DATA7 | |||||||

| ALT5 | GPIO3_IO05 | |||||||

| J1.138

(NAND on board) |

SD1_DATA0 | CPU.SD1_DATA0 | Y27 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA0 | |

| ALT5 | GPIO2_IO02 | |||||||

| J1.138

(eMMC on board) |

NAND_DATA00 | CPU.NAND_DATA00 | P23 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA00 | |

| ALT1 | QSPI_A_DATA0 | |||||||

| ALT5 | GPIO3_IO06 | |||||||

| J1.140

(NAND on board) |

SD1_DATA1 | CPU.SD1_DATA1 | Y26 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA1 | |

| ALT5 | GPIO2_IO0 | |||||||

| J1.140

(eMMC on board) |

NAND_DATA01 | CPU.NAND_DATA01 | K24 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA01 | |

| ALT1 | QSPI_A_DATA1 | |||||||

| ALT5 | GPIO3_IO07 | |||||||

| J1.142

(NAND on board) |

SD1_DATA2 | CPU.SD1_DATA2 | T27 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA2 | |

| ALT5 | GPIO2_IO04 | |||||||

| J1.142

(eMMC on board) |

NAND_DATA02 | CPU.NAND_DATA02 | K23 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA02 | |

| ALT1 | QSPI_A_DATA2 | |||||||

| ALT2 | USDHC3_CD_B

(Configure register IOMUXC_USDHC3_CD_B_SELECT_INPUT for mode ALT2) | |||||||

| ALT5 | GPIO3_IO08 | |||||||

| J1.144

(NAND on board) |

SD1_DATA3 | CPU.SD1_DATA3 | T26 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA3 | |

| ALT5 | GPIO2_IO05 | |||||||

| J1.144

(eMMC on board) |

NAND_DATA03 | CPU.NAND_DATA03 | N23 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA03 | |

| ALT1 | QSPI_A_DATA3 | |||||||

| ALT2 | USDHC3_WP

(Configure register IOMUXC_USDHC3_WP_SELECT_INPUT for mode ALT2) | |||||||

| ALT5 | GPIO3_IO09 | |||||||

| J1.146 | DGND | DGND | - | - | G | |||

| J1.148

(NAND on board) |

SD1_DATA4 | CPU.SD1_DATA4 | U27 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA4 | |

| ALT5 | GPIO2_IO06 | |||||||

| J1.148

(eMMC on board) |

NAND_DATA04 | CPU.NAND_DATA04 | M26 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA04 | |

| ALT1 | QSPI_B_DATA0 | |||||||

| ALT2 | USDHC3_DATA0 | |||||||

| ALT5 | GPIO3_IO10 | |||||||

| J1.150

(NAND on board) |

SD1_DATA5 | CPU.SD1_DATA5 | U26 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA5 | |

| ALT5 | GPIO2_IO07 | |||||||

| J1.150

(eMMC on board) |

NAND_DATA05 | CPU.NAND_DATA05 | L26 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA05 | |

| ALT1 | QSPI_B_DATA1 | |||||||

| ALT2 | USDHC3_DATA1 | |||||||

| ALT5 | GPIO3_IO11 | |||||||

| J1.152

(NAND on board) |

SD1_DATA6 | CPU.SD1_DATA6 | W27 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA6 | |

| ALT5 | GPIO2_IO08 | |||||||

| J1.152

(eMMC on board) |

NAND_DATA06 | CPU.NAND_DATA06 | K26 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA06 | |

| ALT1 | QSPI_B_DATA2 | |||||||

| ALT2 | USDHC3_DATA2 | |||||||

| ALT5 | GPIO3_IO12 | |||||||

| J1.154

(NAND on board) |

SD1_DATA7 | CPU.SD1_DATA7 | W26 | NVCC_3V3

(NVCC_1V8 on request) |

I/O | ALT0 | USDHC1_DATA7 | |

| ALT5 | GPIO2_IO09 | |||||||

| J1.154

(eMMC on board) |

NAND_DATA07 | CPU.NAND_DATA07 | N26 | NVCC_3V3 | I/O | ALT0 | RAWNAND_DATA07 | |

| ALT1 | QSPI_B_DATA3 | |||||||

| ALT2 | USDHC3_DATA3 | |||||||

| ALT5 | GPIO3_IO13 | |||||||

| J1.156

(NAND on board) |

NAND_RE_B | CPU.NAND_RE_B | N27 | NVCC_3V3 | I/O | Internally used for NAND, do not connect | ||

| J1.156

(eMMC on board) |

NAND_RE_B | CPU.NAND_RE_B | N27 | NVCC_3V3 | I/O | ALT0 | RAWNAND_RE_B | |

| ALT1 | QSPI_B_DQS | |||||||

| ALT2 | USDHC3_DATA4 | |||||||

| ALT5 | GPIO3_IO15 | |||||||

| J1.158

(NAND on board) |

NAND_READY_B | CPU.NAND_READY_B | P26 | NVCC_3V3 | I/O | Internally used for NAND, do not connect | ||

| J1.158

(eMMC on board) |

NAND_READY_B | CPU.NAND_READY_B | P26 | NVCC_3V3 | I/O | ALT0 | RAWNAND_READY_B | |

| ALT2 | USDHC3_RESET_B | |||||||

| ALT5 | GPIO3_IO16 | |||||||

| J1.160

(NAND on board) |

NAND_WE_B | CPU.NAND_WE_B | R26 | NVCC_3V3 | I/O | Internally used for NAND, do not connect | ||

| J1.160

(eMMC on board) |

NAND_WE_B | CPU.NAND_WE_B | R26 | NVCC_3V3 | I/O | ALT0 | RAWNAND_WE_B | |

| ALT2 | USDHC3_CLK | |||||||

| ALT5 | GPIO3_IO17 | |||||||

| J1.162

(NAND on board) |

NAND_WP_B | CPU.NAND_WP_B | R27 | NVCC_3V3 | I/O | Internally used for NAND, do not connect | ||

| J1.162

(eMMC on board) |

NAND_WP_B | CPU.NAND_WP_B | R27 | NVCC_3V3 | I/O | ALT0 | RAWNAND_WP_B | |

| ALT2 | USDHC3_CMD | |||||||

| ALT5 | GPIO3_IO18 | |||||||

| J1.164 | DGND | DGND | - | - | G | |||

| J1.166 | GPIO1_IO15 | CPU.GPIO1_IO15 | AB9 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO15 | |

| ALT1 | USB2_OTG_OC | |||||||

| ALT4 | USDHC3_WP

(Configure register IOMUXC_USDHC3_WP_SELECT_INPUT for mode ALT4) | |||||||

| ALT5 | PWM4_OUT | |||||||

| ALT6 | CCM_CLKO2 | |||||||

| J1.168 | GPIO1_IO07 | CPU.GPIO1_IO07 | AF11 | NVCC_3V3 | I/O | ALT0 | GPIO1_IO07 | |

| ALT1 | ENET1_MDIO

(Configure register IOMUXC_ENET1_MDIO_SELECT_INPUT for mode ALT1) | |||||||

| ALT5 | USDHC1_WP | |||||||

| ALT6 | CCM_EXT_CLK4 | |||||||

| J1.170 | SAI1_TXD4 | CPU.SAI1_TXD4 | AG22 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA4 |

| ALT1 | SAI6_RX_BCLK

(Configure register IOMUXC_SAI6_RX_BCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | SAI6_TX_BCLK

(Configure register IOMUXC_SAI6_TX_BCLK_SELECT_INPUT for mode ALT2) | |||||||

| ALT4 | CORESIGHT_TRACE12 | |||||||

| ALT5 | GPIO4_IO16 | |||||||

| ALT6 | SRC_BOOT_CFG12 | |||||||

| J1.172 | SAI1_TXD5 | CPU.SAI1_TXD5 | AF22 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA5 |

| ALT1 | SAI6_RX_DATA0

(Configure register IOMUXC_SAI6_RX_DATA_SELECT_INPUT_0 for mode ALT1) | |||||||

| ALT2 | SAI6_TX_DATA0 | |||||||

| ALT4 | CORESIGHT_TRACE13 | |||||||

| ALT5 | GPIO4_IO17 | |||||||

| ALT6 | SRC_BOOT_CFG13 | |||||||

| J1.174 | SAI1_TXD6 | CPU.SAI1_TXD6 | AG23 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA6 |

| ALT1 | SAI6_RX_SYNC

(Configure register IOMUXC_SAI6_RX_SYNC_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | SAI6_TX_SYNC

(Configure register IOMUXC_SAI6_TX_SYNC_SELECT_INPUT for mode ALT2) | |||||||

| ALT4 | CORESIGHT_TRACE14 | |||||||

| ALT5 | GPIO4_IO18 | |||||||

| ALT6 | SRC_BOOT_CFG14 | |||||||

| J1.176 | SAI1_TXD7 | CPU.SAI1_TXD7 | AF23 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_TX_DATA7 |

| ALT1 | SAI6_MCLK

(Configure register IOMUXC_SAI6_MCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT3 | PDM_CLK | |||||||

| ALT4 | CORESIGHT_TRACE15 | |||||||

| ALT5 | GPIO4_IO19 | |||||||

| ALT6 | SRC_BOOT_CFG15 | |||||||

| J1.178 | SAI1_RXD7 | CPU.SAI1_RXD7 | AF19 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA7 |

| ALT1 | SAI6_MCLK

(Configure register IOMUXC_SAI6_MCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | SAI1_TX_SYNC

(Configure register IOMUXC_SAI1_TX_SYNC_SELECT_INPUT for mode ALT2) | |||||||

| ALT3 | SAI1_TX_DATA4 | |||||||

| ALT4 | CORESIGHT_TRACE7 | |||||||

| ALT5 | GPIO4_IO09 | |||||||

| ALT6 | SRC_BOOT_CFG7 | |||||||

| J1.180 | SAI1_RXD6 | CPU.SAI1_RXD6 | AG19 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA6 |

| ALT1 | SAI6_TX_SYNC

(Configure register IOMUXC_SAI6_TX_SYNC_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | SAI6_RX_SYNC

(Configure register IOMUXC_SAI6_RX_SYNC_SELECT_INPUT for mode ALT2) | |||||||

| ALT4 | CORESIGHT_TRACE6 | |||||||

| ALT5 | GPIO4_IO08 | |||||||

| ALT6 | SRC_BOOT_CFG6 | |||||||

| J1.182 | SAI1_RXD5 | CPU.SAI1_RXD5 | AF18 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA5 |

| ALT1 | SAI6_TX_DATA0 | |||||||

| ALT2 | SAI6_RX_DATA0

(Configure register IOMUXC_SAI6_RX_DATA_SELECT_INPUT_0 for mode ALT2) | |||||||

| ALT3 | SAI1_RX_SYNC

(Configure register IOMUXC_SAI1_RX_SYNC_SELECT_INPUT for mode ALT3) | |||||||

| ALT4 | CORESIGHT_TRACE5 | |||||||

| ALT5 | GPIO4_IO07 | |||||||

| ALT6 | SRC_BOOT_CFG | |||||||

| J1.184 | SAI1_RXD4 | CPU.SAI1_RXD4 | AG18 | NVCC_3V3 | I/O | Internally used for BOOT mode configuration:

can be pulled-up or down depending on |

ALT0 | SAI1_RX_DATA4 |

| ALT1 | SAI1_RX_DATA4

(Configure register IOMUXC_SAI6_TX_BCLK_SELECT_INPUT for mode ALT1) | |||||||

| ALT2 | SAI6_RX_BCLK

(Configure register IOMUXC_SAI6_RX_BCLK_SELECT_INPUT for mode ALT2) | |||||||

| ALT4 | CORESIGHT_TRACE4 | |||||||

| ALT5 | GPIO4_IO06 | |||||||

| ALT6 | SRC_BOOT_CFG4 | |||||||

| J1.186 | USB1_VBUS | CPU.USB1_VBUS | F22 | S | Connected with 30K resistor on SOM.

See IMX8MM datasheet for 5V tolerance info. |

|||

| J1.188 | USB2_VBUS | CPU.USB2_VBUS | F23 | S | Connected with 30K resistor on SOM.

See IMX8MM datasheet for 5V tolerance info. |

|||

| J1.190 | DGND | DGND | - | - | G | |||

| J1.192 | USB1_ID | CPU.USB1_ID | D22 | VDDA_1V8 | I | |||

| J1.194 | USB2_ID | CPU.USB2_ID | D23 | VDDA_1V8 | I | |||

| J1.196 | USB1_DN | CPU.USB1_DN | A22 | - | D | |||

| J1.198 | USB1_DP | CPU.USB1_DP | B22 | - | D | |||

| J1.200 | USB2_DP | CPU.USB2_DP | B23 | - | D | |||

| J1.202 | USB2_DN | CPU.USB2_DN | A23 | - | D | |||

| J1.204 | DGND | DGND | - | - | G | |||